## Readout Electronics for Silicon Micro-Strip Sensors

O. Alonso<sup>1</sup>, <u>N. Franch<sup>1</sup></u>, J. Canals<sup>1</sup>, M. López<sup>1</sup>, A. Herms<sup>1</sup>, A. Diéguez<sup>1</sup>, M. Carulla<sup>2</sup>, D. Flores<sup>2</sup>, S. Hidalgo<sup>2</sup>, A. Merlos<sup>2</sup>, G. Pellegrini <sup>2</sup>, D. Quirion<sup>2</sup>, J. González<sup>3</sup>, R. Jaramillo<sup>3</sup>, M. Fernández<sup>3</sup>, I. Vila<sup>3</sup>, R. Millán<sup>4</sup>, F.R. Palomo<sup>4</sup>

<sup>1</sup>SIC – Engineering Department: Electronics – Universitat de Barcelona

<sup>2</sup>Centro Nacional de Microelectrónica (IMB-CNM-CSIC)

<sup>3</sup>Instituto de Física de Cantabria (CSIC-UC)

<sup>4</sup>Escuela Técnica Superior de Ingeniería, Universidad de Sevilla

Silicon micro-strips detectors are the baseline for the tracker region of the future International Linear Collider (ILC). Lately, variations of this type of sensors, like resistive micro-strips, Low Gain Avalanche Detectors (LGAD) and inverse LGAD (iLGAD) [1], have been presented to be considered as the technology for the future tracker.

Strip W

P<sup>+</sup> Strip P<sup>+</sup> Strip

D+ S

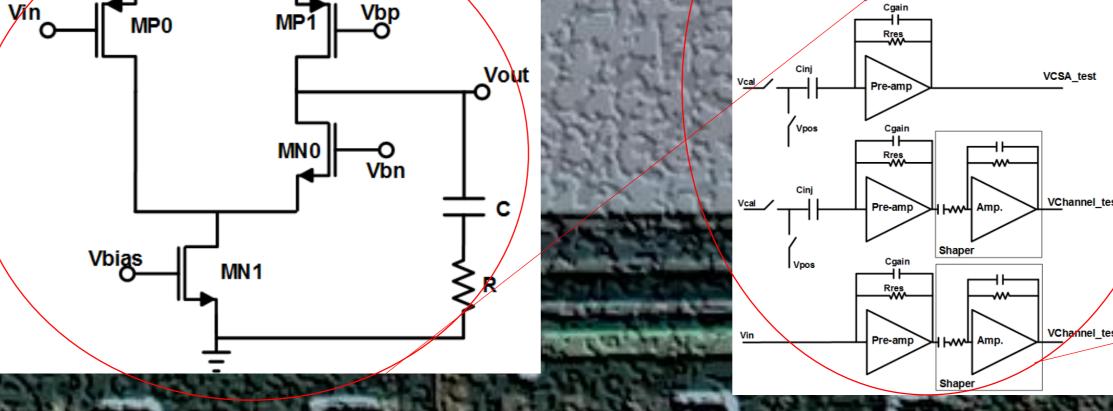

ASIC fabricated in 180 nm CMOS technology from AMS with the very front-end electronics used to readout silicon micro-strips is presented as well as its experimental results. The front-end has the typical architecture for Si-strip readout [2], i.e., preamplification stage with a Charge Sensitive Amplifier (CSA) followed by a CR-RC shaper. Both amplifiers are based on a folded cascade structure with a PMOS input transistor and the shaper only uses passive elements for the feedback stage. The CSA has programmable gain and a configurable input stage in order to adapt to the different strip flavours (resistive micro-strips, LGADs and iLGADs). The fabricated prototype is 0.865 mm x 0.965 mm and includes the biasing circuit for the CSA and the shaper, 4 analog channels (CSA+shaper) and programmable charge injection circuits included for testing purposes.

- Power supply: 1.8 V

Power consumption x channel < 160 uW</li>

Pre-amp is the main noise contribution of the circuit.

QVDD

## Gain ~ 67,5 dB GBW ~ 19,5 MHz PM ~ 63°

Optimum L and Ibias to maintain ENC below 400 e- with a C<sub>d</sub> of 20 pF

CSA with two gains (100fC, 500fC)

CR-RC shaper with a folded cascade structure. C's and R's are passive

ASIC:

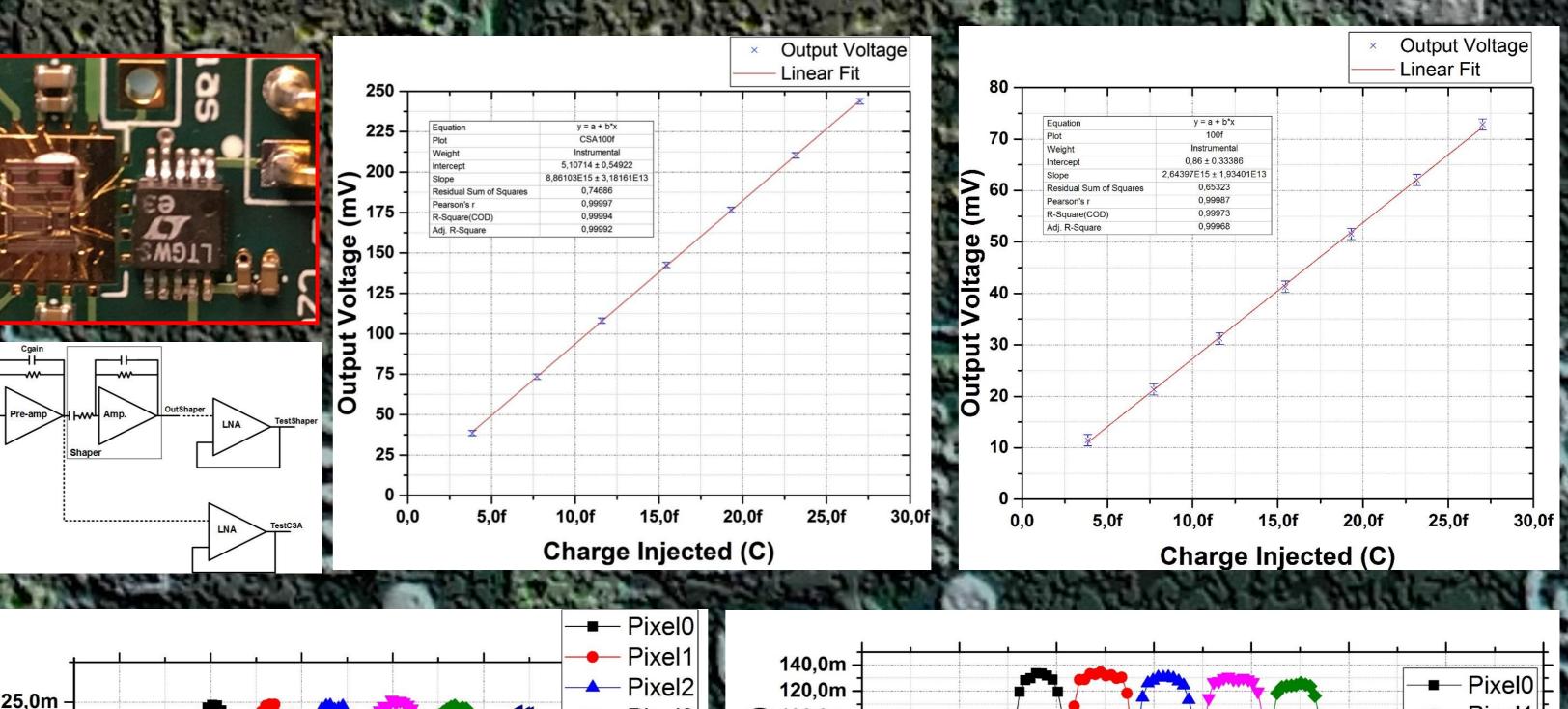

CSA gain of 8.86 mV/fC with feedback C = 100f

Channelgain of 2.64 mV/fC with feedback C = 100f

Vrms noise = 0.73 mV

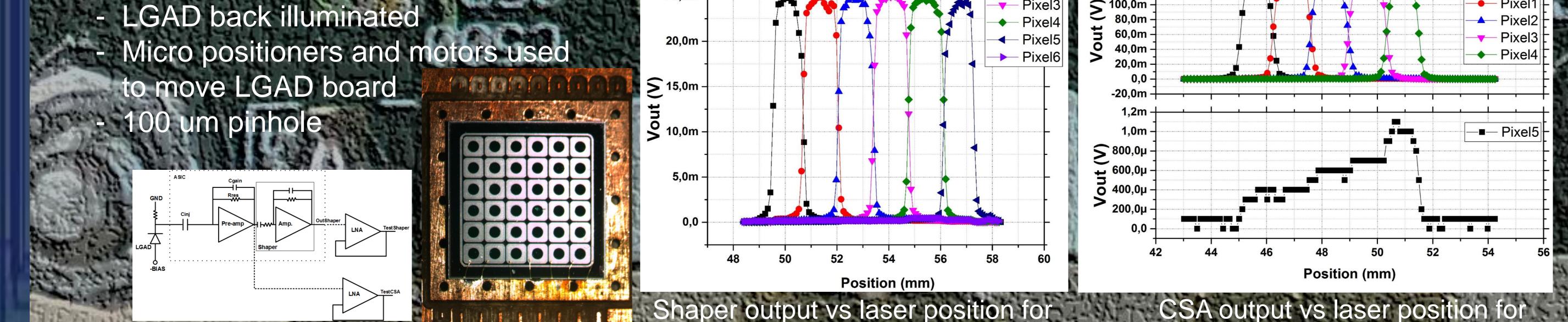

Pixelated LGAD + ASIC:- LGAD biased @ 420 V

each pixel

each pixel. Pixel 5 covered.

[1] G. Pellegrini et al., "Recent Technological Developments on LGAD and iLGAD Detectors for Tracking and Timing Applications", Instrumentation and detectors, arXiv:1511.07175.

[2] F. Anghinolfi et al., in: IEEE Transaction on nuclear science, vol. 49, nº 3, pp.1080-1085, 2002

Vork done in the framework of the RD50 CERN collaboration and the Spanish national projects FPA2013-48387 and

UNIVERSITAT DE BARCELONA