# High-Speed Serial Optical Link Test Bench Using FPGA with Embedded Transceivers

Annie C. Xiang<sup>1</sup>, Datao Gong<sup>1</sup>, Suen Hou<sup>2</sup>, Chonghan Liu<sup>1</sup>, Tiankuan Liu<sup>1</sup>, Da-Shung Su<sup>2</sup>, Ping-Kun Teng<sup>2</sup>, Jingbo Ye<sup>1</sup>, <sup>1</sup> Department of Physics, Southern Methodist University, Dallas TX 75275, U.S.A. <sup>2</sup> Institute of Physics, Academia Sinica, Nangang 11529, Taipei, Taiwan

cxiang@smu.edu

#### Introduction

#### Test Bench

Serial optical data transmission provides a solution to High Energy Physics experiments' readout systems with high bandwidth, low power, low mass and small footprint. It is widely proposed to be used in detector upgrades for SLHC. Commercial FPGAs with embedded multi-gigabit transceivers have become readily accessible. Altera's Stratix II GX family and Xilinx's Virtex 5 FXT family offer comprehensive data interface designs that operate up to 6.5Gbps. And the newest Stratix IV GX and Virtex 6 push the serial transceiver rate up to 10Gbps.

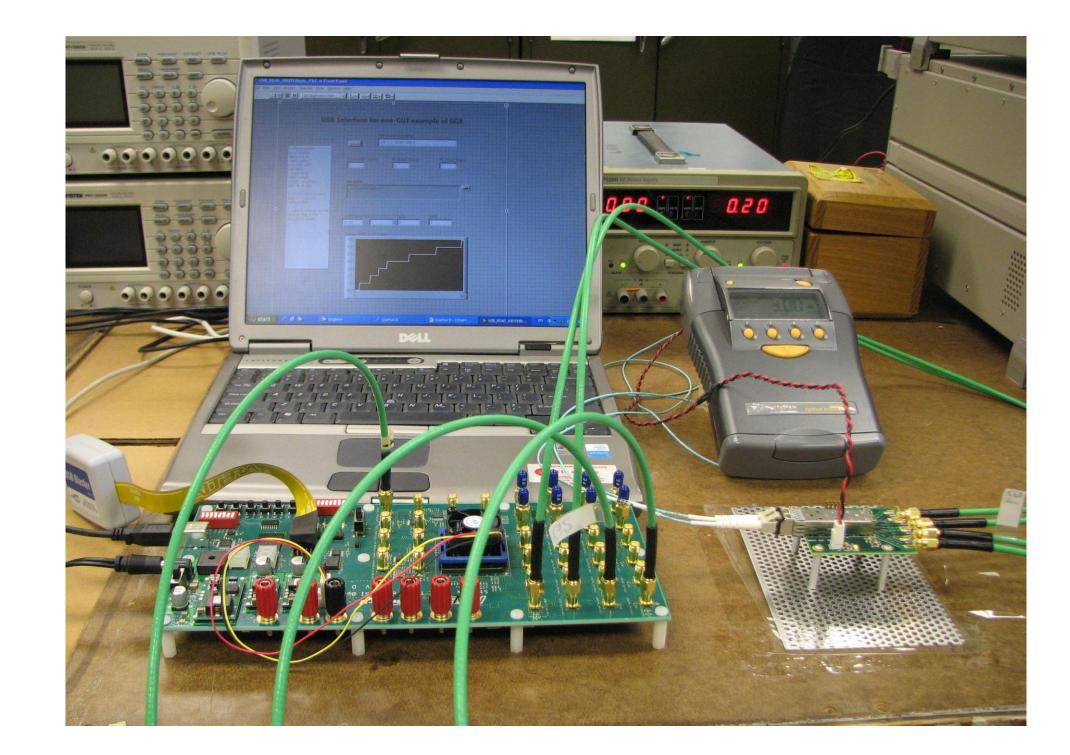

We develop a test bench based on Altera' s Stratix II GX Transceiver SI Development kit. Demonstrate it on a Point-2-Point serial optical link. And compare it with a stand alone Bit Error Rate Tester. 8b/10b protocol is implemented and its effects studied. Single bit flip will affect two code-groups and results in multiple errors detected. Word error is a more accurate measure in this scenario.

## Signal Integrity

- Above eye diagram shows the near-end transmitter output of a common configuration: 5Gbps serial data rate, 800 mV differential voltage, no pre-emphasis, PRBS-7 data pattern at room temperature.

- Electrical signal loopback is error free for three days.

- Transmitter rise/fall time, jitter output, jitter transfer and receiver jitter tolerance data are available for link budget planning.

## Characteristic

#### Embedded Transceiver

#### **Basic BER**

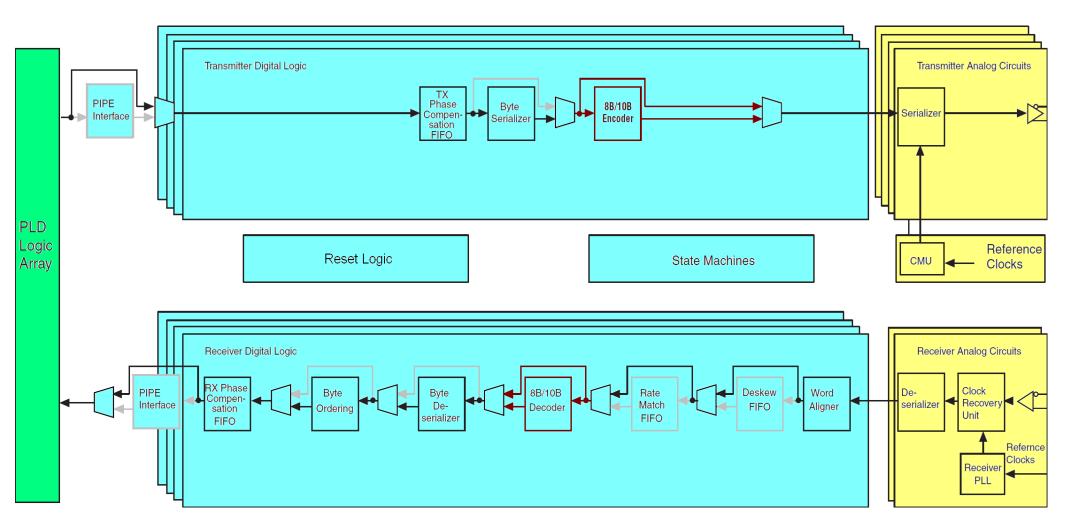

- The Stratix II GX transceiver is configured in basic mode. Dynamic reconfiguration supports switching of analog setting at run-time.

- Double widths data path is used to support data rate over 3.125Gbps. And byte serializer is needed to allow FPGA core to run at adequate frequency.

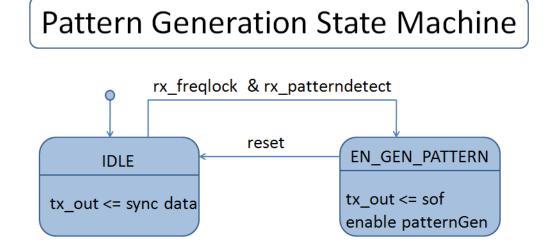

- The word aligner detects word patterns, aligns word boundaries and signals synchronization. Then the bit error rate test is enabled.

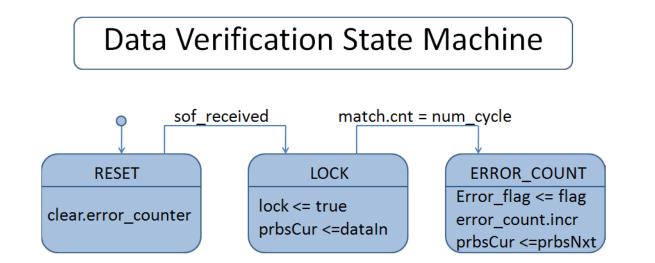

- A pseudo-random binary sequence (PRBS) generator and checker is implemented for the bit error rate test. Test pattern is implemented in polynomial shifters.

- The error checker uses the incoming data as seed to generated expected output pattern, until pattern match is declared. The checker then switches to internal seed.

- PC user interface through USB is coded in LabVIEW to enable feature settings and data analysis settings .

- A variable optical attenuator is inserted in the fiber loop to induce transmission degradation.

- mode with and without 8b/10b coding.

- When 8B/10B is not used, data bus on PLD side is 40 bit wide. When 8B/10B is used, data bus on PLD side is 32 bit wide.

- Basic clock of 156.25MHz is enabled to generate serial references.

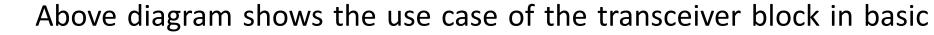

- The above error rate measurement compares results of the FPBA BERT and than of a commercial BERT. It also shows that there are more 1 to 0 bit flip than 0 to 1 bit flip at lower error rate in this degradation scenario.

# PatternGen & ErrorChk

| log: 2009/09/10 16: |       |                                                 |    | click to insert time bar |    |  |       |   |    |   |   |  |   |   |           |   |    |    |    |    |    |    |    |    |    |

|---------------------|-------|-------------------------------------------------|----|--------------------------|----|--|-------|---|----|---|---|--|---|---|-----------|---|----|----|----|----|----|----|----|----|----|

| Туре                | Alias | Name                                            | -8 | -7                       | -6 |  | -5 -3 | 3 | -2 | - | Û |  | 1 | 7 | 8         | 9 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 |

| $\odot$             |       | data_Generators_and_Checkers checker_synced     |    |                          |    |  |       |   |    |   |   |  |   |   |           |   |    |    |    |    |    |    |    |    |    |

| ۲                   |       | data_Generators_and_Checkers enable_mux         |    |                          |    |  |       |   |    |   |   |  |   |   |           |   |    |    |    |    |    |    |    |    |    |

| $\odot$             |       | data_Generators_and_Checkers rx_enapatternalign |    |                          |    |  |       |   |    |   | Ì |  |   |   |           |   |    |    |    |    |    |    |    |    |    |

| ۲                   |       | data_Generators_and_Checkers rx_freqlocked      |    |                          |    |  |       |   |    |   | - |  |   |   |           |   |    |    |    |    |    |    |    |    |    |

| ٥                   |       |                                                 | 0  | h X                      |    |  |       |   |    |   | Ì |  |   |   |           |   |    |    |    |    | Oh |    |    |    |    |

| ٥                   |       |                                                 |    |                          |    |  |       |   |    |   | 1 |  | • | 0 | 000000000 | າ |    |    |    |    |    |    |    |    |    |

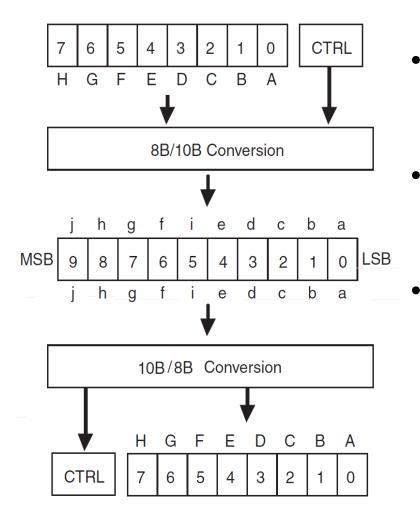

The 8B/10B coding is used by many protocols such as Fiber Channel, Gigabit Ethernet, PCIe and XAUI. The 8B/10B coding algorithm achieves: DC balanced data stream; Sufficient level transitions; Unique code groups Stratix II GX devices support two dedicated 8B/10B encoders in each transceiver channels. It works in cascade mode and complements the word aligner to achieve boundary synchronization.

| Stroom                     |    | Code-grou | ıp                           | Code-g   | roup   | Code-group            |        |  |  |

|----------------------------|----|-----------|------------------------------|----------|--------|-----------------------|--------|--|--|

| Stream                     | RD | RD        | RD                           | RD       | RD     | RD                    | RD     |  |  |

| Transmitted code-<br>group | _  | D21.1     | _                            | D10.2    | _      | D23.5                 | +      |  |  |

| Transmitted bit stream     | _  | 101010 -  | 1001 -                       | 010101 - | 0101 - | 111010 +              | 1010 + |  |  |

| Received bit stream        | _  | 101010 -  | 10 <b>1</b> 1 <sup>a</sup> + | 010101 + | 0101 + | 111010 + <sup>b</sup> | 1010 + |  |  |

#### 1E-01 🗕 8b/10b bit error 8b/10b word error 1E-02 🗕 8b/10b total word error 1E-03bit error no 8b/10b 1E-04 പ1E-05ос 1E-06 Ю 1E-07-Ш 1E-08 1E-09 1E-10-1E-11 1E-12--17 -22 -20 -16 -15 -23 -21 -19 -18 OMA (dBm)

- In 8B/10B coded transmission, a single bit flip in the serial data stream may affect two code-groups as exampled in the table on the left.

- The propagation of errors is eventually prevented by nonzero disparity blocks. Although the delay is uncertain depending on transmitted data.

- When a code/disparity violation is detected, the decoder output is not valid. Hence it makes more sense to count word errors instead of bit errors.

#### 8B/10B

#### Word Error

| Ð                       | ⊞- doits:Generators_and_Checkers rx_data_in_xcvr | X    | 00555555BCh X |             |   |  |             | 00AEEFABCDh X |  | Χ | Χ | X) | () | (     |        |

|-------------------------|--------------------------------------------------|------|---------------|-------------|---|--|-------------|---------------|--|---|---|----|----|-------|--------|

| $\bigcirc$              | ⊕- doits:Generators_and_Checkersttx_out_xcvr     |      | 00555555BCh   | 00AEEFABCDh | X |  | 00FC0830A3h |               |  |   | ( | Χ  |    | 00D2E | FREEFL |

| $\overline{\mathbf{O}}$ |                                                  | Oh X |               |             | 1 |  | Fh          |               |  |   |   |    |    |       |        |

| Received code-group | _ | D21.0 | + | D10.2 | + invalid code-group <sup>b</sup> + <sup>c</sup> |

|---------------------|---|-------|---|-------|--------------------------------------------------|

• The above error rate measurement shows that more word errors were detected than bit errors when the 8b/10b transmission degrades. It also confirms that 8b/10b error rate is confined and not much worse than none coded transmission.

| _         |    | •    |   |  |

|-----------|----|------|---|--|

| <b>FX</b> | na | nsi  | n |  |

|           | pu | 1131 |   |  |

#### Summary

- Additional features of error logging is developed and will be used to investigate timing distribution of erroneous events during link degradation.

- At higher data rate, 64B/66B coding is preferred and will be implemented in place of 8B/10B coding.

- A high-speed serial optical link test bench using FPGA with embedded transceiver is demonstrated. This test bench is proposed to characterize physical layer components and to verify link bit error performance.

- The test bench consists of a PRBS generator and detector, implements on Altera's Stratix II GX development kit, with configurable embedded transceiver and provides PC LabVIEW interface for automation and control.

- 8B/10B protocol is implemented and studied. Although bit error can spread into multiple code groups, word error rate is contained by disparity blocks.

The SMU group acknowledge the US-ATLAS R&D program for the upgrade of the LHC, and the US Department of Energy grant DE-FG02-04ER41299.

The authors acknowledge Drs. Francois Vasey, Jan Torska and Paschalis Vichoudis at CERN for beneficial discussions.

Acknowledgement