# Characterisation of 2nd generation flex cables

Nadim Conti

On behalf of INFN - Sezione di Milano

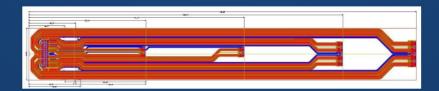

# Second generation flex cable changelog

Technology: Full-flex + stiffener design

- Stack-up: Two double cores

- Traces with/space adjusted in the inner layers to keep Zdiff ~ 100 Ohm

- Power traces width increased from 4 mm to 6-7 mm

- Digital and analog power traces maintained just in case

- Central symmetry maintained

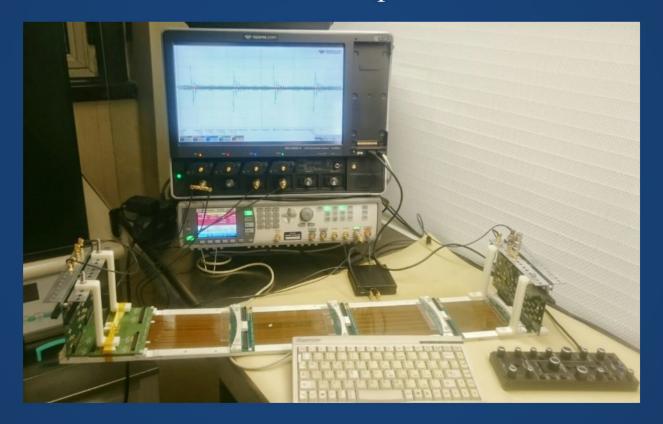

# Test setup

### Test setup

- Milli-Ohmeter for precise Resistance and DC measurement

- Sampling oscilloscope with dual channel TDR module for trace impedance characterization

- Digital signal analyzer for signal integrity measurement + low jitter PRBS generator

- Passive board provided by Maryland

# Digital power lines resistance measurements (one way)

| Flex position | Current [A] | Resistance [mOhm] |  |

|---------------|-------------|-------------------|--|

| P1            | 3           | 114±3             |  |

| P2            | 1           | 101±2             |  |

| Р3            | 1           | 84±1              |  |

| P4            | 1           | 41±1              |  |

#### Power lines resistance measurements (one way)

- A single via (0.6x0.3mm) can withstand at least up to 3A

- We have consistency between AnSys SiWave simulations and our measurements, achieving a maximum of 6% deviation 1.5% on average.

# Differential pairs resistance measurements

| Dataflex position | Resistance @10mA<br>[Ohm] | Resistance @20mA<br>[Ohm] | Layer |

|-------------------|---------------------------|---------------------------|-------|

| P1                | 5.211±0.09                | 5.224±0.10                | Тор   |

| P1                | 7.751±0.12                | 7.767±0.12                | Inner |

By climbing from 10 to 20mA we consistently get an increase of 20mOhm ca.

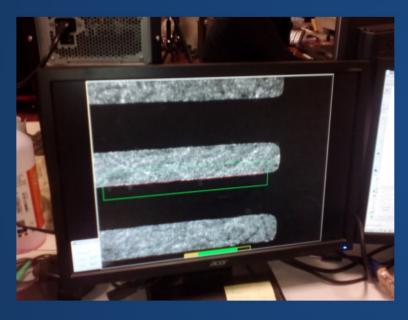

### Differential pairs resistance measurements

- CERN confirmed top-layer lines to be thicker than expected (30um, originally 22.5um)

- After an optical inspection we have also found them to be thinner (90um, designed to be 115um)

- Section area ratio is consistent with resistance measurements and symulations

To do: flex micro-sectioning to analyze traces geometry & multiple samples

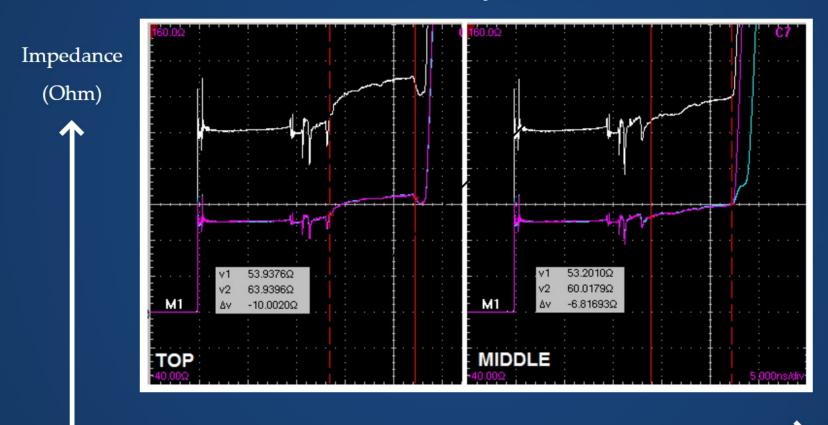

# Time Domain Reflectomery (TDR) Measurements

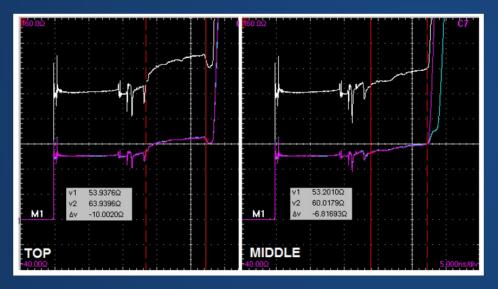

#### Time Domain Reflectomery (TDR) Measurements

- P2, P3 and P4 behave like P1

- 6 Ohms slope in both layers

- Reflections are probably smoothing the graph

- We can't extract the "line model" yet

- Top-Middle differences are resembling what we're supposing the flex section to be

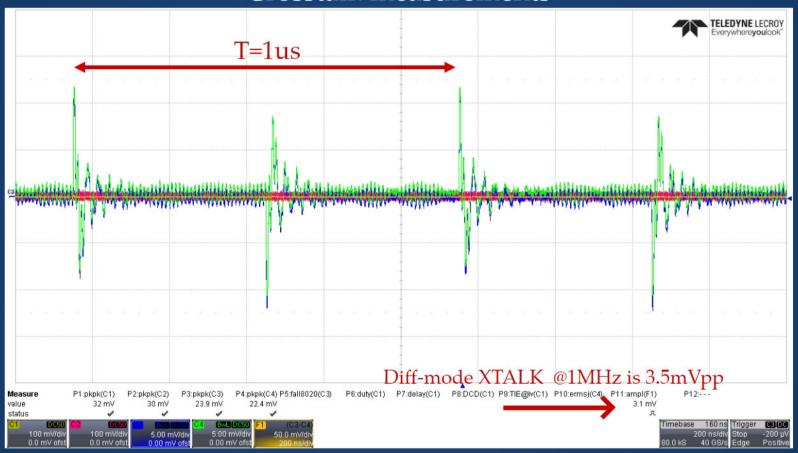

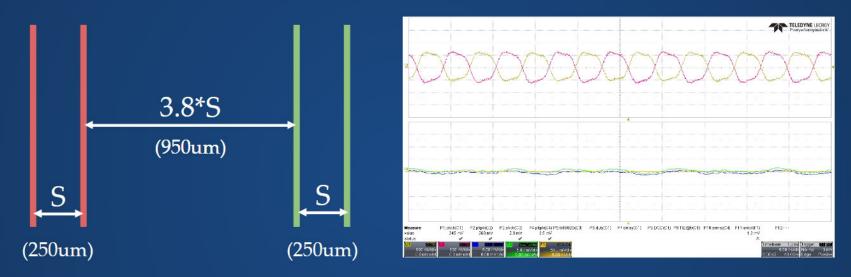

#### Crosstalk measurements

#### Crosstalk measurements

We have measured FEXT in every combination (top-middle, top-top, middle-middle)

@10MHz & @160MHz we consistently have about 1% Far End Cross-Talk

(In theory it should be around 0.8%)

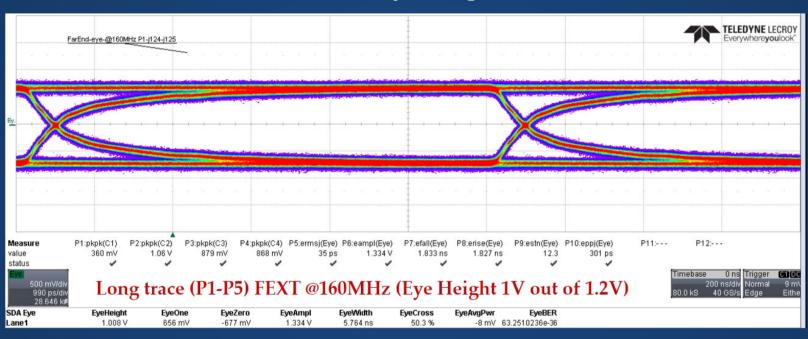

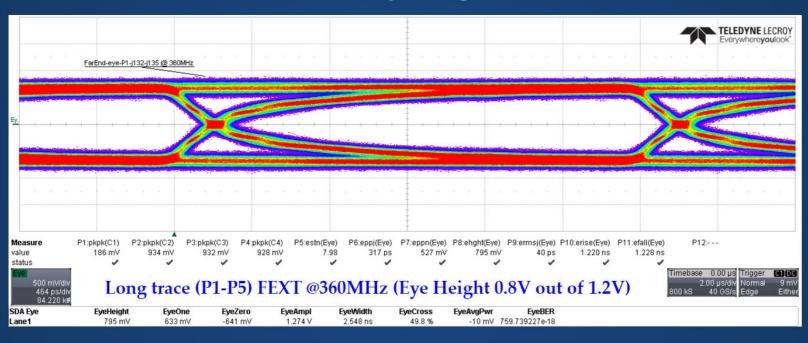

### Far-end eye diagrams

Eye wide open @160MHz, S/N>10 and jitter(RMS) around 36ps (12ps due to the setup)

### Far-end eye diagrams

The Eye is still open @360MHz but then the S/N goes below 8, jitter(RMS)=40ps

#### Summary

- Resistance expectations achieved, flexes are fully working with promising results

- We still have to consolidate the production line to achieve the best impedance matching

- HV distribution will be tested soon

- We can trust Ansys and Hyperlinx simulations for further development of flexes

- We have consistent measurements between different flexes (made with the same process)

- Via behaviour will be analyzed by routing a few via-chains in the future release

- Extensive testing setup is still in discussion