# Summary of Work Package 8-Power distribution

Marc Weber

- Pace of power distribution R&D remains very high

- Lot's of progress, but technical challenges are huge (only a fraction of results can be mentioned)

LARGE HADRON COLLIDER UPGRADE

- Healthy competition between serial powering and DC-DC conversion

- Good communication, many informal meetings, free exchange of information between WP8 members and wider powering community

- Many in depth talks on next Tuesday within ACES 2009

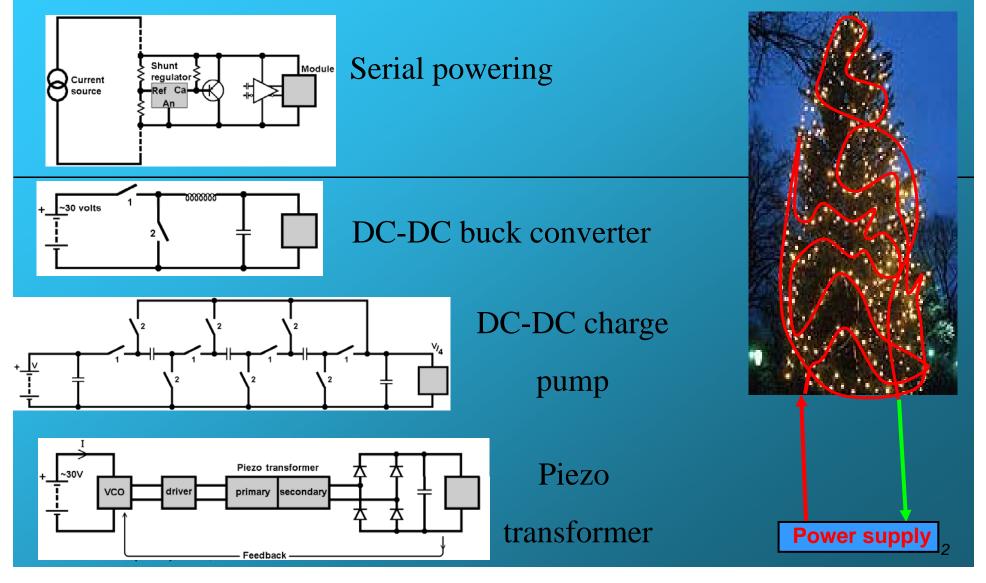

### How to get the power in ?

a) "recycling" of current (SP) oder b) "high-voltage power transmission (DC-DC)

### Some highlights of DC-DC conversion R&D

- Progress on radiation-hard technologies

- Lot's of progress on **DC-DC topology choices** and **converter design**

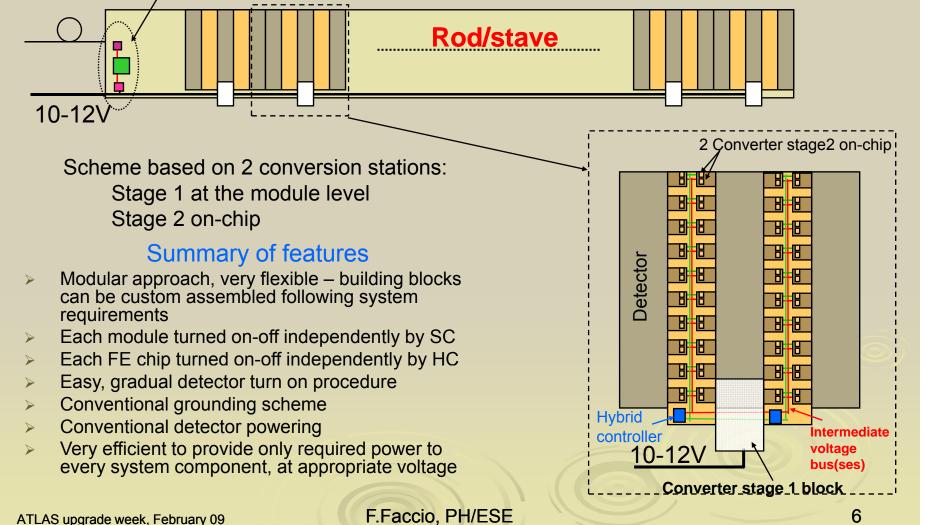

- Convergence on **Two-stage conversion scheme**

- Custom air-coil inductors with PCB technology

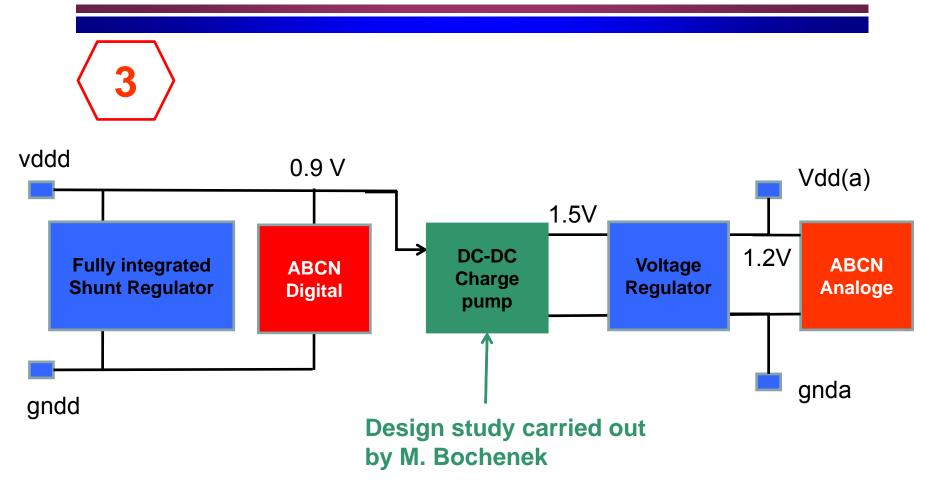

- Integrated DC-DC charge pumps

- Wealth of **test results with large-scale silicon detectors**

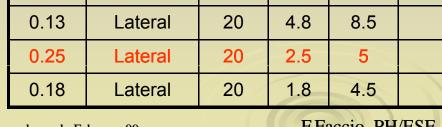

# Semiconductor technology (1)

- The converter requires the use of a technology offering both low-voltage and high-voltage (15-20V) transistors

- Properties of high-voltage transistors largely determine converter's performance

- Need for small Ron, and small gate capacitance (especially Cgd) for given Ron!

Vqs

3.5

3.5

5.5

(V)

Tox

(nm)

7

7

12

Survey of available options covered 5 technologies  $\geq$

Trans type

Lateral

Vertical

Lateral

Best results with 0.25um SGB25V GOD technology from IHP

Max

Vds

(V)

14

80

20

ATLAS upgrade week, February 09

Tech

Node

(um)

0.35

0.18

F.Faccio, PH/ESE

Ron\*um

(kOhm\*um)

8

33

4.75

7

4-5

9.3

Status

Tested

Tested

Tested

Tested

First MPW April 09

Prototype in 0.35µm

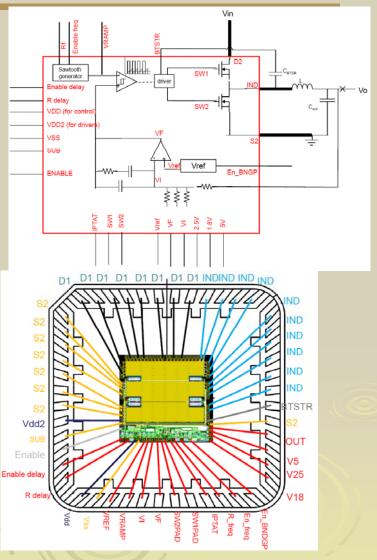

### ASIC development – 2<sup>nd</sup> generation

- Second generation prototype

- > Still manufactured in AMIS 0.35µm

#### > Features:

- VIN and Power Rail Operation from +3.3V to +12V

- Selectable output voltage (nominal 2.5V)

- Maximum output current: 3A

- Fast Transient Response 0 to 100% Duty Cycle

- 14MHz Bandwidth Error Amplifier with 10V/µs Slew Rate

- Internal oscillator fixed at 1Mhz, programmable from 400kHz to 3MHz with external resistor

- Internal voltage reference (nominally (1.2V)

- Remote Voltage Sensing with Unity Gain

- Programmable delay between gate signals

- Integrated feedback loop with bandwidth of 20Khz

- Submitted December 08, expected back in April 09

- Mounted in 7x7mm QFN package

- Third generation will be in the IHP 0.25µm technology

- > It will be a simple buck

- Refined comparison with 2-phase interleaved with V-divider (alternative topology), using also prototypes, has indicated little advantage of this latter topology at the small load currents foreseen for a module

ATLAS upgrade week, February 09

F.Faccio, PH/ESE

## Proposed distribution scheme (ATLAS Short Strip concept)

Voltage for SC and optoelectronics generated locally by a converter stage 1

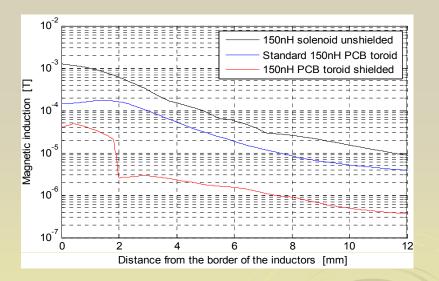

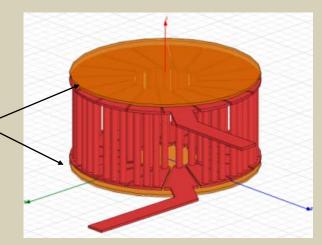

# "Optimized" PCB toroid (1)

- Custom design exploiting PCB technology: easy to manufacture, characteristics well reproducible

- Design can be optimized for low volume, low ESR, minimum radiated noise

- With the help of simulation tools (Ansoft Maxwell 3D and Q3D Extractor), we estimated inductance, capacitance and ESR for different designs. This guided the choice of the samples to manufacture as prototypes

- The addition of two Al layers (top, bottom) shields the parasitic radiated field efficiently

ATLAS upgrade week, February 09

F.Faccio, PH/ESE

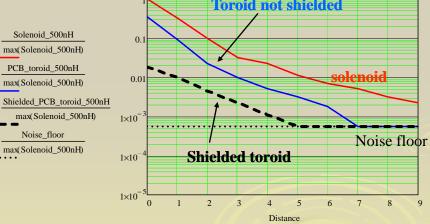

# "Optimized" PCB toroid (2)

- First samples manufactured at the CERN PCB shop

- Inductance, shield efficiency, ESR in agreement with simulation

- ESR can be decreased still by 2x by "filling" the vias this has not yet been done

- Now that the concept has been validated, we prepare for a prototype run with all the final characteristics (ESR, volume, shield material)

Measurement in the lab: Normalized current induced in 1 Cu loop at increasing distance from the inductor (cm)

ATLAS upgrade week, February 09

F.Faccio, PH/ESE

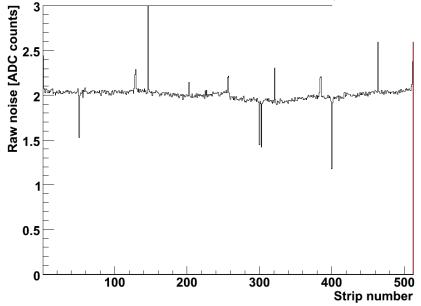

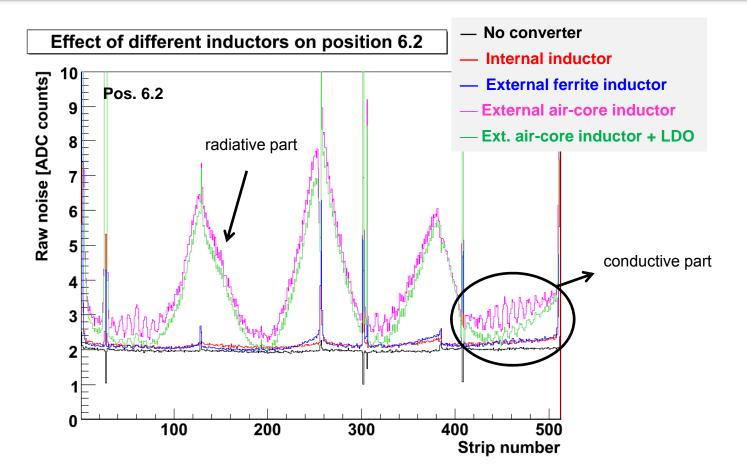

### System Test with a TEC Petal

7.10.2008 CMS TK Upgrade Power WG

Lutz Feld (RWTH Aachen)

### **System Test with Commercial DC-DC Converters**

- o internal or external ferrite core inductor: 10% noise increase

- o air-core inductor: huge noise increase, interference with module both radiative and conductive

- "radiative part" can be reproduced by an air core coil converter (not connected to a module) above hybrid

- "conductive part" can be reproduced by noise injection into the cables (see later)

Lutz Feld (RWTH Aachen)

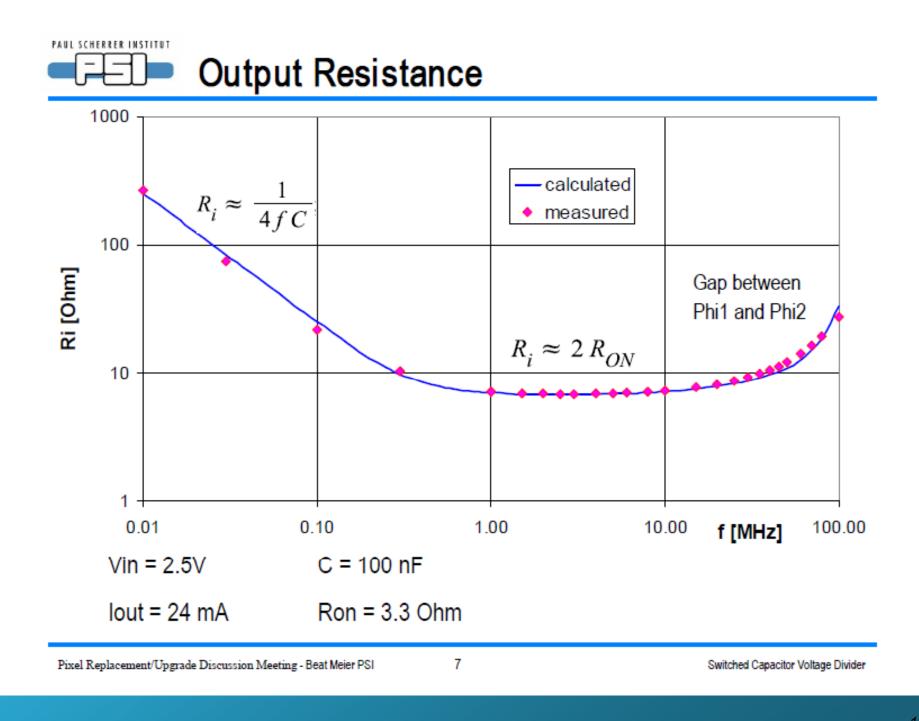

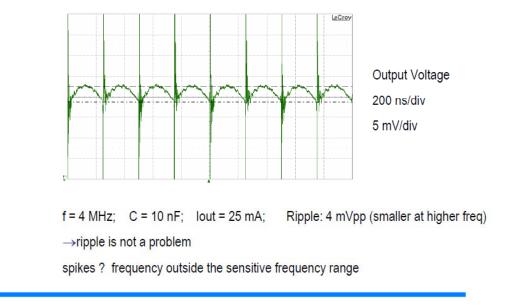

### Summary

- over 80% efficiency at 20 MHz switching frequency

- better efficiency with lower  $\text{Ron} \rightarrow \text{bigger FETs}$

- area on chip: 10'000 μm<sup>2</sup> (100 μm x 100 μm)

- output voltage to small (Vout = 1.1V @ Vin=2.5V and lout = 24 mA)

- · not adjustable, no voltage regulation

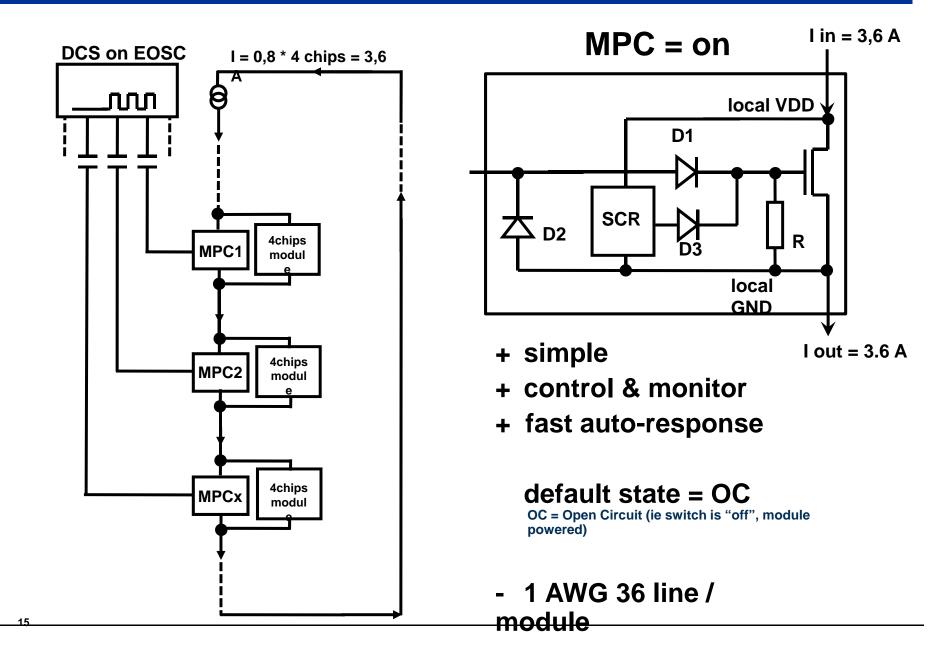

### Some highlights of serial powering R&D

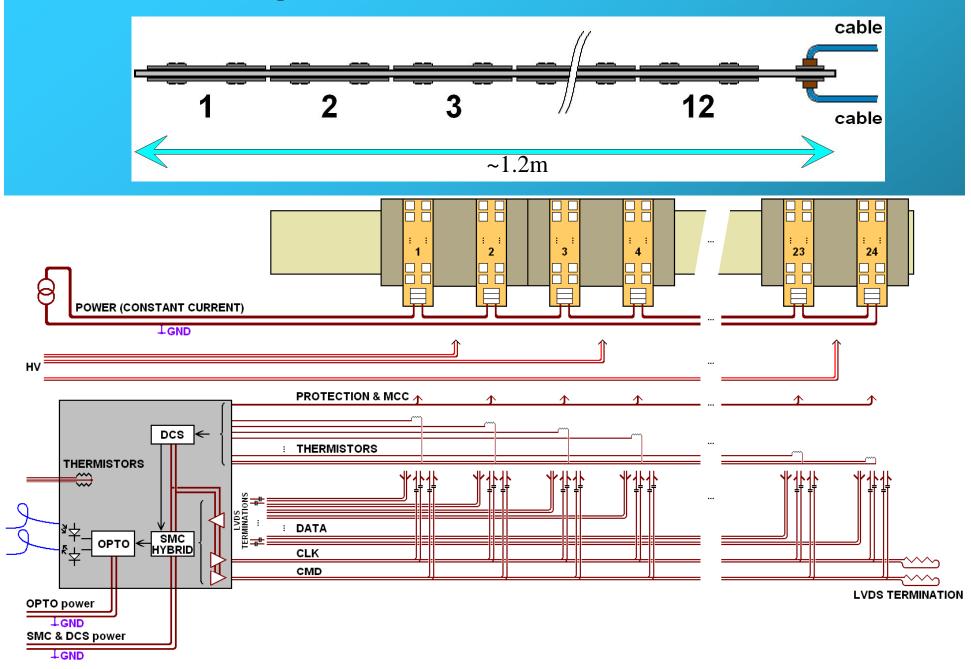

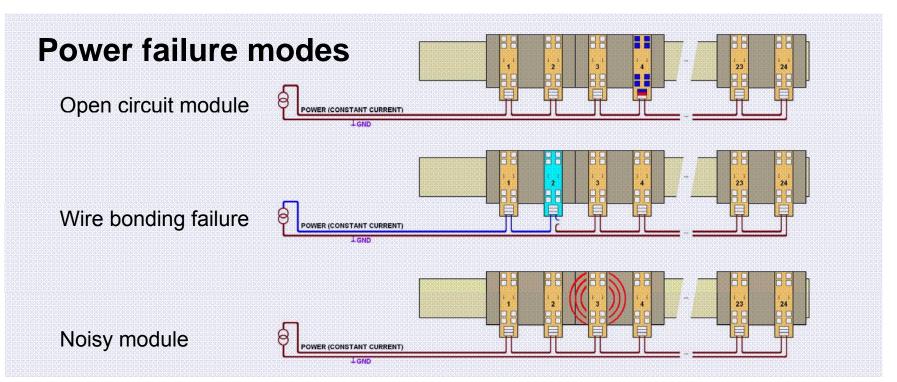

- Serial powering supermodule system architecture much better understood

- **Protection schemes** are emerging

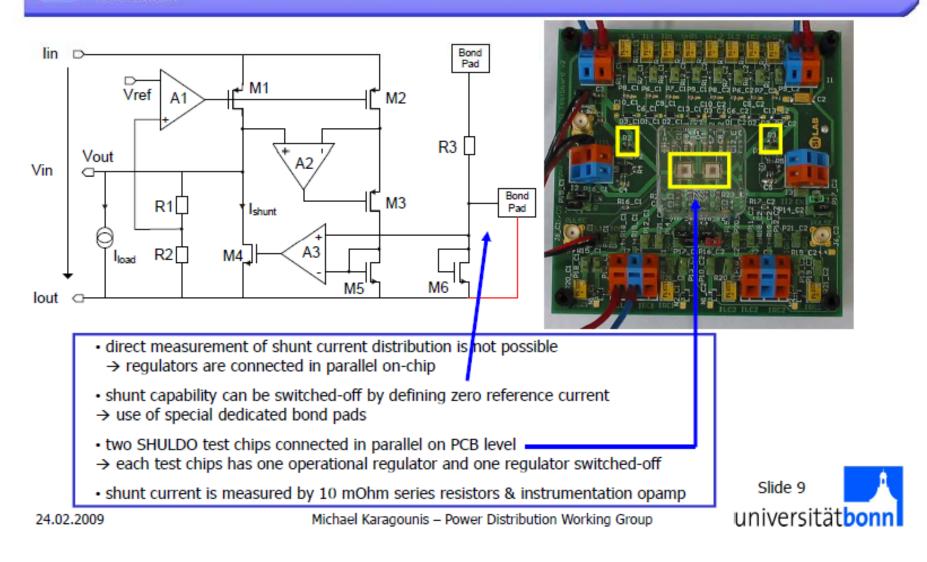

- **Custom shunt regulator circuitry** became available and seems to be functional

- AC LVDS coupling of data and control and command signals much better understood

### **SP** with commercial electronics

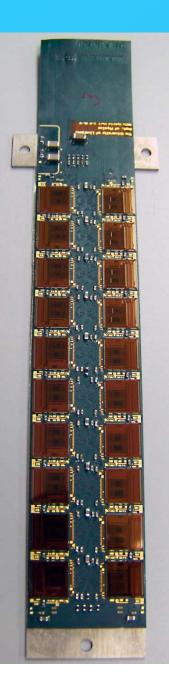

### **1)** Supermodule with SP (LBNL and RAL)

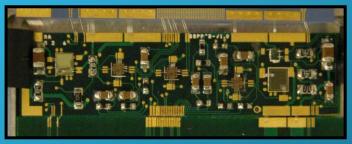

#### **BeO MCM and SP PCB**

#### PCB with SP circuitry, 38 mm x 9 mm

Results: 1) no noise, robust system 2) Can bias sensors with a common HV line 3) AC (Multidrop) LVDS working well

#### 2) Large supermodule with SP

30 MCMs with SP

### Supermodule architecture

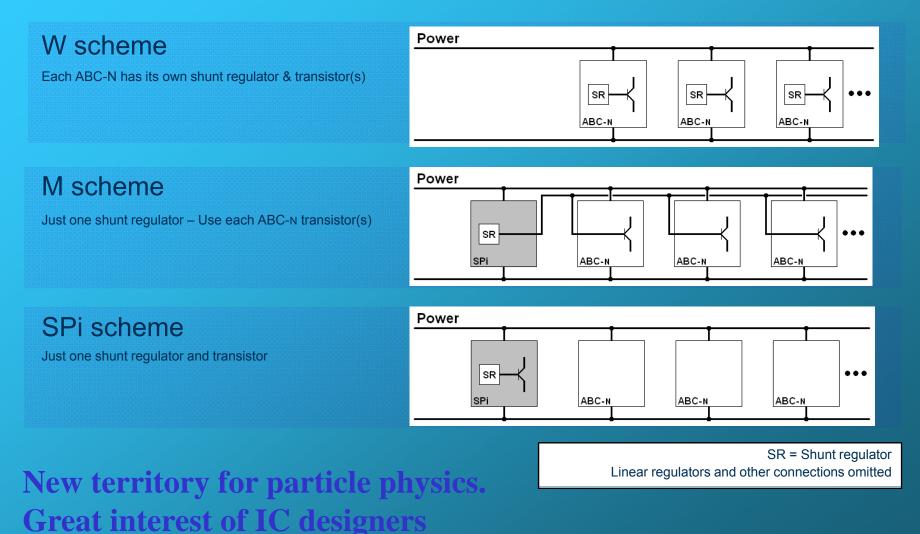

### **SP ASIC Design: ABC-Next and SPi**

Need radiation-hard SPASICs with small dynamic impedance. Which architecture is best?

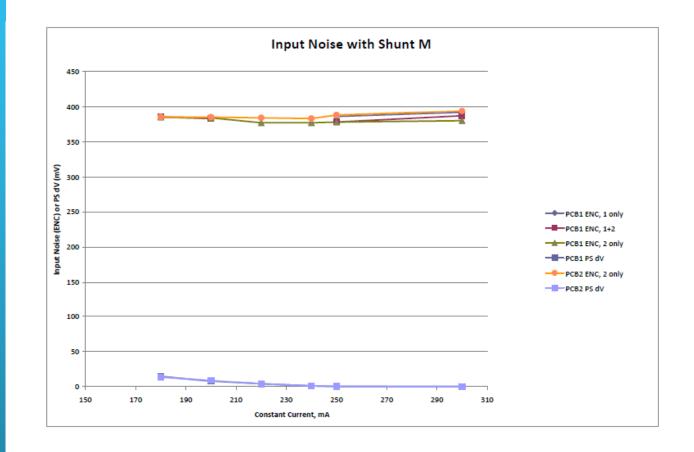

### **Setup for Measurement of Shunt Currents**

### **ABC-Next with SP blocks for W and M scheme**

Both schemes are being evaluated. Preliminary tests on single chips (rather than hybrid) are looking good.

Chips and SP blocks are functional and noise performance is OK

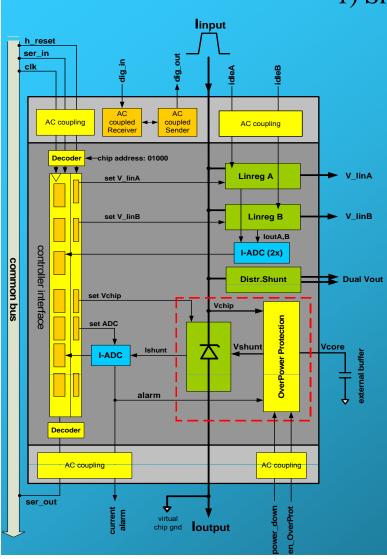

# SP made easy - the SPi IC <sup>\*</sup>Fermilab

SPi is stand-alone IC with all relevant SP elements:

1) Shunt regulator 2) Shunt transistor 3) LVDS ports

- plus Shunt current sensing ADC

- Over-current protection

- Linear regulators

suitable for 1.2 V to 2.5 V technology: TSMC 0.25µm CMOS area: ~ 14 mm<sup>2</sup> max. current through shunt transistor: 1-3 A

SPi makes SP straightforward.

Science & Technology Facilities Council

Richard Holt – Rutherford Appleton Laboratory ATLAS SCT SP protection options January 2009

# Why add protection?

Without protection, one failed module can adversely affect the operation of all other modules on stave Demonstration staves are very reliable - Protection is not strictly necessary

### **Serial powering sceme**

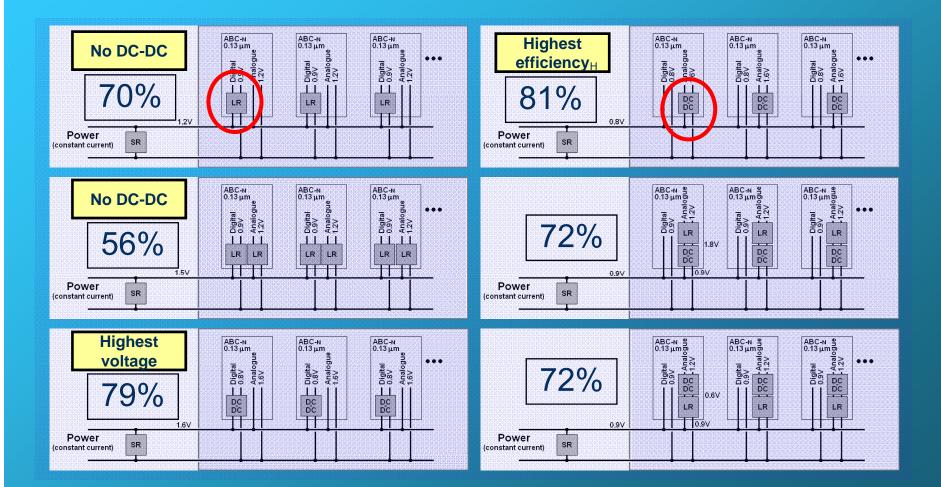

### Need both analog and digital voltage

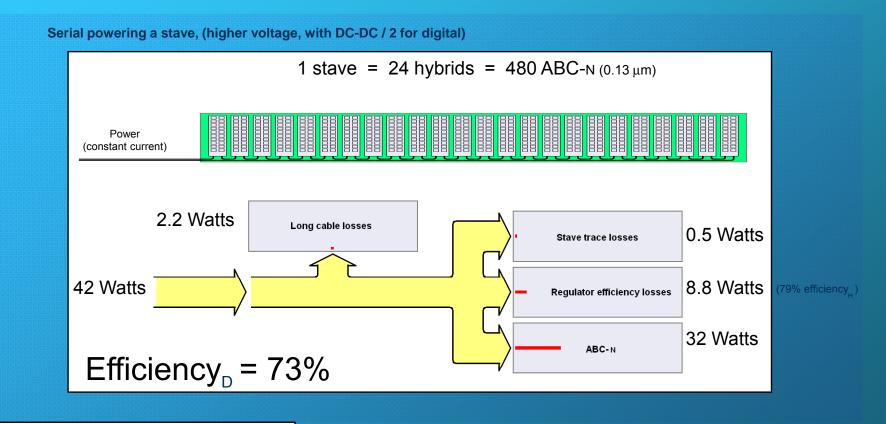

How? There are many choices. So far  $V_{analog} < V_{digital}$  in future :  $V_{analog} = 1.2$  V,  $V_{digital} - 0.9$  V Efficiency =: ABC-N power consumption/total consumption at rack power supply

### Possible schema of power management in ABCN (130 nm)

#### Possibly most efficient system compatible with serial powering

### **Power efficiency IP**

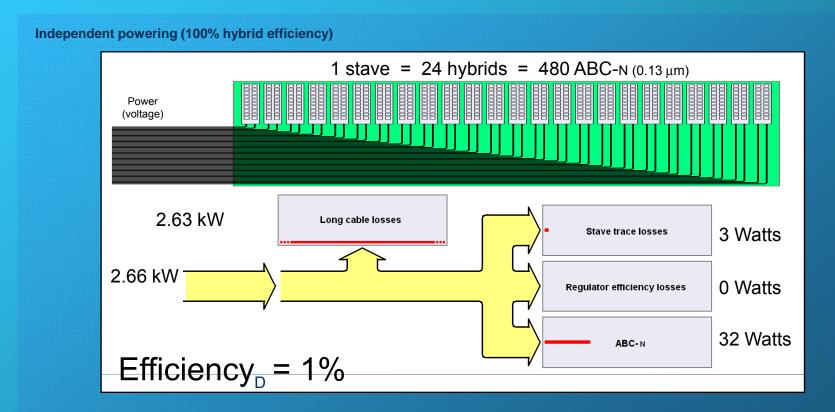

24 cables for digital power, 24 cables for analog. Also "sense wires".

$(I_{analog} = 0.32 \text{ A}, I_{digital} = 1.02 \text{ A}, \text{ cable resistance (both ways) 2 Ohms)}$

**Efficiency =:** ABC-N power consumption/total consumption (cables, regulator, ABC-N)

### **Power efficiency SP**

1 cable for digital plus analog current. Only minimal cable losses!

Cables assumed to be 2 ohms total for each power line pair Regulator power = (1/eff<sub>H</sub> - 1) x ABC power Stave supply current = (32 + 8.5)watts / (1.6volts x 24) = 1.1amps

Numbers rounded

### Summary and next steps

- Characterize various ASICs designs for both DC-DC and SP

- Move on to more realistic technologies (e.g. 130 nm CMOS)

- Understand system architecture better

- Gain practical experience with "full system" prototypes (sensors, readout chips, hybrids, modules, supermodules)

### Huge progress, but

The more progress we make, the larger the challenge seems to become...Still looking good