-

# Future of Compute is Big Data

Mark Seager Intel Fellow, CTO for HPC Ecosystem Intel Corporation

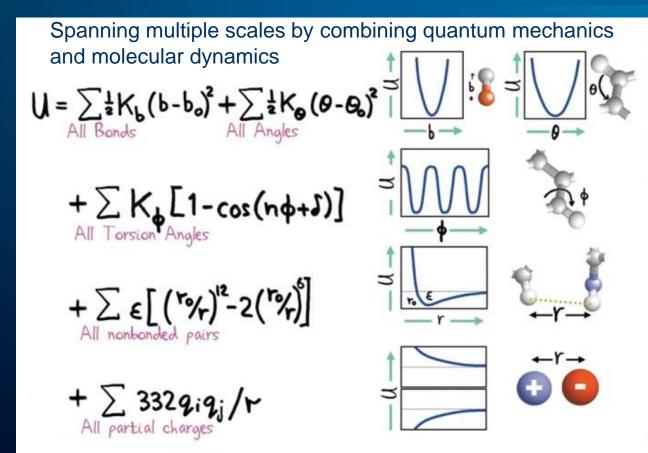

## Traditional HPC is scientific simulation First ever Nobel prize for HPC takes the experiment into cyberspace

Chemical reactions occur at lightning speed; electrons jump between atoms hidden from the prying eyes of scientists. The Nobel Laureates in Chemistry 2013 have made it possible to map the mysterious ways of chemistry by using computers. Detailed knowledge of chemical processes makes it possible to optimize catalysts, drugs and solar cells.

### Martin Karplus Michael Levitt Arieh Warshe

The Nobel Prize in Chemistry 2013 was awarded jointly to Martin Karplus, Michael Levitt and Arieh Warshel "for the development of multi-scale models for complex chemical systems".

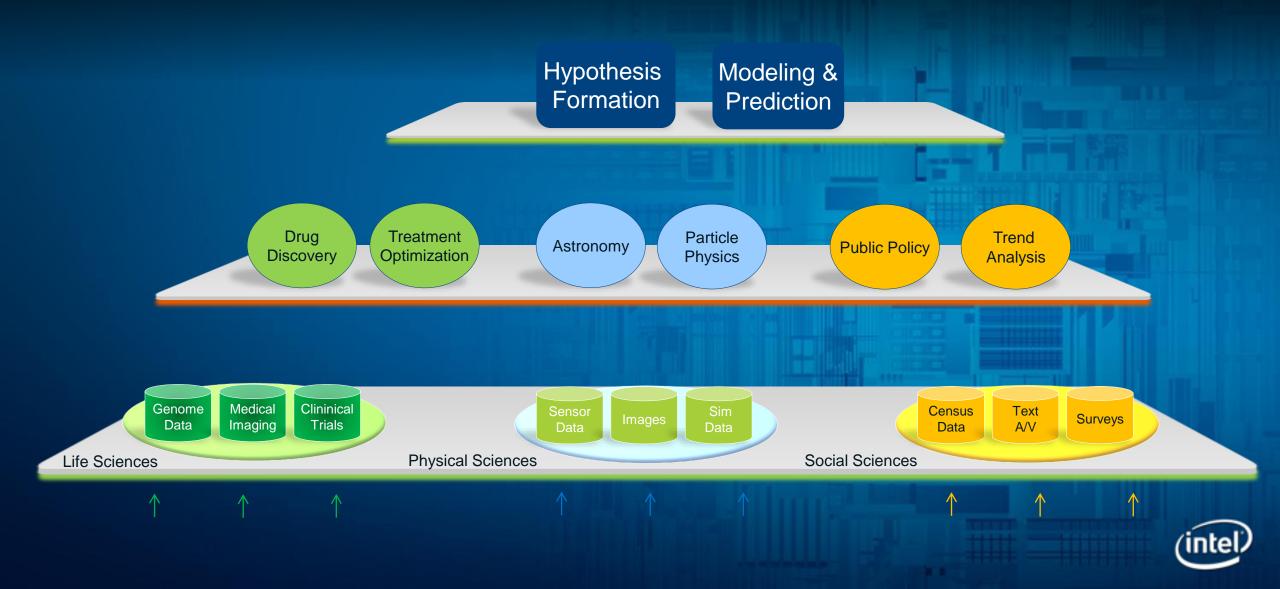

# Other emerging technical computing usage models are driven by Big Data

### Transform data into useful knowledge

# Data-Driven Discovery

# Data-Driven Discovery in Science

600 million collisions / sec

Detecting 1 in 1 trillion events to help find the Higgs Boson

1 human genome = 1 petabyte

Finding patterns in clinical and genome data at scale can cure cancer and other diseases

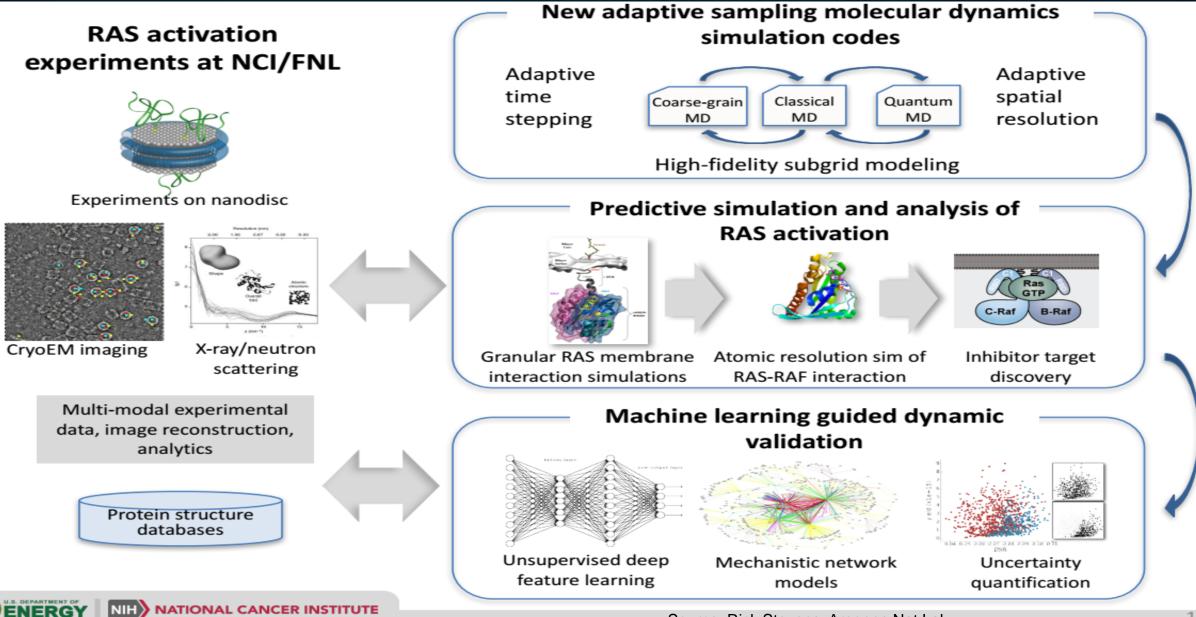

# Project Moonshot for Cancer: Predictive Oncology Pilot 2

Source: Rick Stevens, Argonne Nat Lab

# **Convergence of Driving Forces**

**19B** Connected devices by 2016<sup>1</sup>

### \$200B Cloud services In 2016<sup>2</sup>

2X Annual growth in supercomputing FLOPS<sup>3</sup>

HPC

### **Big Data**

**15PB**

Data collected in 1 year at CERN<sup>4</sup>

1 Source: Cisco® Visual Networking Index (VNI) Forecast (2011-2016)

2 Source: Gartner Worldwide IT Spending Forecast, 2Q12 Update

3 Source: Top 500 list: Top 10 change from November 2007 to November 2012

4 Source: CERN

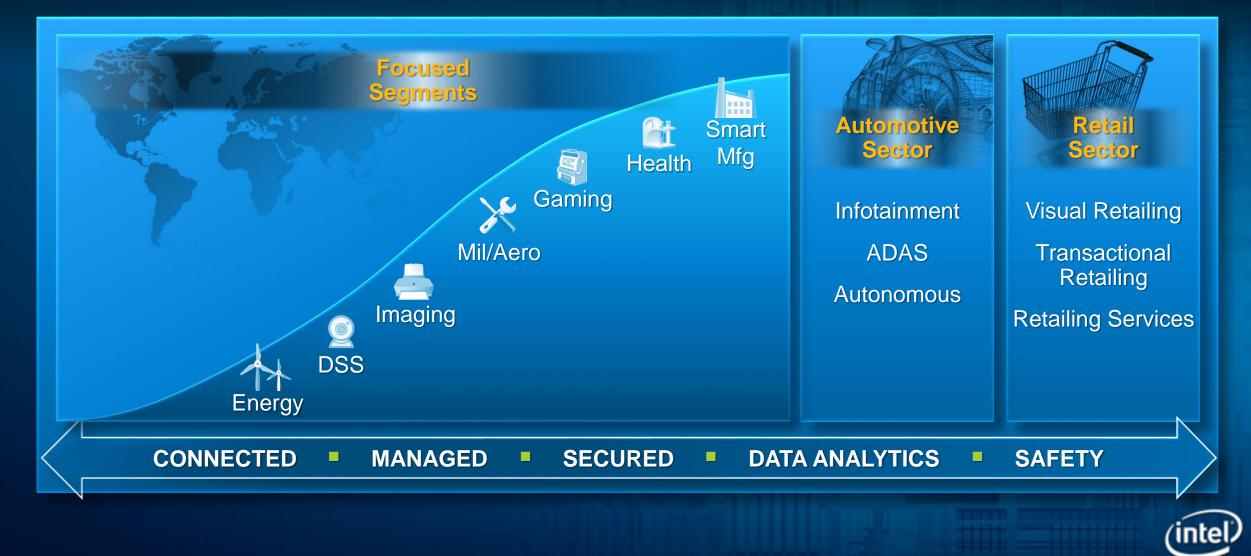

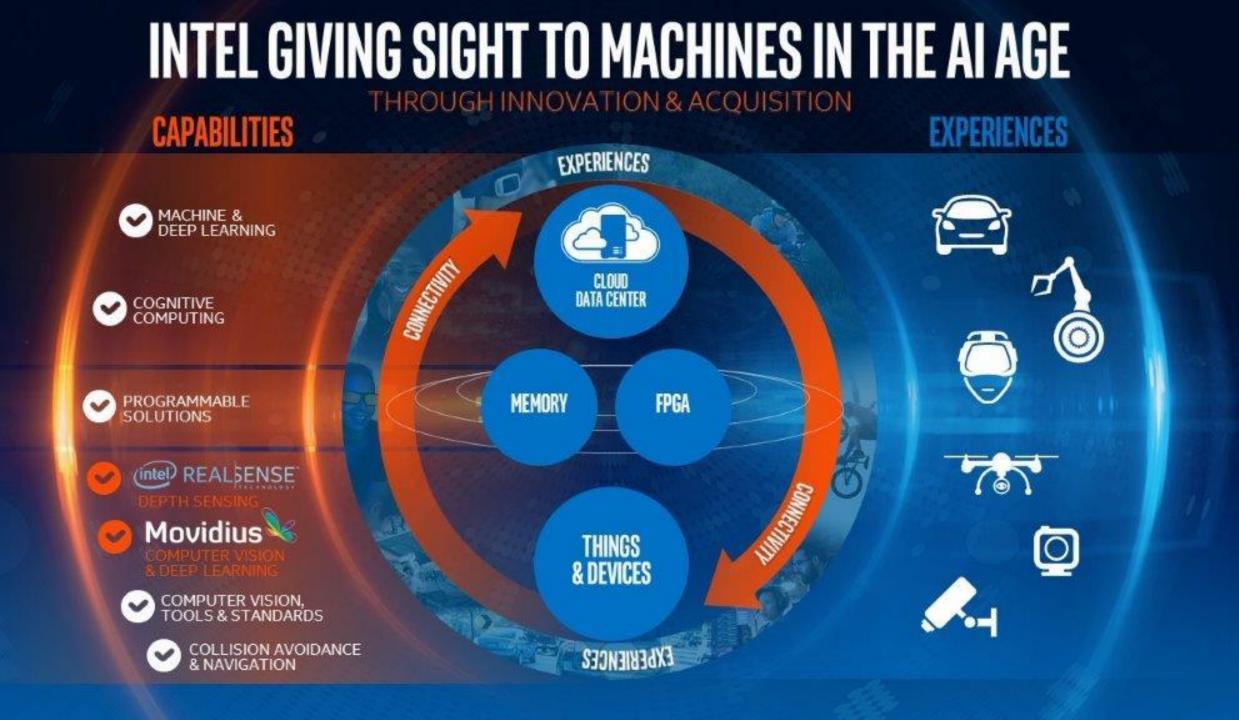

# Intelligent Devices - New Era of Computing Enabling an Industry of Pervasive Computing

# Intel® Scalable System Framework A Holistic Solution for All HPC Needs

Small Clusters Through Peta and Exascale Compute and Data-Centric Computing Standards-Based Programmability IA and HPC Ecosystem Enabling On-Premise and Cloud-Based

Intel® Xeon® Processors Intel® Xeon Phi™ Processors Intel® FPGAs and Server Solutions Intel® Solutions for Lustre\* Intel® Optane™ Technology 3D XPoint™ Technology Intel® SSDs

Intel® Omni-Path Architecture Intel® Silicon Photonics Intel® Ethernet Intel® HPC Orchestrator Intel® Software Tools Intel® Cluster Ready Program Intel Supported SDVis

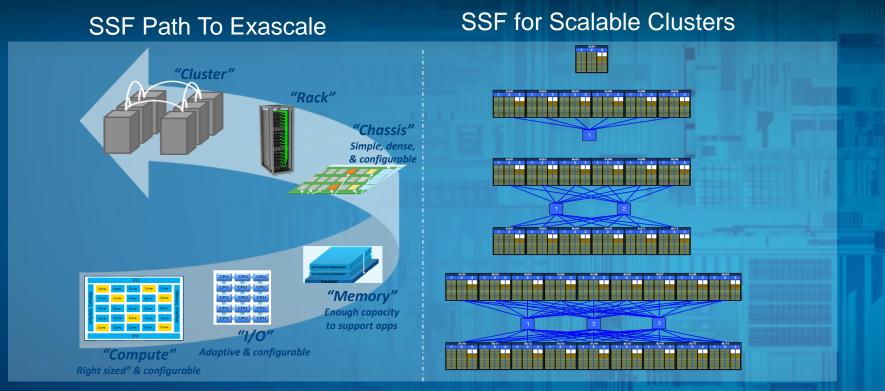

# SSF: Enabling Configurability & Scalability from components to racks to clusters

- Xeon or Xeon-Phi based on workload needs

- Compute flexibly aggregated

- Lowest latency compute to compute interconnect

- I/O Topologies for best performance

- Configurable I/O bandwidth director switch

- Burst buffer to decouple storage from I/O

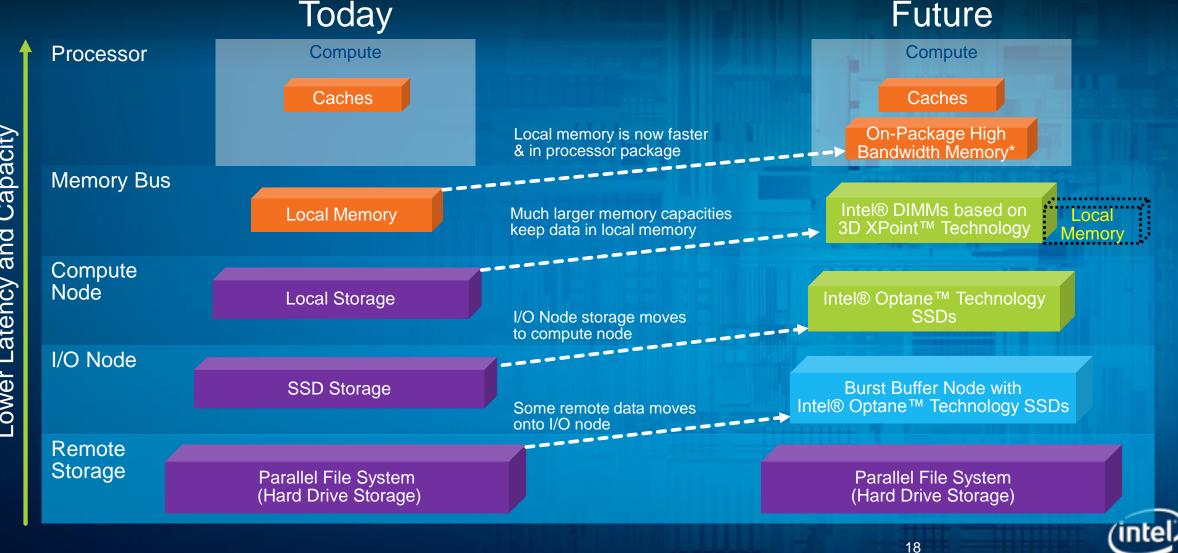

# Tighter System-Level Integration Innovative Memory-Storage Hierarchy

INTEL<sup>®</sup> SSF Memory

Higher Bandwidth. Lower Latency and Capacity

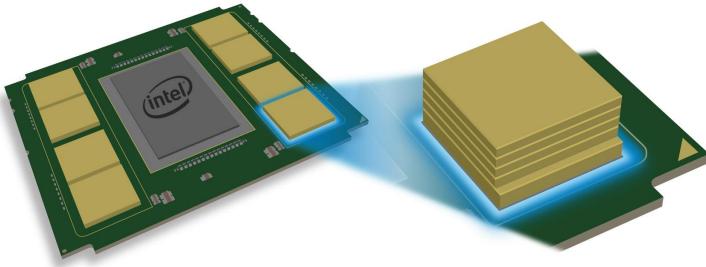

# Bringing Memory Back Into Balance High Bandwidth, On-Package Memory

**Up to 16GB with Knights Landing** 5x the Bandwidth vs DDR4<sup>1</sup>, >400 GB/s<sup>1</sup> >5x More Energy Efficient vs GDDR5<sup>2</sup> >3x More Dense vs GDDR5<sup>2</sup> **3** Modes of Operation Flat Mode: Acts as Memory **Cache Mode: Acts as Cache** Hybrid Mode: Mix of Cache and Flat

<sup>1</sup> Projected result based on internal Intel analysis of STREAM benchmark using a Knights Landing processor with 16GB of ultra high-bandwidth versus DDR4 memory with all channels populat <sup>2</sup> Projected result based on internal Intel analysis comparison of 16GB of ultra high-bandwidth memory to 16GB of GDDR5 memory used in the Intel® Xeon Phi<sup>™</sup> coprocessor 7120P.

# NAND Flash and 3D XPoint<sup>™</sup> Technology

# **3D MLC and TLC NAND** 3D XPoint<sup>™</sup> Technology Selector Memory Cell Enabling highest capacity SSDs Enabling highest performance at the lowest price SSDs and expanding use cases

# 3D Xpoint<sup>™</sup> Technology

#### **Cross Point Structure**

Perpendicular wires connect submicroscopic columns. An individual memory cell can be addressed by selecting its top and bottom wire.

### **Non-Volatile**

3D XPoint<sup>™</sup> Technology is non-volatile—which means your data doesn't go away when your power goes away—making it a great choice for storage.

#### **High Endurance**

Unlike other storage memory technologies, 3D XPoint™ Technology is not significantly impacted by the number of write cycles it can endure, making it more durable.

### Stackable

These thin layers of memory can be stacked to further boost density.

### Selector

Whereas DRAM requires a transistor at each memory cell—making it big and expensive—the amount of voltage sent to each 3D XPoint<sup>™</sup> Technology selector enables its memory cell to be written to or read without requiring a transistor.

#### Memory Cell

Each memory cell can store a single bit of data.

### **Transforming the Memory Hierarchy**

For the first time, there is a fast, inexpensive and non-volatile memory technology that can serve as system memory and storage.

Processor

3D XPoint<sup>™</sup> Technology

~8x to 10x Greater Density than DRAM<sup>1</sup>

3D XPoint<sup>™</sup> Technology's simple, stackable, transistor-less design packs more memory into less space, which is critical to reducing cost.

DRAM 3D XPoint<sup>™</sup> Technology

TIME

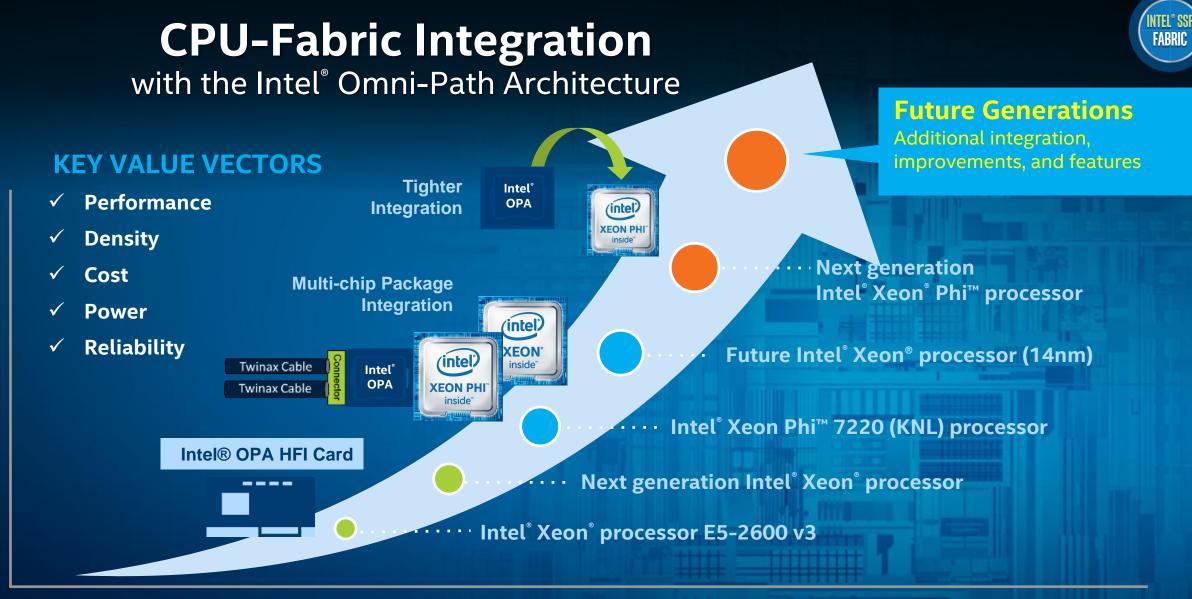

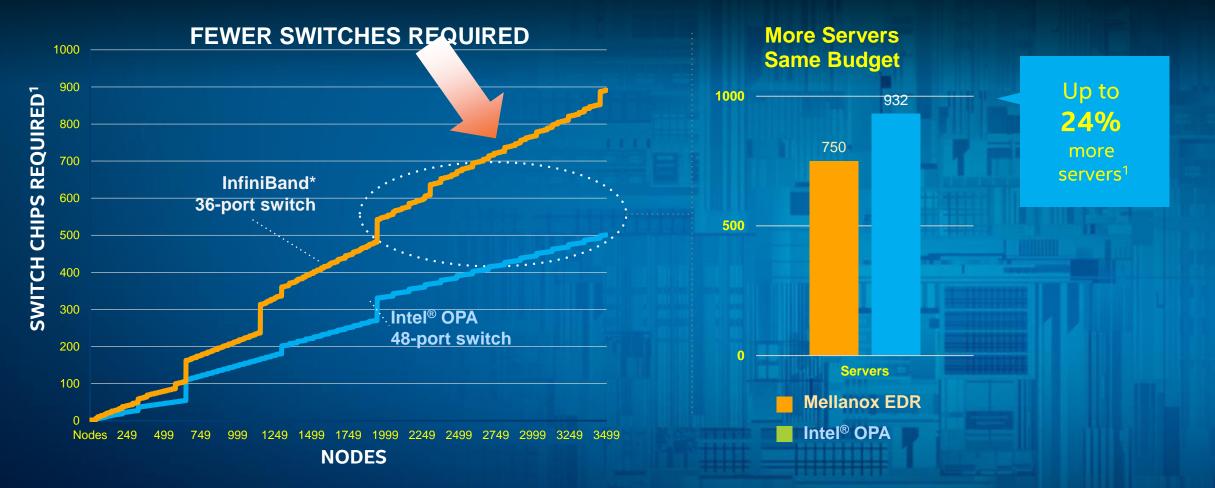

# OmniPath is Optimized for scalability

<sup>1</sup> Configuration assumes a 750-node cluster, and number of switch chips required is based on a full bisectional bandwidth (FBB) Fat-Tree configuration. Intel® OPA uses one fully-populated 768-port director switch, and Mellanox EDR solution uses a combination of 648-port director switches and 36-port edge switches. Intel and Mellanox component pricing from www.kernelsoftware.com, with prices as of May 5, 2016. Compute node pricing based on Dell PowerEdge R730 server from www.dell.com, with prices as of November 3, 2015. Intel® OPA pricing based on estimated reseller pricing based on projected Intel MSRP pricing at time of launch. \* Other names and brands may be claimed as property of others.

INTEL<sup>®</sup> SSI FABRIC

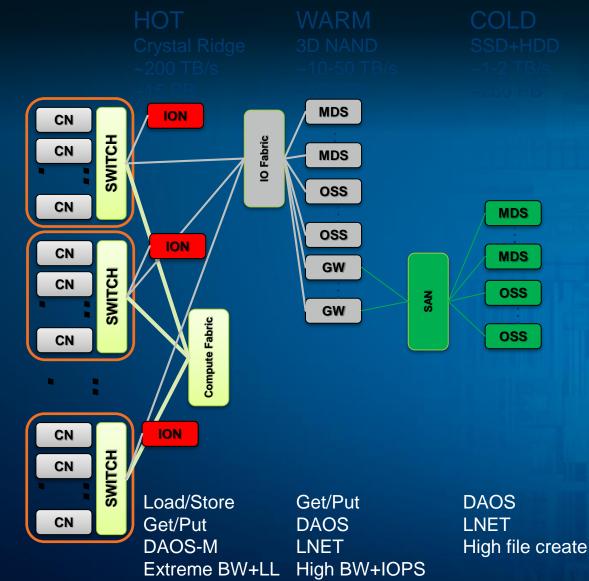

# New storage paradigm for data intensive systems

## SSF Enables HPC+HPDA workloads

- System components can be configured to match workload requirements

- Enables new access methodologies (DAOS) to create new generation applications

- Incremental improvements to Lustre to provide enhanced performance for existing applications

### Distributed Asynchronous Object Storage

# Benefit from Intel's long-standing investments

# Legal Information

INFORMATION IN THIS DOCUMENT IS PROVIDED "AS IS". NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. INTEL ASSUMES NO LIABILITY WHATSOEVER AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO THIS INFORMATION INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

Software and workloads used in performance tests may have been optimized for performance only on Intel microprocessors. Performance tests, such as SYSmark and MobileMark, are measured using specific computer systems, components, software, operations and functions. Any change to any of those factors may cause the results to vary. You should consult other information and performance tests to assist you in fully evaluating your contemplated purchases, including the performance of that product when combined with other products.

Intel product plans in this presentation do not constitute Intel plan of record product roadmaps. Please contact your Intel representative to obtain Intel's current plan of record product roadmaps.

Intel's compilers may or may not optimize to the same degree for non-Intel microprocessors for optimizations that are not unique to Intel microprocessors. These optimizations include SSE2, SSE3, and SSE3 instruction sets and other optimizations. Intel does not guarantee the availability, functionality, or effectiveness of any optimization on microprocessors not manufactured by Intel.

Microprocessor-dependent optimizations in this product are intended for use with Intel microprocessors. Certain optimizations not specific to Intel microarchitecture are reserved for Intel microprocessors. Please refer to the applicable product User and Reference Guides for more information regarding the specific instruction sets covered by this notice.

#### Notice revision #20110804

All products, computer systems, dates, and figures specified are preliminary based on current expectations, and are subject to change without notice. Intel processor numbers are not a measure of performance. Processor numbers differentiate features within each processor family, not across different processor families. Go to: http://www.intel.com/products/processor\_number

Intel, processors, chipsets, and desktop boards may contain design defects or errors known as errata, which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Intel, Intel Xeon, Intel Xeon Phi, the Intel Xeon Phi logo, the Intel Xeon logo and the Intel logo are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

Intel does not control or audit the design or implementation of third party benchmark data or Web sites referenced in this document. Intel encourages all of its customers to visit the referenced Web sites or others where similar performance benchmark data are reported and confirm whether the referenced benchmark data are accurate and reflect performance of systems available for purchase.

Other names and brands may be claimed as the property of others. Copyright © 2013, Intel Corporation. All rights reserved.