# **Upgrade of the ATLAS Hadronic Tile Calorimeter** for the High Luminosity LHC

Michaela Mlynáriková, on behalf of the ATLAS Tile Calorimeter System

Charles University, Prague, Czech Republic

No. 166

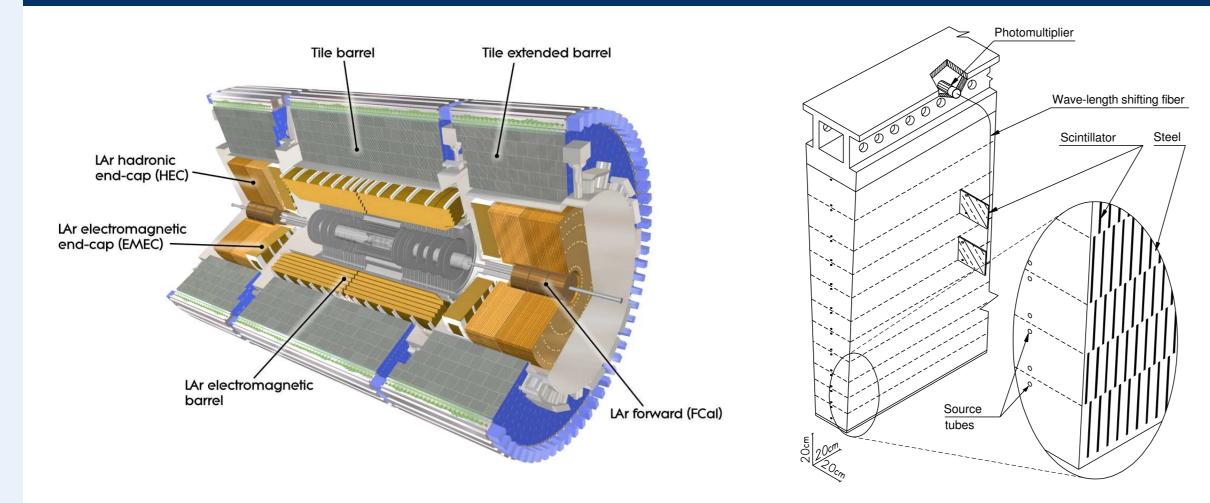

#### **ATLAS** Tile Calorimeter

- Sampling hadronic calorimeter made of alternating steel plates and scintillating tiles

- Scintillating tiles are read out by 2 photomultiplier tubes (PMTs) via wave length shifting fibers

- Divided into long barrel and two extended barrels along the beam line and segmented azimuthally into 64 modules

- Energy reconstruction of hadrons, jets,  $\tau$  particles and missing transverse momentum; identification of electrons and muons

### High Luminosity LHC (HL-LHC)

- ► The Upgraded LHC for HL-LHC will deliver five times the LHC nominal instantaneous luminosity.

- ► The ATLAS upgrade, in 2024, will adjust the detector and data acquisition system for the HL-LHC.

- ► Tile Calorimeter will undergo a major replacement of its on- and off-detector electronics. All PMT signals will be digitized and send off the detector at the full collision rate of 40 MHz. The off-detector pre-processor (PPR) will buffer the data and calculate the cell energies and trigger primitives. This will provide better precision of the calorimeter signals used by the trigger system. The upgrade will also improve reliability and redundancy of the system.

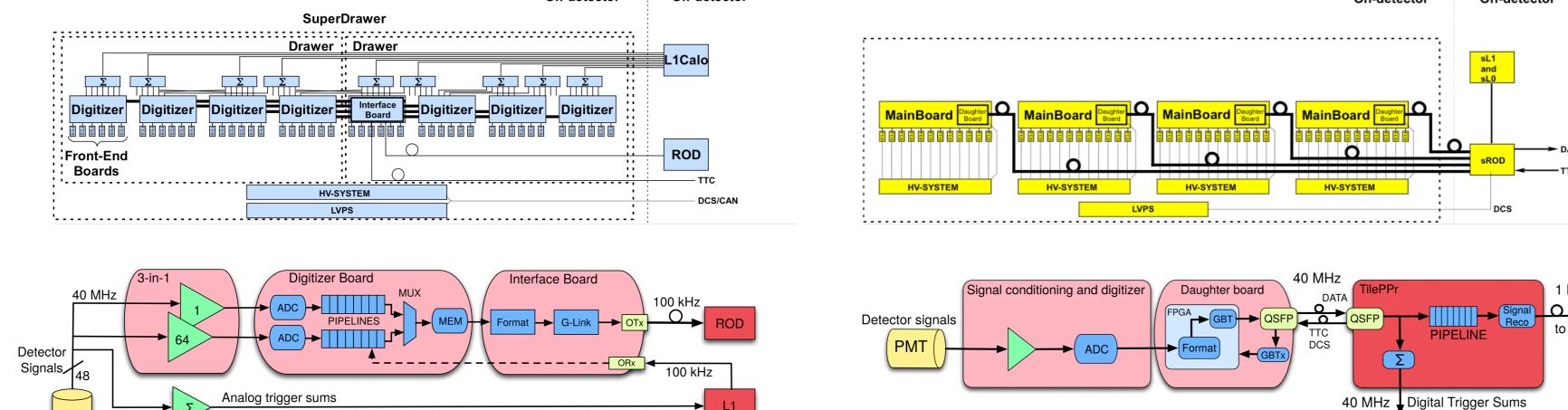

#### Phase II Tile Calorimeter Upgrade

#### **CURRENT SYSTEM UPGRADED SYSTEM**

$\rightarrow$  Flexible trigger logic, lower noise and higher granularity

#### Hybrid Demonstrator

| Level I Trigger Signals: | Low-granularity Analog Sum | Fully Digitized     | ightarrow Flexible trigger logic, lower | noise and   | high |

|--------------------------|----------------------------|---------------------|-----------------------------------------|-------------|------|

| Pipeline Memory:         | On Detector                | Off Detector        | ightarrow Performance and flexibility   |             |      |

| Readout Modularity:      | $1{+}1$ Links, 48 PMTs     | 16+16 Links, 6 PMTs | ightarrow Reliability                   |             |      |

| LVPS Modularity:         | 1 Unit, 48 PMTs            | 4+4 Units, 12 PMTs  | ightarrow Reliability                   |             |      |

| HV Modularity:           | 2 Units, 24 PMTs           | 4+4 Units, 12 PMTs  | ightarrow Reliability                   |             |      |

|                          | On-detector                | Off-detector        |                                         | On-detector | Off- |

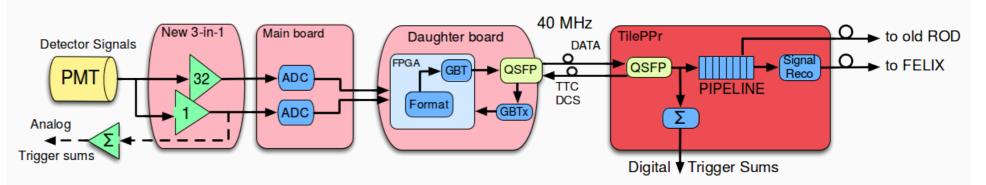

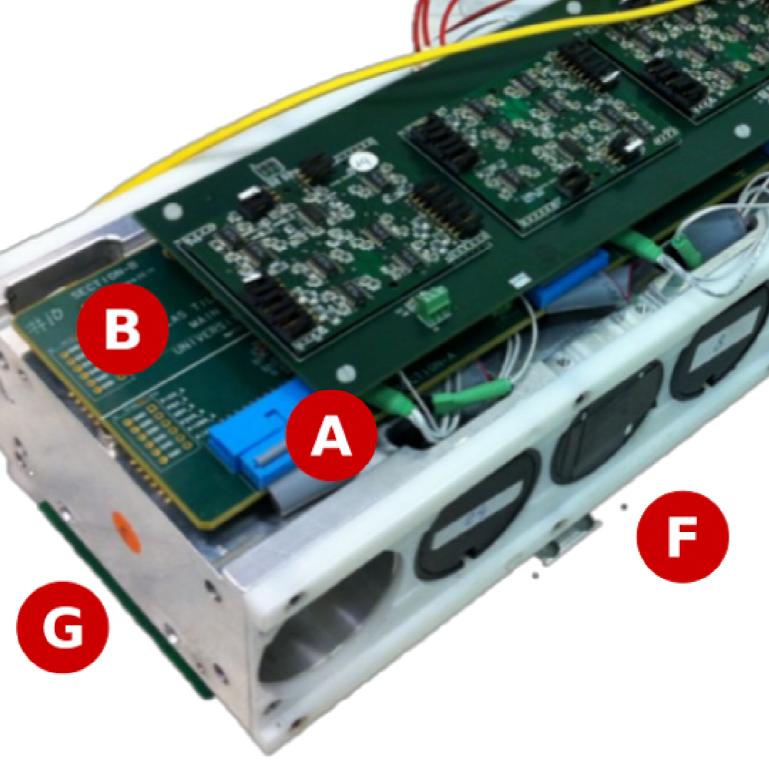

- TileCal Demonstrator is a prototype of the upgraded readout system and it is compatible with the current system.

- The Demonstrator has been interfaced with legacy control, monitoring and calibration infrastructure and with the new off-detector electronics.

- It was extensively tested during three test beam campaigns in 2015 and 2016 and testing will continue during two test beam periods in 2017.

- Insertion of one Demonstrator module in the current system is planned during one of the short LHC shutdowns during Run 2.

#### Tile Calorimeter Upgrade Design

## Front End Board (FEB)

- Process PMT signals

- Slow integration for Cs calibration

- Charge injection calibration (CIS)

#### Front End Strategies

#### **Upgraded 3-in-1** : Discrete elements

#### Daughterboard

- Data collection and control system

- ► 2x redundancy data transmission to off-detector

- On-detector electronics timing management

**PMTs**

Low Voltage Power Supply

Same reliable components

► 8 Identical + 10V Bricks

Point of load regulators

More modular and redundant

#### **Redesigned Chassis and Cable Carriers**

- Modular design

- (1 Tile Module = 4 Mini-drawers)

- Easier installation, extraction and repair

#### High voltage (HV) regulation

- Improves current design

- Passive pulse shaping

- ► Bi-gain amplification (1x, 32x)

**QIE** : Charge Integrator in an ASIC chip

- No pulse shaping

- Signal digitization

**FATALIC** : Implemented as ASIC

- Active pulse shaping

- ► Tri-gain (1x, 8x, 64x)

- Signal digitization

#### Mainboard: Specific for each FEB

- ► Interface between FEB and Daughter board

- Low Voltage control

- Signal digitization for 3-in-1 FEB option

- Control of CIS and Cesium calibrations

#### Individual PMT control (2 options studied): Remote HV

- Off-detector

- ► HV to each PMT separately

#### Local HV/HV Opto

- Improved monitoring and radiation hardness

- ► HV supplied to 6 PMTs

#### **Tile Preprocessor**

- Receives high-speed data from on-detector electronics

- ► 40 MHz digital inputs for the L0 Triggers

- Keeps data in pipelines pending trigger decision

- Signal reconstruction

- Trigger, timing and control signals to FEB

- Monitoring, data control system

- Interface with ATLAS data acquisition system

#### **Status of Control and Calibration Tests**

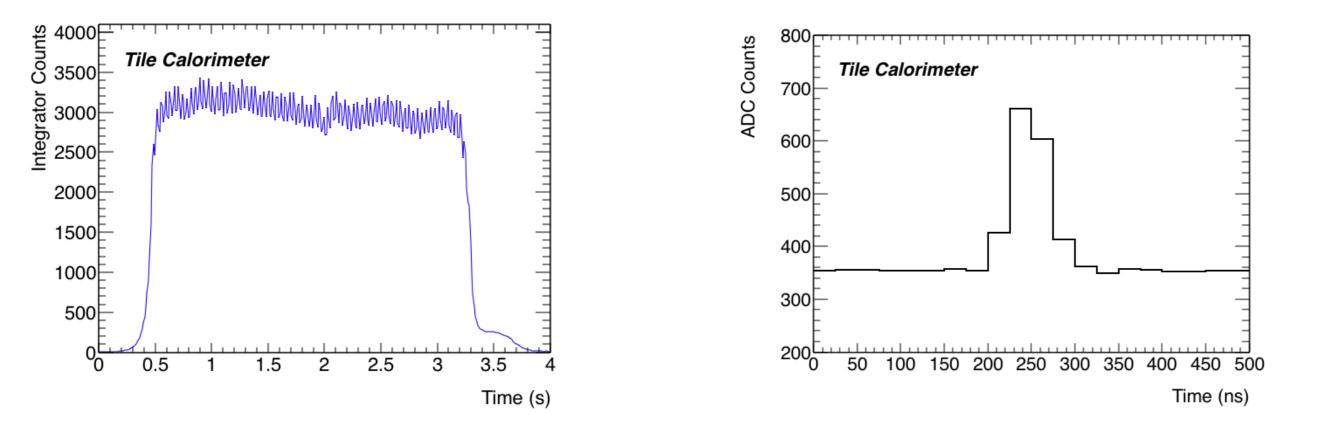

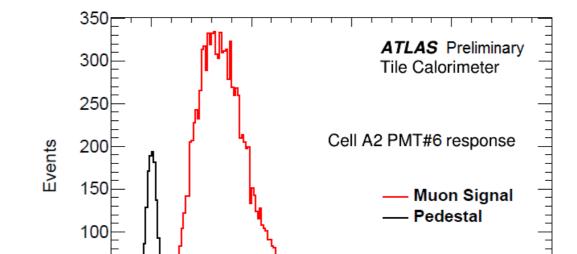

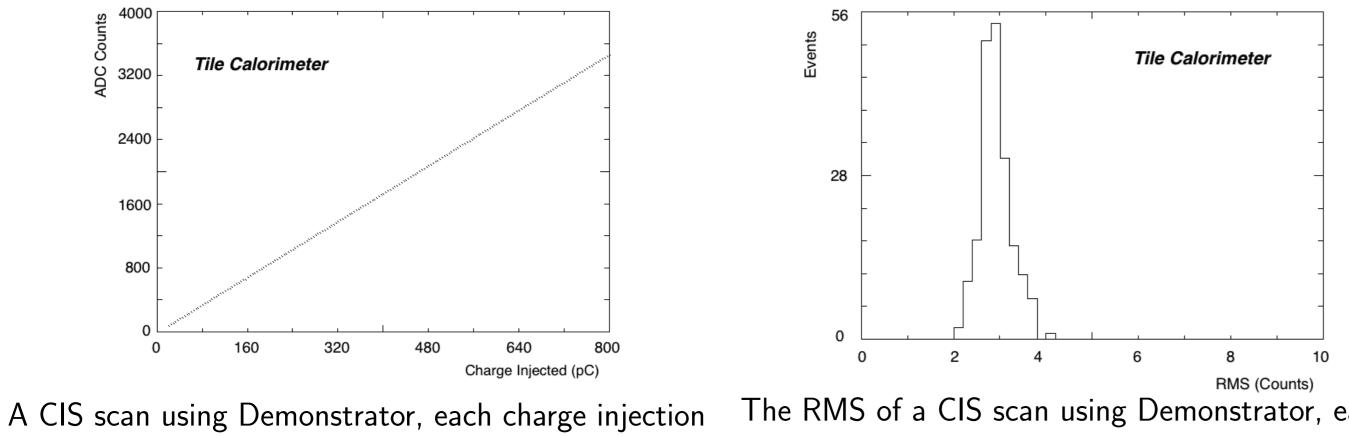

► Plots for Demonstrator (3-in-1) – QIE and FATALIC provide comparable results

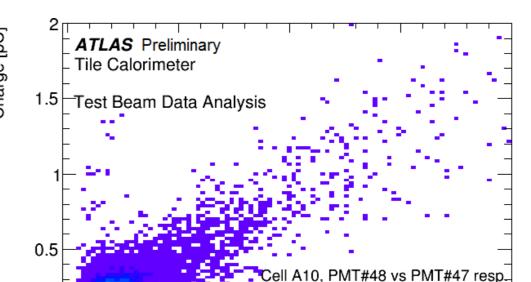

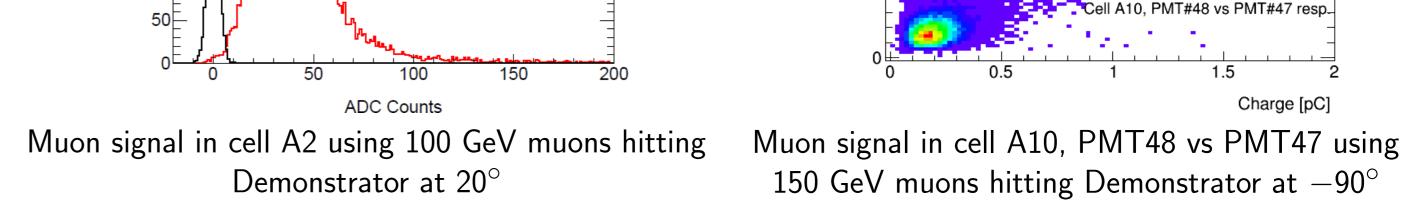

#### Test Beam Results

► Good performance for Demonstrator (3-in-1), QIE and FATALIC

PMTs with active dividers

Linearity in high luminosity

Demonstrator integrator response for Extended Barrel Demonstrator Low Gain response to a Laser pulse in Cell D-6 to a passing Cesium source the hundreds of GeV, sampled at 40 MHz

step is sampled 50 times and the average is plotted for that step

The RMS of a CIS scan using Demonstrator, each charge injection step is sampled 50 times and the RMS of these 50 samples is plotted for each step

#### Summary

- ► The upgraded Tile calorimeter architecture was designed to meet ATLAS requirements for the HL-LHC.

- Control and calibrations tests proved successful in the Demonstrator, QIE and FATALIC.

- ▶ Three test beam campaigns conducted in 2015 and 2016 and two test beam periods are planned in 2017.

- ► 3-in-1, QIE and FATALIC front-end technologies were successfully evaluated at the testbeam.

- ► Three different front-end and two HV options are being investigated for the upgrade and a final solution will be chosen after test-beam studies.

#### References

- https://twiki.cern.ch/twiki/bin/view/AtlasPublic/ApprovedPlotsTileUpgrade

- https://twiki.cern.ch/twiki/bin/view/AtlasPublic/ApprovedPlotsTileUpgrades

- https://twiki.cern.ch/twiki/bin/view/AtlasPublic/ApprovedPlotsTileTestBeamResults

Charge [pC]