### Trans-Impedance Amplifier solution for VFE upgrade

Pascal Baron CEA-Saclay Irfu/SEDI May 12th 2016

- TIA solution

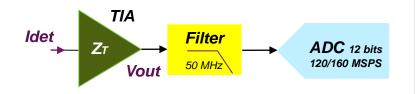

- **TIA** architecture

- Performances

- **Status & Planning**

### Conclusion

- TIA solution comes from Marc Dejardin works

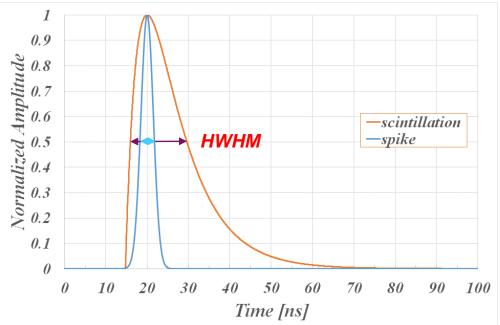

- Work on the APD signal shape which provide the best information to cope the upgrade requirements:

- Online spike tagging by shape analysis (*HWHM\**)

- Offline energy reconstruction with Pileup

- Allows best timing resolution

# Freedom to tune algorithm to follow detector aging & unforeseen "features"

#### \*Half Width at Half Maximum

CMS ECAL VFE phase II upgrade workshop 11-13 Mai 2016 CEA-Saclay INSTN

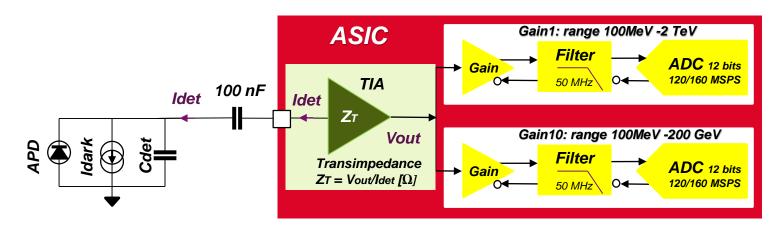

- **TIA ASIC** architecture

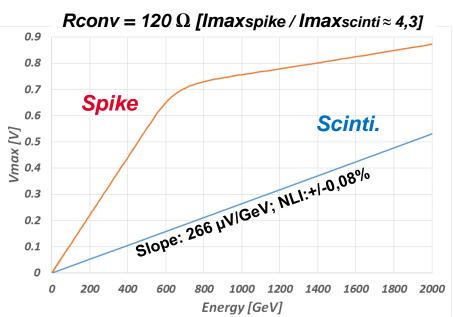

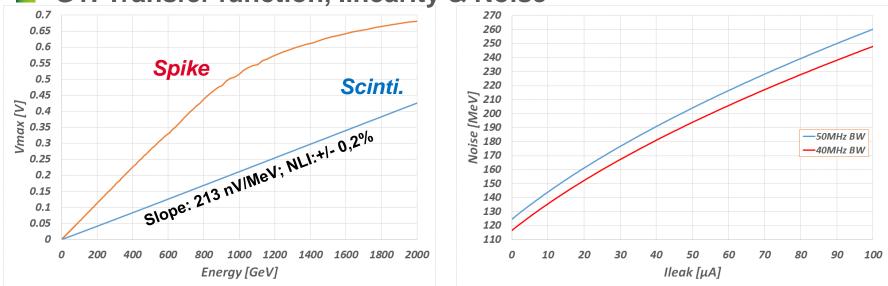

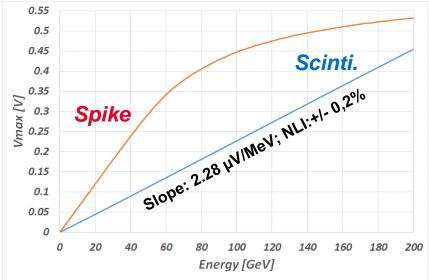

- 1 TIA for 2 Gains called G1 & G10

- G1: 100MeV 2 TeV; G10: 100 MeV 200 GeV

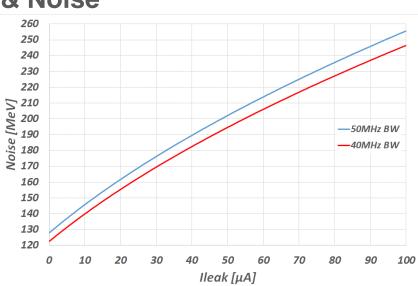

- 1 Gain: gain + Filter [50 MHz] + 12-bit ADC 120/160 MSPS

- Detector

- Cdet = 200 pF

- Ileak from 10 µA to 100 µA

- Crystal: 4.5 p.e/MeV; APD gain: 50 => Qinmax. = 72 pC

- Technology

- TSMC 130 nm [1.2V Core Voltage / 2,5V I/O Voltage]

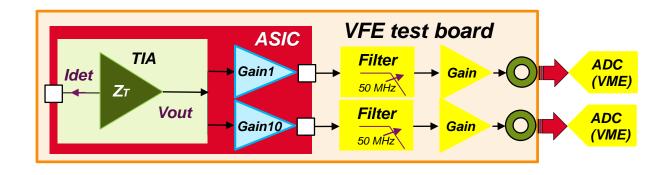

- Prototype

- 5 channels: 1 TIA + 2 Gains G1 & G10

- Filtering & Gain on VFE test board

- External ADC: 50 MHz

- Additional functionalities

- Additional blocks for technology studies: TIA with different gain, Gain stage, CSA, test cells ..

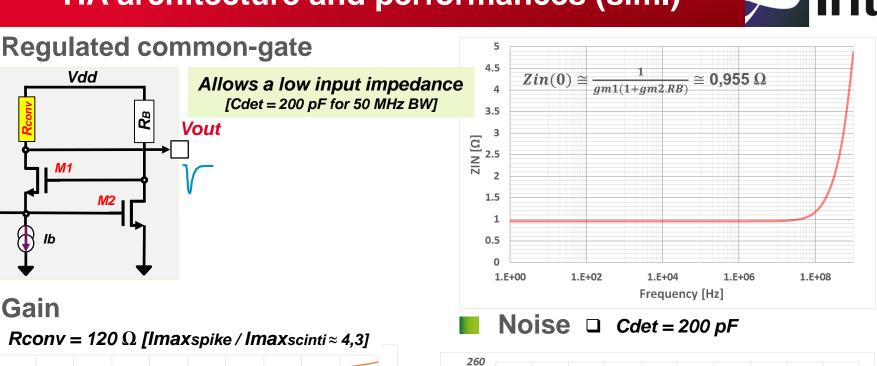

## **TIA** architecture and performances (sim.)

240

220

Noise [MeV] 200 180 140

140

120

100

80

Vdd

M2

**M1**

lb

Gain

**Idet**

CMS ECAL VFE phase II upgrade workshop 11-13 Mai 2016 CEA-Saclay INSTN

TIA solution for VFE upgrade

0

10

20

30

40

50

Ileak [µA]

60

70

80

30MHz

40MHz 50MHz

60MHz

90

100

## G1 and G10 outputs performances (sim)

G1: Transfer function, linearity & Noise

G10: Transfer function, linearity & Noise

CMS ECAL VFE phase II upgrade workshop 11-13 Mai 2016 CEA-Saclay INSTN

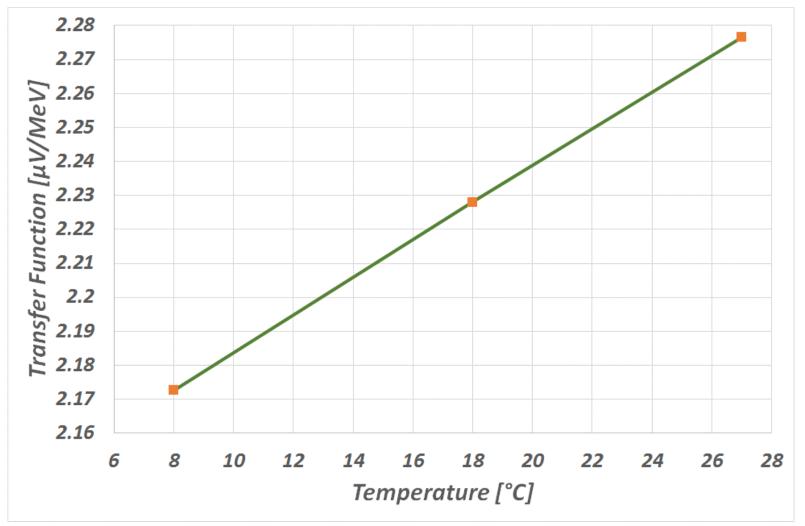

**Transfer function versus Temperature**

□ Gain vs Temperature: + 0.23% /°C [ APD: - 2(3)% /°C]

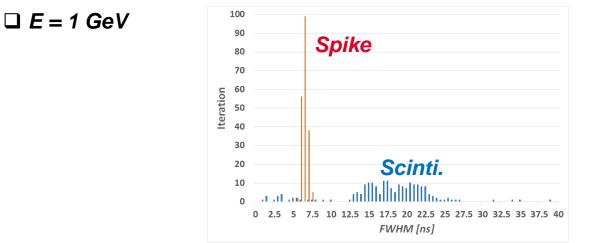

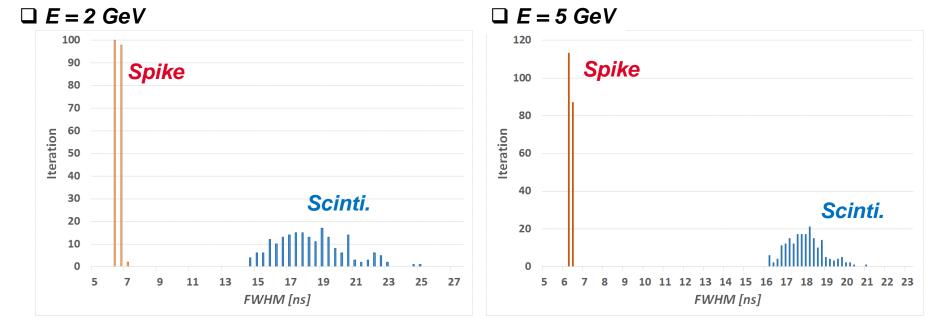

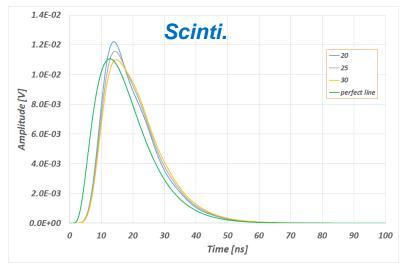

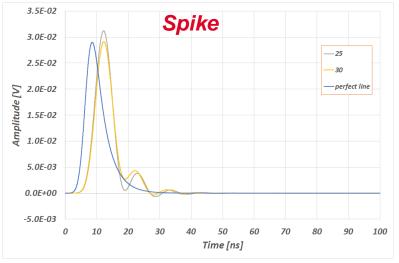

### Spike rejection: lleak = 100 µA; Cdet = 200 pF

CMS ECAL VFE phase II upgrade workshop 11-13 Mai 2016 CEA-Saclay INSTN

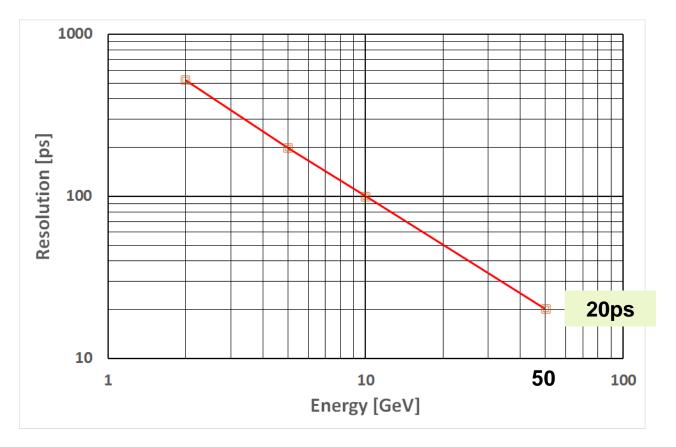

### Time resolution: lleak = 100 μA; Cdet = 200 pF

### Power consumption: 63mW (1.2V)

#### TIA (46mW); G1 (7.9mW); G10 (9.1mW)

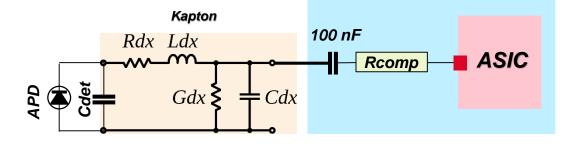

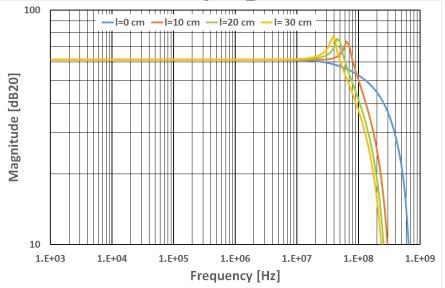

### Interface APD – TIA: strip lines

Measured parameters: L = 3,75 nH/cm; R = 0,05 Ω/cm; C = 2,4 pF/cm

Length 20 - 30 cm => 75 - 100 nH !!

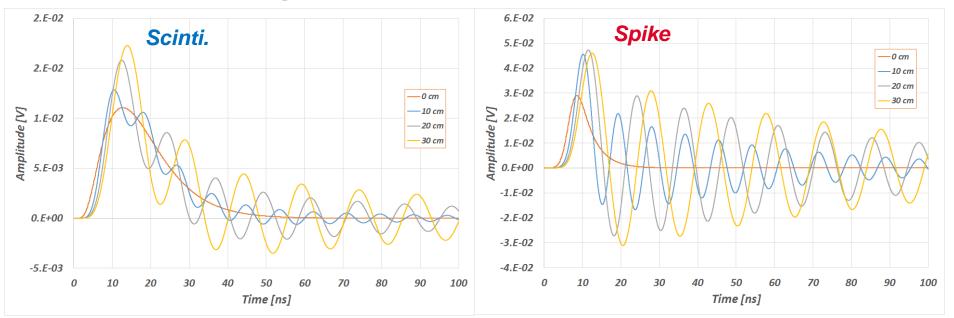

#### **Effect of the length:** Signal E=5GeV

CMS ECAL VFE phase II upgrade workshop 11-13 Mai 2016 CEA-Saclay INSTN

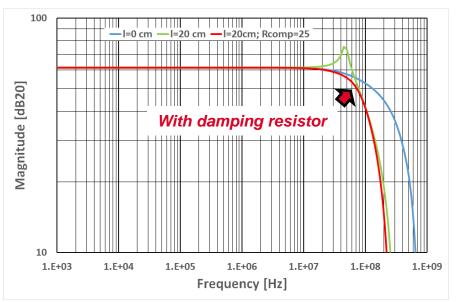

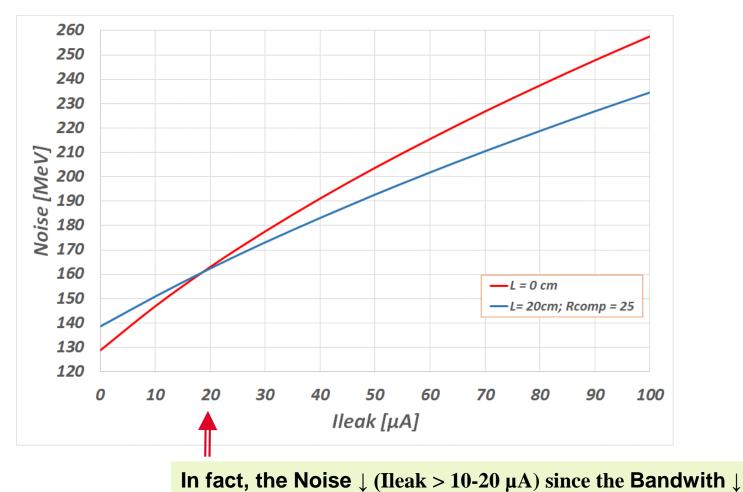

### System performances

#### **Needs damping resistor Rcomp**

#### □ Length: 20 cm

CMS ECAL VFE phase II upgrade workshop 11-13 Mai 2016 CEA-Saclay INSTN

### **System performances**

### Kapton & damping resistor Rcomp

**Drawback:** Noise  $\uparrow$  (@ Ileak = 0  $\mu$ A); Bandwidth  $\downarrow$  => Timing  $\downarrow$

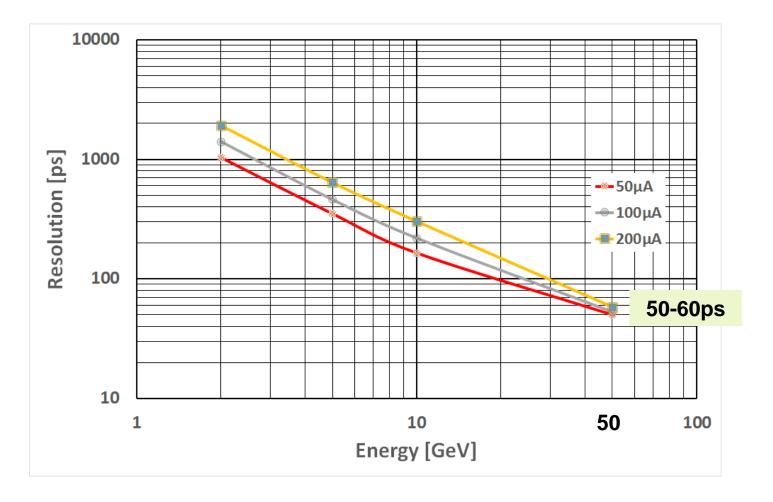

### Charge resolution (G10)

CMS ECAL VFE phase II upgrade workshop 11-13 Mai 2016 CEA-Saclay INSTN

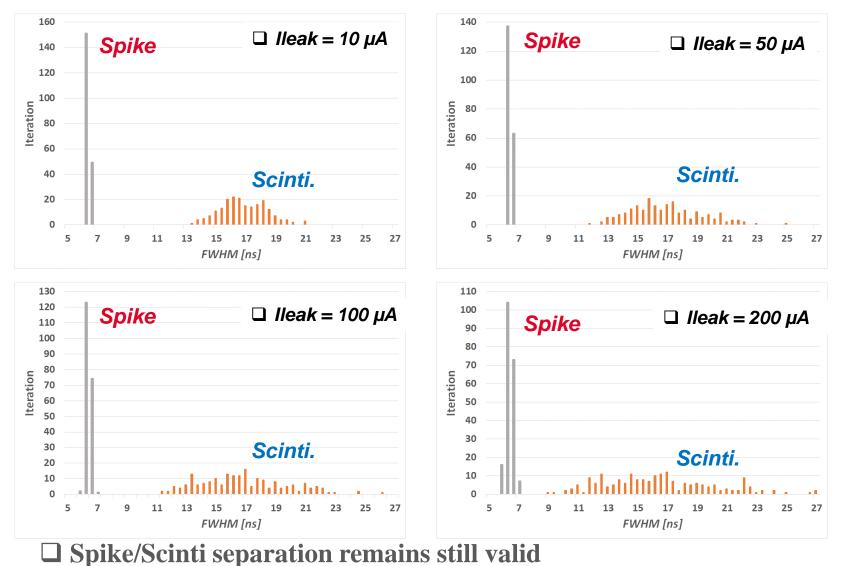

#### Spike/Scinti separation @ 2 GeV for L = 20 cm & Rcomp = 25 $\Omega$

CMS ECAL VFE phase II upgrade workshop 11-13 Mai 2016 CEA-Saclay INSTN

#### **Timing resolution** (L = 20 cm & Rcomp = 25 $\Omega$ )

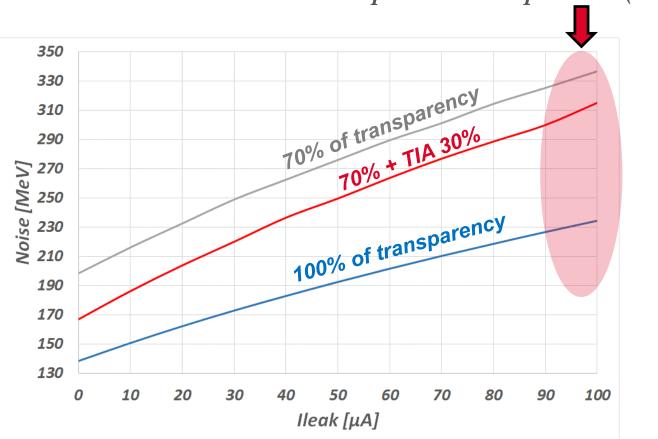

### Crystal transparency loss

**Radiation damage to PbWO4 crystals:**

### 4.5 p.e /MeV to 3 p.e/MeV (- 30%)

**Energy resolution can be improved by increasing Rconv** (+ **30%**)

- The schematic of the global chip is finished at 98%

- The layout has started but we are always waiting the agreement from TMC to

have access to the TSMC Mixed-Signal Design Kit of the CERN

[process started since 19 November 2015..]

Planning: 15 June / 27 July

| TSMC                                                                       | J  | F    | М    | Α     | М     | J    | J    | Α    | S    | 0    | Ν    | D |

|----------------------------------------------------------------------------|----|------|------|-------|-------|------|------|------|------|------|------|---|

| TSMC 0.18 CMOS Logic or Mixed-Signal/RF,<br>General                        | 6  | 3,24 | 9,30 | 13,27 | 11,28 | 8,29 | 6,27 | 3,24 | 7,28 | 5,26 | 2,30 | 7 |

| TSMC 0.18 CMOS High Voltage Mixed-Signal<br>(CV018LD 1.8/3.3/32V)          |    | 9    | 30   |       | 4     |      |      | 3    |      |      |      |   |

| TSMC 0.18 CMOS High Voltage BCD Gen 2<br>(1.8V/5V70V)                      |    | 24   |      |       | 4     |      | 6    |      | 7    |      | 9    |   |

| TSMC 0.13 CMOS Logic or Mixed-Signal/RF,<br>General or Low Power (8-inch)  |    | 9    | 16   |       | 11    | 15   | 27   |      | 7    |      | 9    | 7 |

| TSMC 0.13 CMOS Logic or Mixed-Signal/RF,<br>General or Low Power (12-inch) | 11 |      |      | 13    |       |      | 13   |      | 20   |      |      |   |

- The TIA ASIC is in layout phase

- The performances obtained by simulation are pretty good

- These performances will be degraded by coupling the electronic to the APD through kapton but spike tagging, charge resolution and timing measurement will remain acceptable

- Submission Planning: 15 June or 27 July