# Monitoring Vibrations with an FPGA

Sharon Tseng Christian Faerber LHCb

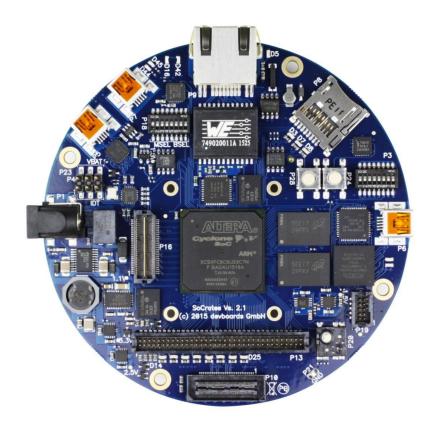

Develop a vibration monitoring system for the hard-disks using vibration sensors, ADCs and a SoC FPGA

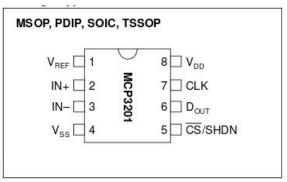

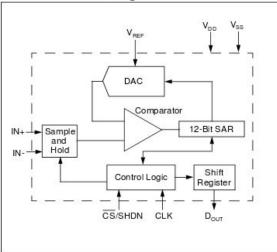

- Communicate with ADC chip via Verilog SPI

- Visual indications with LEDs

- Interface between ARM processor and FPGA fabric

- Communicate with accelerometer using Verilog I<sup>2</sup>C

- Communicate with ADC chip via Verilog SPI

- Visual indications with LEDs

- Interface between ARM processor and FPGA fa

- Communicate with accelerometer using Verilog

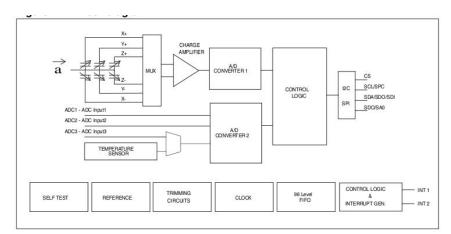

#### Functional Block Diagram

- Communicate with ADC chip via Verilog SPI

- Visual indications with LEDs

- Interface between ARM processor and FPGA fabric

- Communicate with accelerometer using Verilog I<sup>2</sup>C

- Communicate with ADC chip via Verilog SPI

- Visual indications with LEDs

- Interface between ARM processor and FPGA fabric

- Communicate with accelerometer using Verilog I<sup>2</sup>C

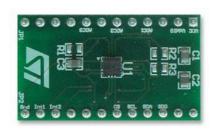

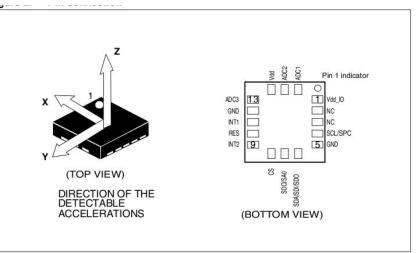

## LIS3DH

- Implementing a sequential communication interface using parallel logic

- Time communications at the right clock cycles

- Testing modules (ModelSim & SignalTap)

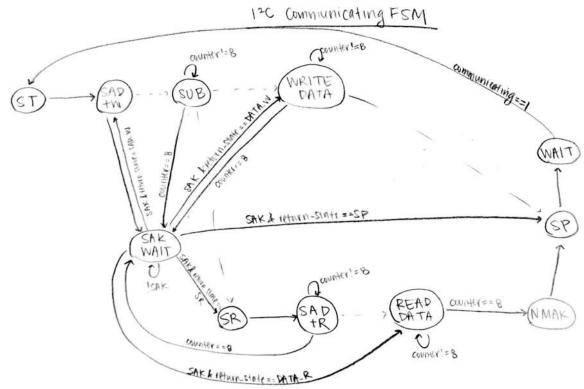

#### FSM Diagrams - Main

12C Main FSM

## I<sup>2</sup>C - Inter-integrated Circuit Protocol

#### Table 15. Transfer when master is receiving (reading) one byte of data from slave:

| Master | ST | SAD + W |     | SUB | *<br>* | SR | SAD + R |     |      | NMAK | SP |

|--------|----|---------|-----|-----|--------|----|---------|-----|------|------|----|

| Slave  |    |         | SAK |     | SAK    |    |         | SAK | DATA |      |    |

#### Table 13. Transfer when master is writing one byte to slave

| Master | ST | SAD + W | 2   | SUB | 2   | DATA |     | SP |

|--------|----|---------|-----|-----|-----|------|-----|----|

| Slave  |    |         | SAK |     | SAK |      | SAK |    |

### FSM Diagrams - Communication

## Questions?