# Beam Wire Scanner (BWS) serial link requirements and architecture

J. Emery for the BWS electronics team

Ad-hoc BI-TB meeting for inter-FPGA communication

29.06.2016

PHASE 2

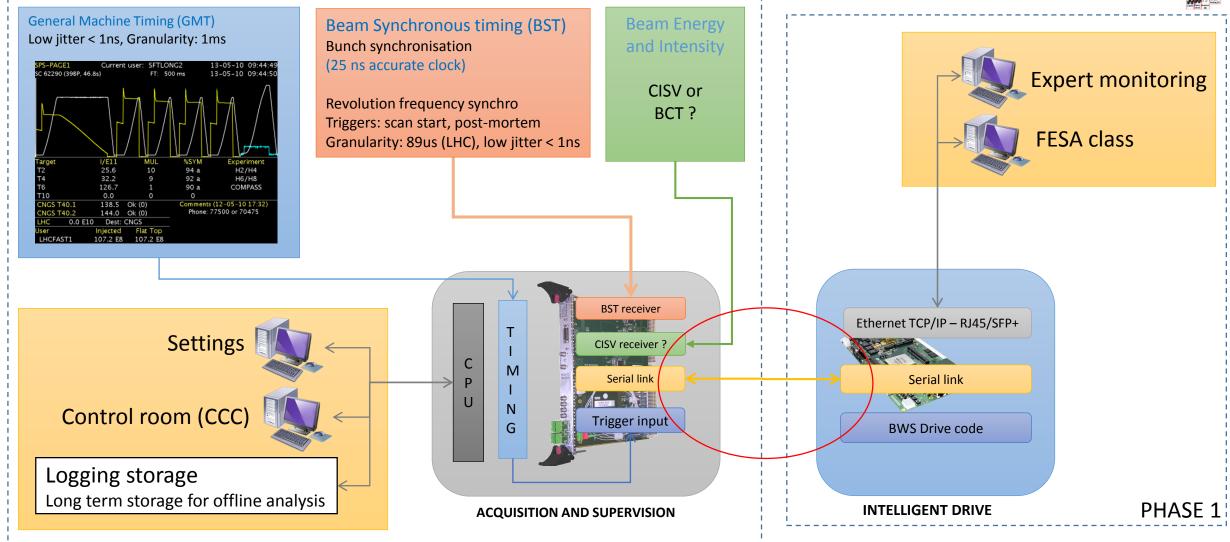

# BWS system connections

# BWS link services requirement list

- Data integrity

Error detection, correction and/or retransmission.

Notification and statistics.

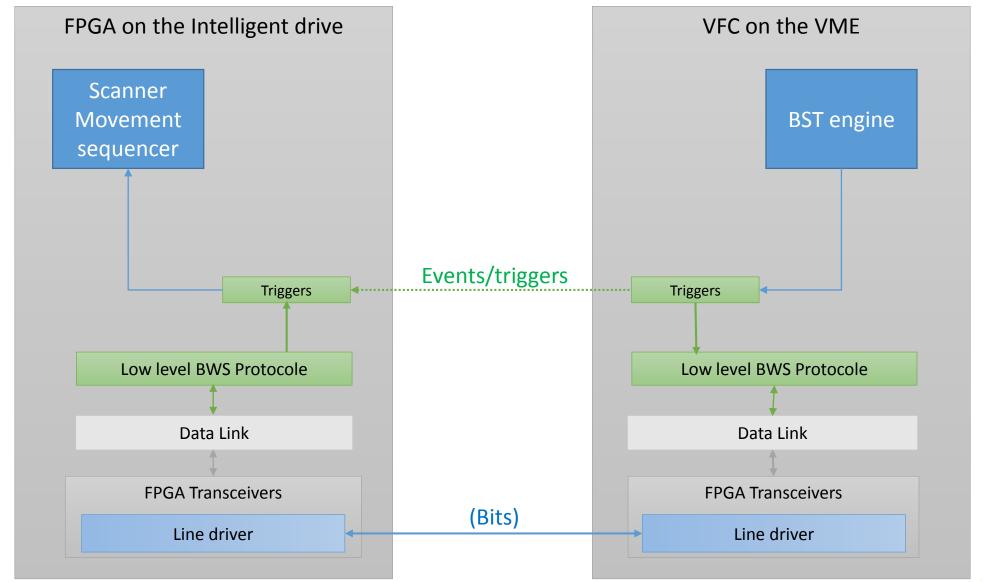

- Event transport Trigger and IO port replication between the 2 ends Link latency jitter < 0.1us, (1km ~5us, Fused Silica 10°C up => +27ps) Automatic transmission time evaluation

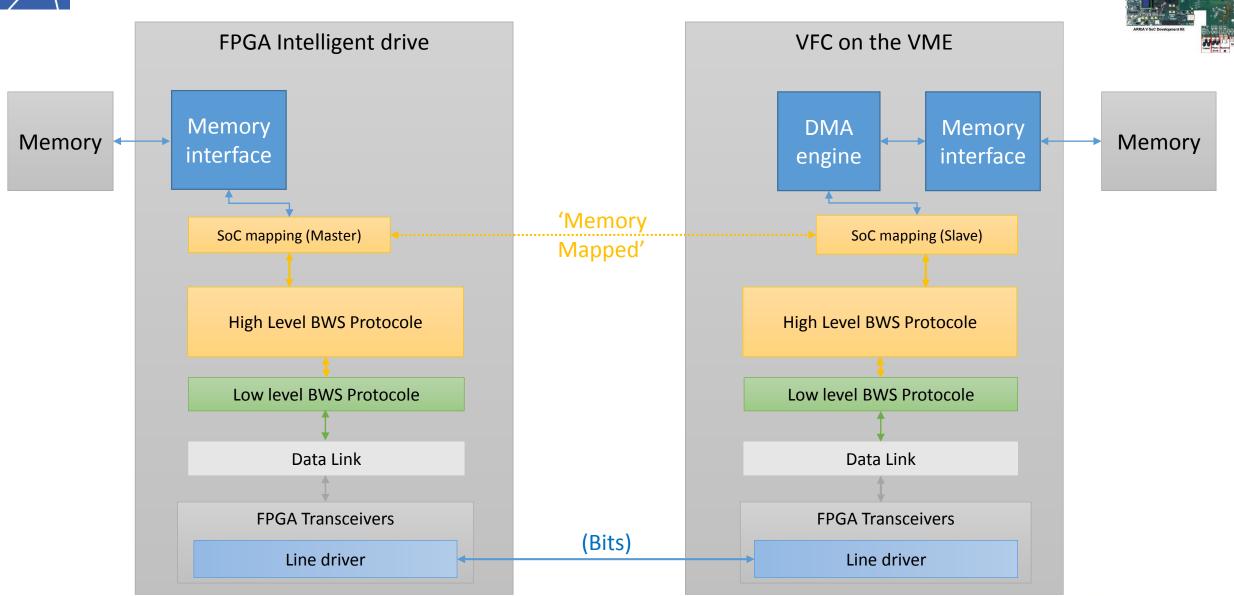

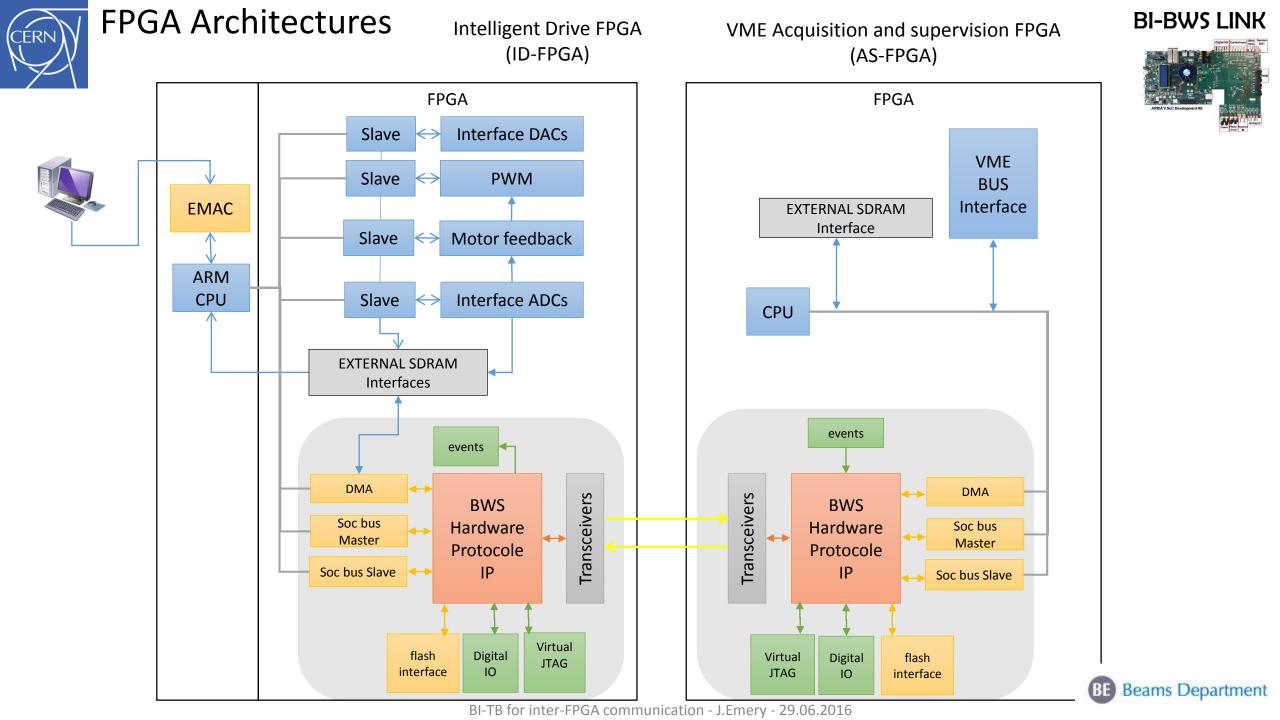

- Transparent interconnect SoC bus Interconnection of internal FPGA bus transparently (Memory Mapping), data blocks transfer between FPGA (2 directions), use of DMA mechanism, etc. PSB >= 118 Mbits/s

- 4) Streaming links Interconnection of internal FPGA bus transparently (Stream interfaces: 1..N @ >= 1Mbit/s) transparent connections for streaming mechanism

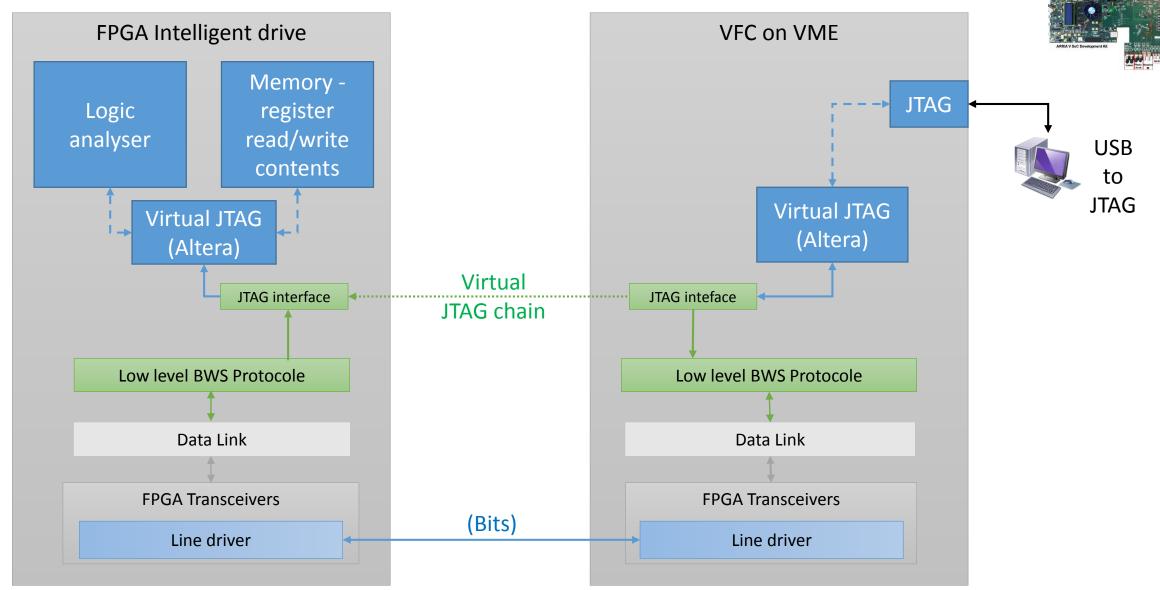

- Virtual JTAG over the link (investigation)

JTAG chain over the link: Use of vendor tool for logic analyser (SignalTap),

memory/register content modification, probing by using Boundary Scan (tbc)

- 6) None-volatile memory management External flash management over the link. Read/write flash of program or settings.

Listed in the technical specification "Beam wire scanner data and events digital link" EDMS 1701798

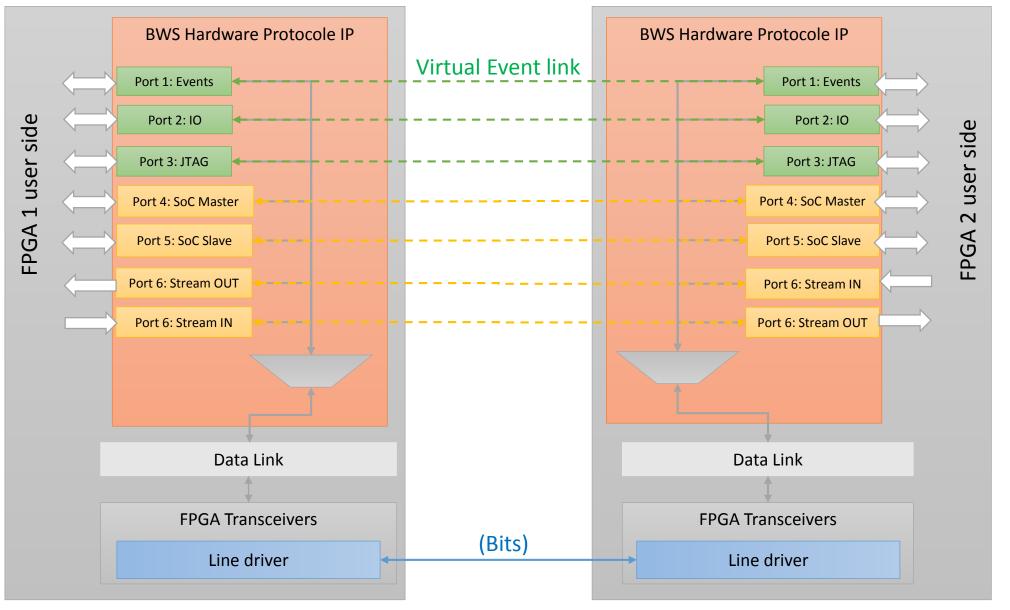

# IP core concept

#### **BI-BWS LINK**

Development scheduled

Could probably be based on GBT layer (tbc)

## Use case: Scanner movement start trigger

## Use case: data collection after a measurement

### Use case: JTAG chain over serial link

# Verification methodology

#### **BI-BWS LINK**

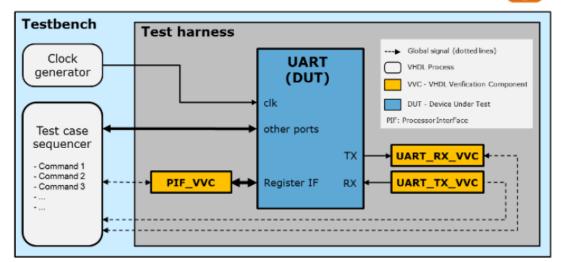

- Management of the complexity

- multiple ports in

- multiple ports out

- priority levels

- Transaction Level Modelling (TLM)

- VHDL 2008 based

- UVVM (Universal VHDL Verification Methodology)

Open source http://bitvis.no/products/uvvm/

- Similar approach that UVM (in systemVerilog)

- Assertions based verification for the interfaces ports

#### **UVVM** - Universal VHDL Verification Methodology

- Master Student will work with me for the implementation and the verification environment (from September 2016)

- Possibility to include additional requirements of potential users

- Master thesis, code and verification environment will be made accessible to users

- Services requirement described for the BWS serial link

- Transport of data and events trough the same channel

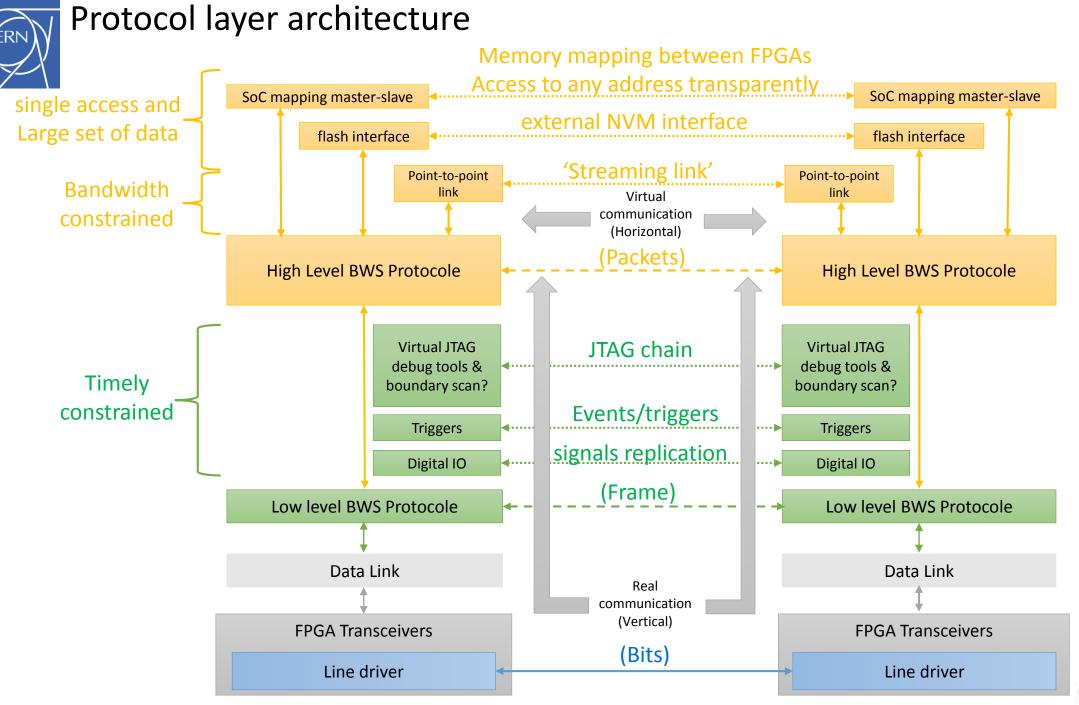

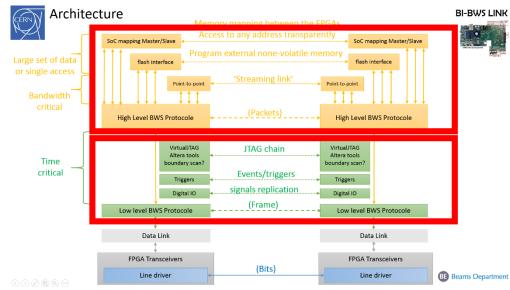

- Based on layered architecture of communication systems

- Low level layer for timely constraints signals, events, IO replication, JTAG

- High level layer for transparent mapping of SoC domains, streaming links

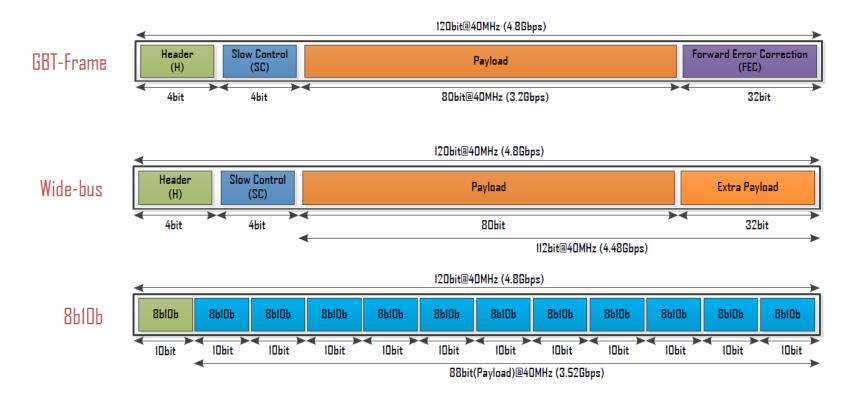

- Physical and data link layer could be using GBT defined protocol (tbc)

Other potential users are welcome to contact me to discuss additional requirements to be include in this implementation

# Additional slides

# The context: "multiple needs" (3 of 5)

## **Multiple Configurations**

Encoding