# An sTGC Prototype Readout System for ATLAS New-Small-Wheel Upgrade

Peng Miao<sup>1,2</sup>,Feng Li<sup>1,2</sup>, ShengQuan Liu<sup>1,2</sup>, ZhiLei Zhang<sup>1,2</sup>,Tianru Geng<sup>1,2</sup>, Xinxin Wang<sup>1,2</sup>, Shuang Zhou<sup>1,2</sup>,Ge Jin<sup>1,2</sup>

1.Modern Physics Department, University of Science and Technology of China (USTC), Hefei, Anhui 230026 China 2.State Key Laboratory of Particle Detection and Electronics, Hefei, Anhui 230026 China Email: mpmp@mail.ustc.edu.cn, peng.miao@cern.ch

#### 1. Introduction

ATLAS will replace the muon end-cap detectors, the so-called Small Wheel(SW), with the New Small Wheel (NSW) in the Phase-I upgrade to enhance its high rate performance. Small-Strip Thin Gap Chambers (sTGCs), developing from the Thin Gap Chamber(TGC) technology but with much smaller strip pitch, have been selected as one of the main detector technologies to be used for the NSW. An sTGC quadruplet consists of four pad-wire-strip planes. To readout sTGC signals, two kinds of Front End Board (FEB) will be designed, pad Front End Board (pFEB) and strip Front End Board (sFEB). The pFEB with the maximum 192 channels is responsible for reading out pad and wire signals of each plane, while the sFEB with the maximum 512 channels is responsible for reading out strip signals of one gas-gap. This paper presents a readout system capable of testing one full-size sTGC quadruplet. It consists of 4 pFEBs and 4 sFEBs along with one specifically designed DAQ board. The FEBs use VMM3 ASIC for analog signal amplification and digitization. The DAQ board is able to configure and readout up to 8 FEBs through Gigabit Ethernet. This readout system can be used to evaluate the functionality and performance of sTGC prototype, and help optimize the design of the final pFEB and sFEB.

Fig.1 pFEB(right) and sFEB(left)

## 2. Readout System Setup

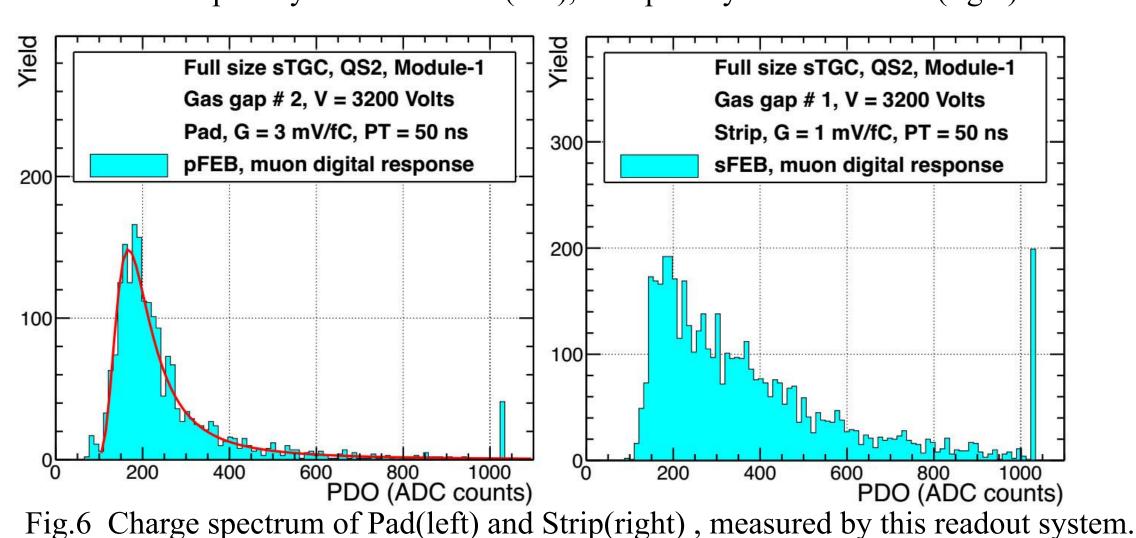

The simplified block diagram of the readout system for one sTGC quadruplet is illustrated in Fig.1.

Each sTGC layer needs one set of pFEB and sFEB. The FEBs receive the charge signals from sTGC detectors through adapt-boards. The digitized amplitude value will be read out by a specifically designed DAQ board. This DAQ board is also responsible for configuring FEBs. The Graphical User Interface running on the host downloads command and configuration data to DAQ board and reads back packaged event data from DAQ board via Gigabit Ethernet.

Fig.2 Schematic of the readout system for sTGC prototype

The region of interest of sTGC detectors is sandwiched between two layers of scintillator arrays. And there is a PMT for capturing photons from each scintillator array. The Coincidence and Trigger Unit receiving the signals from two PMT generates trigger signals for the whole system when a muon goes through the sTGC quadruplet. Once triggered, the DAQ board will fan out the trigger signals to all FEBs through the control path.

### 3. Design of DAQ Board

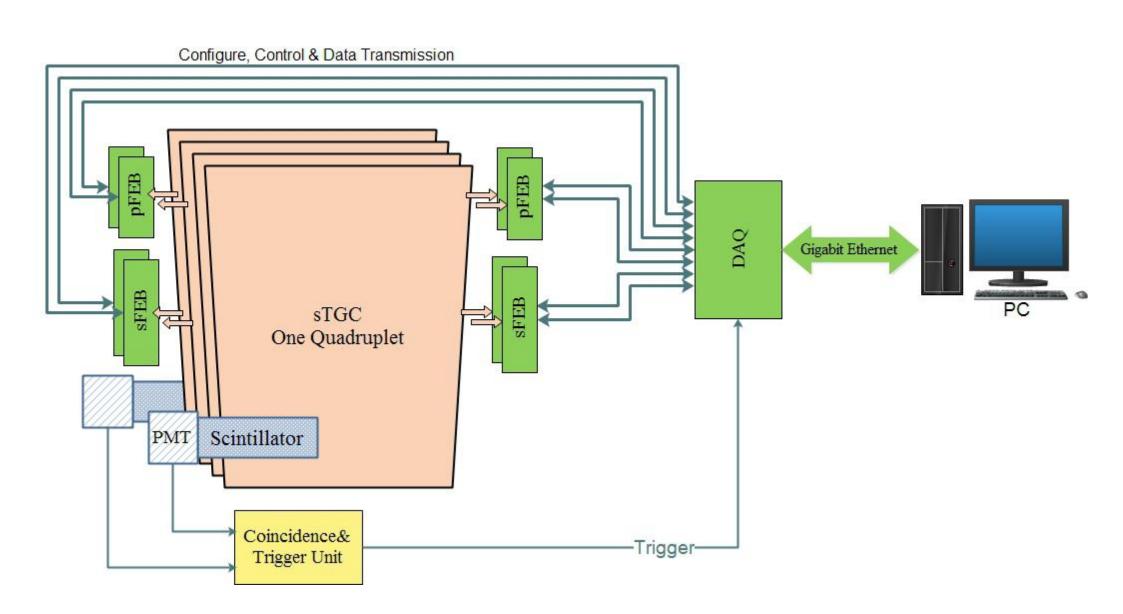

Fig.3 shows the block diagram of the specifically designed DAQ board for this readout system. There are three relatively independent paths between FEBs and DAQ board, and they are control path, configuration path and data path.

Fig.3 Block diagram of the specifically designed DAQ board.

Fig.4 Picture of the DAQ board.

The Timing-Trigger-Control (TTC) module is the key component of the control path. The TTC module has three main tasks: global clock fan-out, trigger signal fan-out and system synchronization signals fan-out.

The FEBs are all configured by the Slow Control Adapter ASIC (SCA), which is designed to provide several protocols for front-end configuration. The SCA chips on the front-end boards communicate with DAQ board through Elink, a full duplex serial interface, and based on the HDLC standard. To deal with the complex HDLC protocol, a CPU/FPGA hybrid architecture is implemented, which significantly simplifies the FPGA firmware and makes the entire system much more reliable. The FPGA focuses on the high-speed HDLC frame reception and transmission, while the CPU concentrates on the complicated SCA commands parsing.

The data capture core in the data path performs 8b/10b decoding and data packaging. And then the Ethernet core uploads buffered data from eight separated FIFOs in a round-robin manner to PC for future analysis.

#### 4. Results and Conclusion

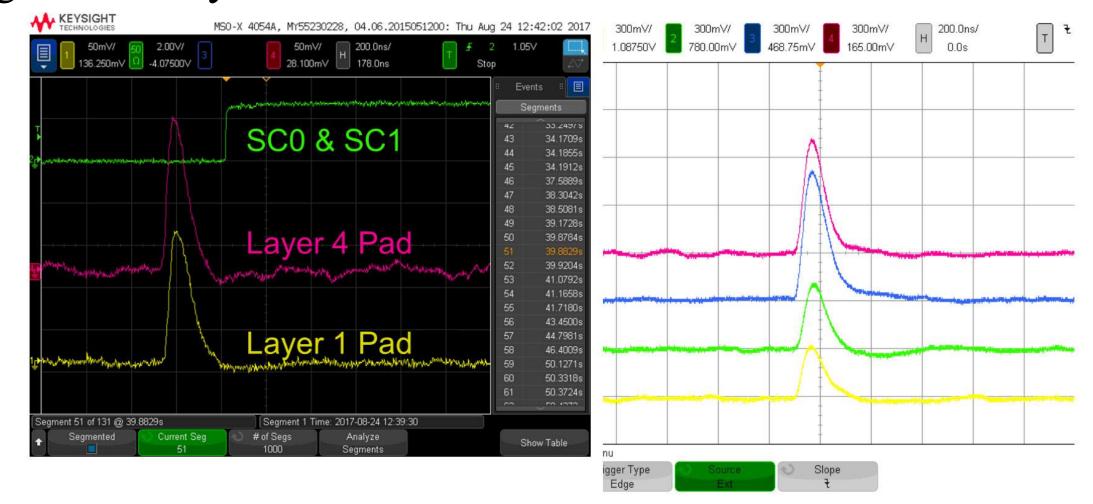

This readout system has been successfully used to test sTGC prototype at ShanDong University in China and Weizmann Institute of Science in Israel.

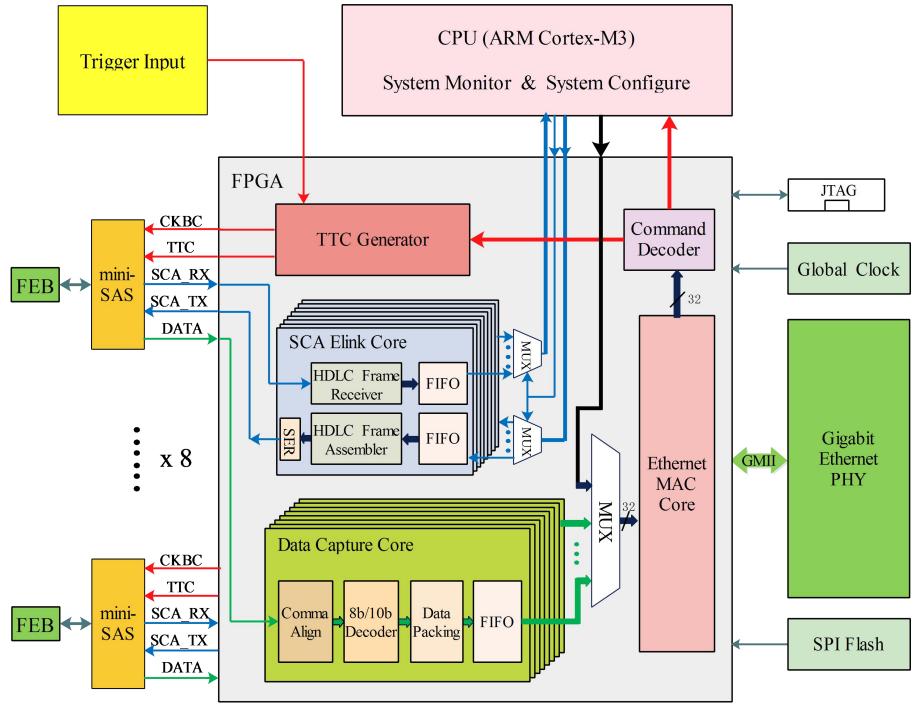

Fig.5 Multi-layer coincidence with cosmic muon triggers

Two pad layers coincidence(left), four pad layers coincidence(right).