# FPGA acceleration of Model Predictive Control for ITER Plasma current and shape control

Samo Gerkšiča, Boštjan Pregelja, Matija Perne

# Overview

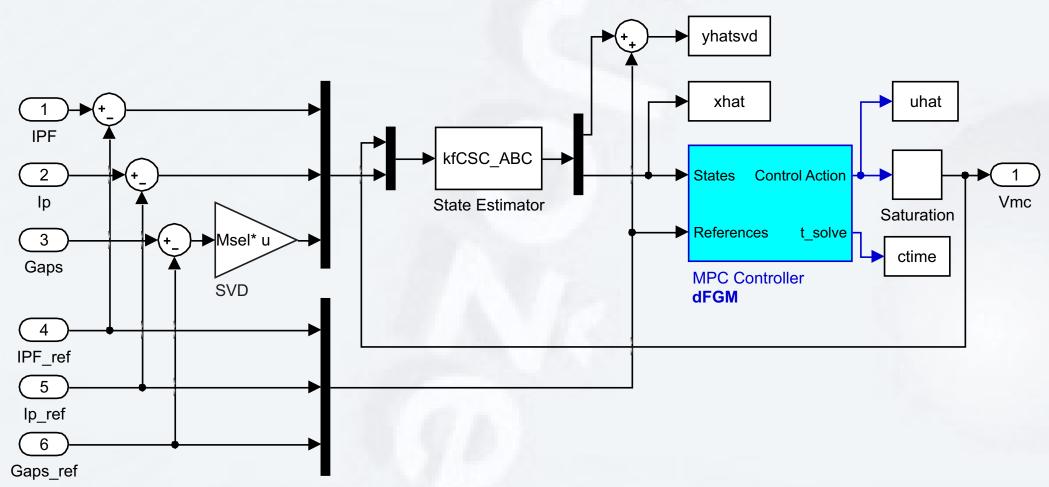

- Plasma Current and Shape Controller (PCSC) for ITER

- Singular Value Decomposition (SVD) -based Model Predictive Control (MPC) using a dual Fast Gradient Method (dFGM) quadratic programming (QP) solver

- FPGA acceleration with a High-Level Synthesis (HLS) approach

SVD-based fast MPC PCSC block scheme

#### **Model Predictive Control (MPC)**

MPC is an advanced model-based process control technique, based on on-line optimization of predicted future courses of the process signals. Typically, a simplified control model in the discrete-time linear state space form is used, and the MPC controller is used in conjunction with a Kalman state estimator. It is closely related to LQ (linear quadratic) optimal control, and is convenient for control of multivariable processes such as PCSC. It is efficient in handling of constraints - in the case of ITER PCSC:

- input constraints of the power supply voltages **V**<sub>PF</sub>

- output constraints of the superconductive coil currents  $\mathbf{I}_{PF}$ .

# **Solving QP problems for MPC using dFGM**

In MPC, a QP optimisation problem must be solved in each time step of the algorithm, which is difficult with large-scale multivariable systems with fast dynamics. Using complexity reduction techniques for MPC and C code optimisation, with the dFGM algorithm the required accuracy was achieved in 500 iterations with peak computation times 3 ms using a standard Intel x86 CPU using a single thread. This is considered sufficiently fast for ITER, but not for experimantation on smaller tokamaks with faster dynamics. The execution of the dFGM algorithm may be accelerated by parallelisation of matrix-vector numerical operations within iterations, but this is not well-suited for the standard CPU architecture with the thread scheduler timescale 10  $\mu$ s, thread synchronisation takes more time than computation.

# **FPGA** implementation

FPGA implementation supports small-scale paralellism, but they have other issues regarding the implementation of complex algorithms: relatively low clock frequencies, limited resources for massive parallelism, specific programming. Aiming to avoid manual recoding as much as possible, the High-Level Synthesis (HLS) approach of Xilinx Vivado HLS was adopted:

- C code (simplifications required: static allocation of variables, direct implementation of functions)

- emulated single float precision (multiple cycles/operation)

- conversion directives (pragma commands) to the VHDL compiler for more optimized implementation:

- pipeline, loop unroll, loop merge, array partition

- hardware: Xilinx Zedboard, Zc706

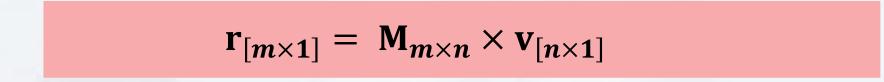

The dFGM main iteration loop must be optimized for speed. Its computational load is dominated by two matrix-vector multiplications (33x99 \* 99 and 99x33 \* 33), while other vector operations represent less than 10% of the workload.

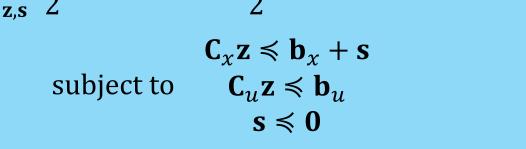

# $\min_{\mathbf{z}} \frac{1}{2} \mathbf{z}^T \mathbf{H} \mathbf{z} + \mathbf{c}^T \mathbf{z}$ subject to $Cz \leq b$ MPC QP, soft state constraints $\min_{\mathbf{z}} \frac{1}{2} \mathbf{z}^T \mathbf{H} \mathbf{z} + \mathbf{c}^T \mathbf{z} + \frac{1}{2} \mathbf{s}^T \mathbf{W} \mathbf{s} + \mathbf{w}^T \mathbf{s}$

**MPC QP, hard constraints**

$\mathbf{C} = \begin{bmatrix} \mathbf{C}_{\chi} \\ \mathbf{C}_{\chi} \end{bmatrix}, \ \mathbf{b} = \begin{bmatrix} \mathbf{b}_{\chi} \\ \mathbf{b}_{\chi} \end{bmatrix}$

# **Dual FGM algorithm**

$$\mathbf{v}^{k} = \mathbf{v}^{k} + \beta^{k} (\mathbf{v}^{k} - \mathbf{v}^{k-1})$$

$$\mathbf{y}^{k} = -\mathbf{H}^{-1} (\mathbf{C}^{T} \mathbf{v}^{k} + \mathbf{c})$$

$$\mathbf{v}^{k+1} = \mathbf{v}^{k} + \mathbf{C} \mathbf{y}^{k} - \widehat{\text{prox}}_{h,\mathbf{W},\mathbf{w}} (\mathbf{v}^{k} + \mathbf{C} \mathbf{y}^{k})$$

$$\widehat{\text{prox}}_{h,\mathbf{W},\mathbf{w}} (\mathbf{t})_{i} = \begin{cases} t_{i} & \text{if } t_{i} \leq b_{i} \\ b_{i} & \text{if } t_{i} > b_{i} \text{ and } i \text{ hard} \\ b_{i} & \text{if } b_{i} + w_{i} \geq t_{i} > b_{i} \text{ and } i \text{ soft} \end{cases}$$

$$\frac{t_{i} + W_{ii}b_{i} - w_{i}}{W_{ii} + 1} \quad \text{if } b_{i} + w_{i} < t_{i} \text{ and } i \text{ soft}$$

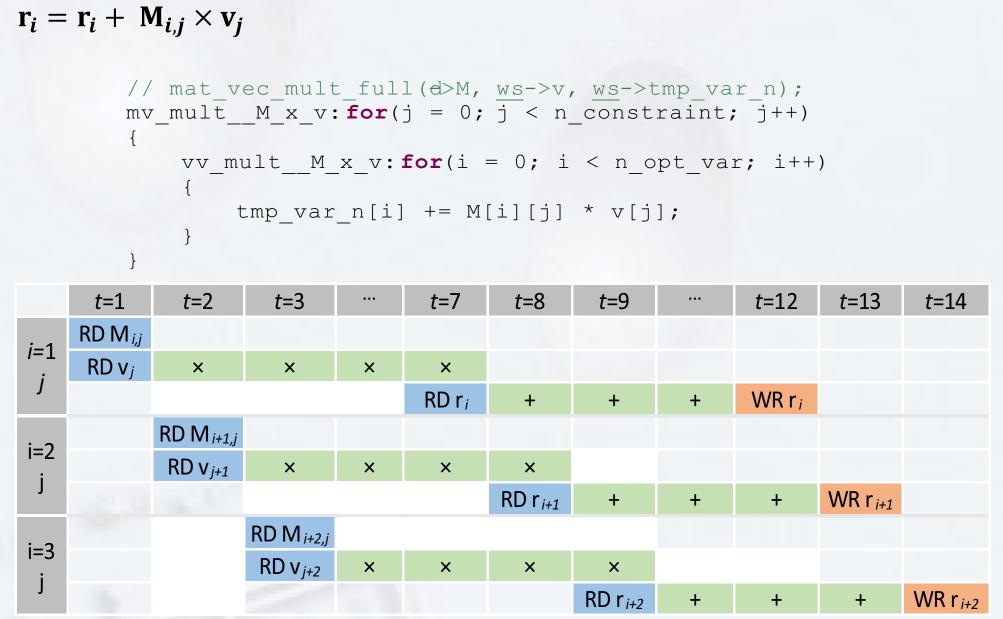

#### **Matrix-vector multiplication implementation**

# Approach 1 (initial)

Time schedule for parts  $\mathbf{M}_{i,j} \times \mathbf{v}_i$  of  $\mathbf{M} \times \mathbf{v}$  product.

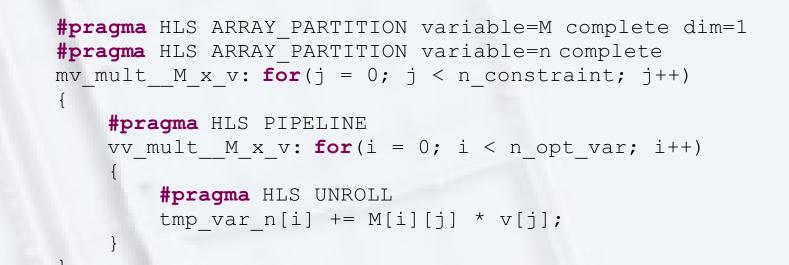

# Approach 2 (inner loop unroll)

Unroll the inner i loop (dimension m) Partition M (dimension m) Partition  $\mathbf{r}$  (dimension m) Pipeline the outer *j* loop

Timing schedule of **M**×**v** product, with parallelized inner loop.

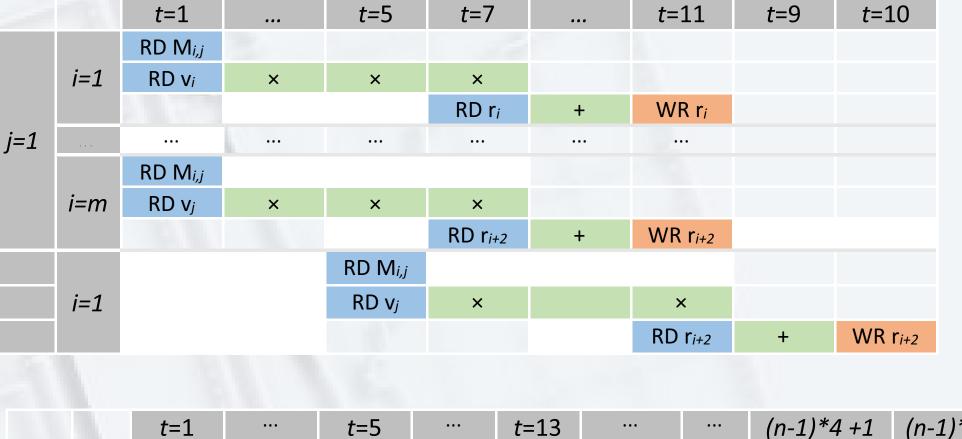

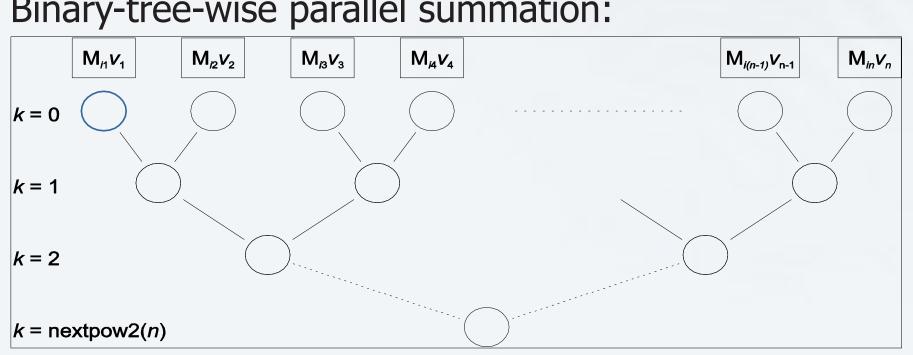

# Approach 3 (scalar product tree-sum)

Jozef Stefan Institute, Jamova cesta 39, 1000 Ljubljana, Slovenia

Multiplication as series of scalar products:

Parallelized calculation of vector scalar product (mat Nik x hin).e

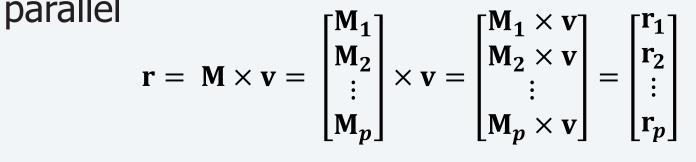

#### **Approach 4 (tall matrix truncation)**

Vertically divide M into p wide matrices  $M_1, ..., M_p$  and process them in parallel

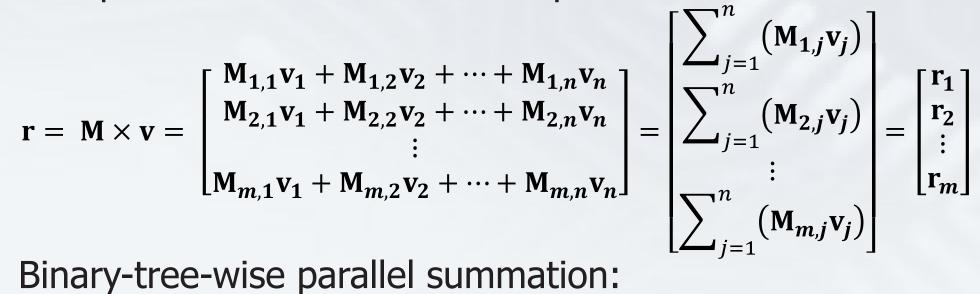

# Matrix-vector multiplication operation count (in clock cycles)

| Status                  | Iteration*<br>latency (Lat) | Initiation*<br>Interval (II) | Iteration*<br>count (It) | Total latency<br>(It*II + Lat) |

|-------------------------|-----------------------------|------------------------------|--------------------------|--------------------------------|

| Iinitial                | m                           | m +3                         | n                        | n*(m+3) (+n**)                 |

| nner unroll             | 12                          | 4                            | n                        | n* 4 + 12                      |

| Scalar product tree-sum | 32                          | 1                            | m                        | m + 32                         |

| Tall matrix truncation  | 32                          | 1                            | m/p                      | <i>m/p</i> + 32                |

<sup>\*\*</sup> The additional n clocks are required to enter the inner loop n-times. This is handled using loop flatten

# **Conclusions**

\*The parameters are stated for the outer loop

The automatic conversion does not yield useful results from the original C code, because the code structure prevents automated application of conversion optimization routines, so that the execution time is 45 ms, which is much longer than the CPU implementation, with low use of resources

After a series of manual modifications of the code with pragma directions, the computation time for Xilinx ZC706 is reduced to 1 ms (3x faster than CPU).

Further acceleration is presumably possible by using a FPGA with hardware flow-point multipliers, or by using fixed-point arithmetics (lower dynamic range)