# I2C Management Based on IPbus

Author:Luo Shiyu

Speaker: Yu Hongwei

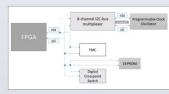

Fig. 1 I2C device connection diagram

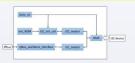

Fig. 2 Logical connection diagram

# Poster

## **I2C Managenent Base on IPbus**

Shiyu Luo<sup>1,2</sup>, Junfeng Yang<sup>1,2</sup>, Kezhu Song<sup>1,2</sup>, Hongwei Yu<sup>1,2</sup>, Tengfei Chen<sup>1,2</sup>, Tianbo Xu<sup>1,2</sup>

1. State Key Laboratory of Particle Detection and Electronics, University of Science and Technology of China, Hefei, 230026, China

2. Department of Modern Physics, University of Science and Technology of China, Hefei, 230026, China

# Introduction

### 1. Introduction

The CBM experiment are composed of kinds of detectors, including Micro Vertex Detector (MVD), Silicon Tracking System (STS), Muon Chamber (MUCH), Ring Imaging Cherenkov Detector (RICH), Transition Radiation Detector (TRD), Time of Flight Detector (TOF), and Projectile Spectator Detector (FED). All these detectors are equipped with the appropriate Front End Electronics (FEE) boards and Readout Boards (ROB) which are located near to the detectors in the irradiated area.

Before the next generation GBTx based CBM DAQ system is built up, the data from the FEE and ROB are injected into a separate intermediate layer named DPB layer, where more complex functionalities, such as slow control, time synchronization, data readout, data pre-process and data format converting, are implemented. In current CBM DAQ architecture, all these functions will be implemented in a Field Programmable Gate Array (FPGA). Considering the optimal balance between the cost and performance, a versatile FPGA-based platform, the AMC FMC Carrier Kintex (AFCK) is used in kinds of the DPB projects to support different detectors.

### 2. System architecture

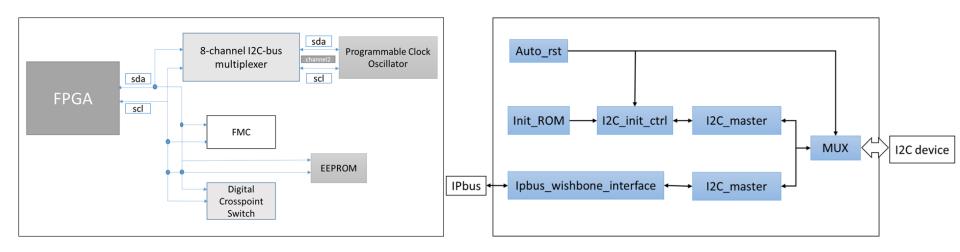

On AFCK, a set of 12C devices can be configured from the Module Management Controller (MMC) software or from the FPGA, including: 12C bus multiplexer, Clock crosspoint switch, Programmable Clock, 12C serial EEPROM with a EUI-48 address, System Monitor Ics, and Other 12C devices.

Figure 1. I2C connection diagram

Although these I2C devices can be configured via MMC when power up, it is important for DAQ system that all these I2C devices can be on-line configured via the slow control bus. In CBM DAQ, the slow control is based on IPBus, an open-source FPGA core which controls a Wishbone-like bus via Ethernet with fully dedicated software package (c+++ or Python). But the settings of IPBus depends on the correct configuration of related I2C devices, including the I2C-bus multiplexer (choosing correct I2C bus), the clock crosspoint switch, the serial EEPROM with a EUL-48 address (providing the AFCK MAC address), which must be configured before the IPBus can be used. Hence a stand-alone, FPGA-based, programmable I2C configuration module is needed to implement the basic I2C initialization when power-up. After the IPBus link is setup, an IPBus I2C slave will fulfill the control needs for all the I2C devices connected. All these two parts consist the I2C management module for CBM DPB layers.

### 3. Ipbus I2C ctrl Module

As shown in Figure 2, there are two I2C controller in the module, one is for I2C device initialization, the other is for the in-system operation on I2C device via IPbus. There is an automatical reset submodule, in which the reset signal will be asserted when power-up. This reset signal will trigger the I2C device initialization module, in which a set of I2C configuration command stored in a ROM can be read out one by one and be sent to the appointed I2C buses.

Figure 2. Logical connection diagram

After the 12C device initialization is finished, the 12C controller switches to the 1Pbus-based 12C controller automatically. The 12C controller in ipbus 12c crit core is an 12C master with WISHBONE interface, so it can be easily either accessed directly or connected to 1Pbus. A set of use-defined i2C configuration commands are used in the 12C device initialization. These commands should be saved in a ROM and be read out one by one by the 12C device initialization module. At the same time, the i2C device initialization module supports the input and output port for comblex 12C configuration.

### 4. I2C init ctrl Module

The initialization controller module is controlled by a state machine. The state machine consists of a total of 11 states. The command is read in the initialization module ROM. When the Ith bit of the instruction is logic 0, the state of the state machine will be transferred from READ\_ROM to READ\_WRITE\_REG, and then to CMD\_END. According to the register port part of the command, the corresponding register in the 12C core is read or written. The specific state transition diagram is shown in Figure 2. When the Ith bit of the command is logical one, different operations are performed according to the register port portion of the command.

Figure 3. Initialize module state transition diagram.

### 5. Software and ROM command file programming

Before initialization, the programmable crystal oscillator is not connected to the FPGA. So the initialization module needs a separate clock to drive it. After initialization, the system clock will connect to FPGA, and the IPBUS control module is driven by the system clock.

### 6.Conclusion

The initialization control module can complete the configuration of some 12C devices. However, some 12C devices need to be configured in real time, so it is necessary to use IPbus to configure 12C devices online. The 12C device can establish connection with IPbus only after the initialization is completed. Therefore, the configuration of the 12C device on the AFCK board can be completed only when two configuration modules are used together.

Hardware and logic architecture