# Radiation-Tolerant, High-speed Serial Link Design with SRAM-based FPGAs

R. Giordano, <u>S. Perrella</u>

21st IEEE Real Time Conference – Williamsburg, Virginia, USA

# Radiation-Tolerant, High-speed Serial Link Design with SRAM-based FPGAs

R. Giordano, <u>S. Perrella</u>

- High-speed serial links implemented by means of SRAM-based FPGAs usually used only offdetector

- mostly due to FPGA sensitivity to radiation-induced single event effects

- This work is about a radiation-tolerant link running @6.25 Gbps in a Xilinx 7-Series FPGA

- Adaptive, FEC line code protects data

- Triple Modular Redundancy protects critical logic blocks

- Scrubber protects configuration

## Radiation-Tolerant, High-speed Serial Link Design with SRAM-based FPGAs

R. Giordano, <u>S. Perrella</u>

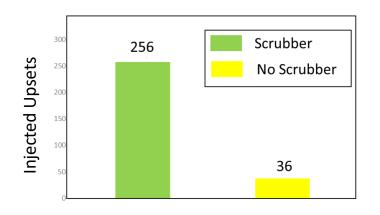

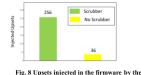

- Results from a fault-injection test

- The link corrects the maximum bursterrors compatible with the line code protection level

- The link recovers from losses of locks in spite of the injected errors when the scrubber is active

- # of injected upsets before failure is 7x higher when the scrubber is operating

Motivation and Overview of the Radiation-Tolerant Link

Details on System and its implementation on Xilinx FPGAs

Description of the fault injection test and of preliminary results

#562

## Radiation-Tolerant, High-speed Serial Link **Design with SRAM-based FPGAs**

R. Giordano<sup>1</sup>, S. Perrella<sup>1</sup> (sabrina.perrella@na.infn.it)

Università di Napoli "Federico II", I-80126 Napoli, Italy and INFN Sezione di Napoli, I-80126, Napoli, Italy

In the field of High Energy Physics experiments, high-speed serial links implemented on SRAM-based FPGAs have been extensively used in the trigger and data acquisition systems Their application has been usually limited to the off-detector electronics, due to SRAM-based FPGA susceptibility to ionizing radiation effects.

However, in order to use these devices in radiation environments, dedicated mitigatio techniques can be adopted

- information redundancy (typical of error correcting codes) hardware redundancy, such as triple modular redundancy (TMR)

- configuration scrubbing.

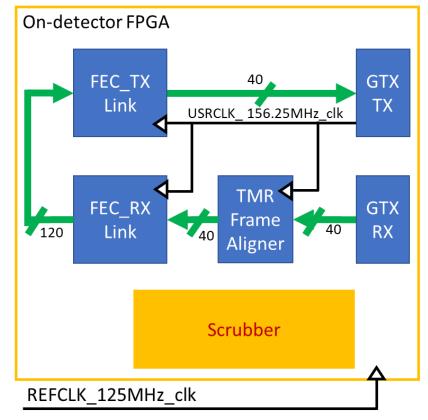

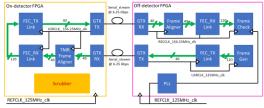

In this paper, we present a serial link running at 6.25 Gbps implemented in a Xilinx Kintex-FPGA which is protected against radiation effects by means of all the above-mentioned methods (Fig. 1).

Fig. 1 Simplified Block Diagram of the Radiation Tolerant Link.

#### 1. Link Architecture

- · Self-synchronizing scrambler for data randomization

- · Reed-Solomon encoder/decoder, whose error correction capability is increased adopting the Interleaving

- · Adaptive Reed-Solomon code to cone with different FEC rates of radiation-induced faults, trading the available [0] bandwidth for data redundancy

- · TMR replicas (Synplify Premier tool [1]) of alignment circuit for masking error before scrubbing correction

- · Scrubber for repairing corrupted

Fig. 3 Block Diagram of the Scrubber

### 2. Implementation & Replication

- · Both the on-detector and the off-detector Link have been implemented in Xilinx Kintex-7 FPGAs whose embedded GTX transceivers support data rates up to 10.3125 Gbps.

- The configuration of the on-detector link node (i.e. intended to be used in radiation areas) has been protected.

- · The project summary of the resources utilization is shown in Table 1.

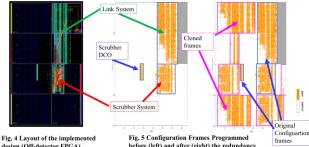

- · The project occupation on the FPGA device is shown on in Fig. 5 · In Fig. 7 the configuration occupation of the project before and after the replication of the configuration frames.

|               | Slice LUTs<br>(41000) | Slice Registers<br>(82000) | Sice<br>(10250) |          |          |

|---------------|-----------------------|----------------------------|-----------------|----------|----------|

| KLinkScrubber | 7057 (17.2%)          | 3450 (4.2%)                | 2091 (20.4%)    | 4[12.5%] | 5 (1.8%) |

|               |                       |                            |                 |          |          |

|               | 5460 (13.3%)          | 1970 (2.4%)                | 1481(14.5%)     | 2(6.3%)  | 3 (1%)   |

|               | 261 (0.6%)            | 310 (0.4%)                 | 132 (1.3%)      | 1 (3.1%) | 0 (0%)   |

| TX_Link       | 1396 (3.4%)           | 367 (0.5%)                 | 139 (3.9%)      | 0 (0%)   | 0 (0%)   |

| RX_Link       | 3032 (7.4%)           | 730 (0.9%)                 | 799 (7.8%)      | 0 (0%)   | 0 (0%)   |

| frame_Aligner | 774 (1.9%)            | 558 (0.7%)                 | 217 (2.1%)      | 0 (0%)   | 0 (0%)   |

|               |                       |                            |                 |          |          |

| bbar          | 1502/3 660            | 149001 990                 | 610 (650)       | 266.287  | 202.050  |

Table 1 Resources Utilization

design (Off-detector FPGA).

before (left) and after (right) the redundancy (on-detector FPGA)

### 4. Test Results

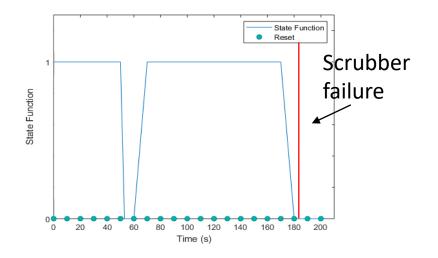

#### The Link has been tested with or without scrubbing

. Fig. 7 shows the state function of the link when scrubber is active.

In Fig. 8 the upsets injected in the configuration before failure w/ and w/out scrubbing

Fig. 7 State Function of the on detector link.

firmware before failure

This work is part of the ROAL project (grant no. RBSI14JOUV) funded by the Scientific Independence of Young Researchers (SIR) 2014 program of the Italian Ministry of Education, University and Research (MIUR)

### 3. Fault InjectionTest

Remote Link firmware

- · Test with a Fault Injector software. · Custom DUT board FPGA loaded with

- · Tester board (Xilinx KC705) with the Local link firmware with a frame checker for the verification of the DUT output

- · Multichannel Power Analyzer (PA) powers DUT board.

- · Test controller logs upsets from scrubber, functionality test results from tester board and power logs from PA.

- · PC inject error on essential bits via JTAG

[1] Synplify Pro and Premier. Synopsys, Inc. Mountain View, Calif. (USA), 2015 [Online]. Available: https://www.synopsys.com/content/dam/synopsys/implementation&signoff/datashe [2] R. Giordano et al. IEEE Trans. on Nucl. Sci., vol. 64, no. 9, pp. 2497-2504, Sept. 2017

[3] R. Giordano et al. "Self-Contained Configuration Scrubbing in Xilinx FPGAs for On-detector Applications PM2018, Conference Proceeding, Pisa, 2018. [4] R. Giordano et al. IEEE Trans. on Nucl. Sci., vol. 64, no. 9, pp. 2497.