# **#545 Design and development of the DAQ and Timing Hub for CMS Phase-2**

#### The DAQ and Timing Hub for CMS Phase-2

21st IEEE Real Time Conference, Colonial Williamsburg, VA USA, 9-15 June 2018 CMS DAQ group, presented by J.Hegeman and F.Meijers CERN EP/CMD

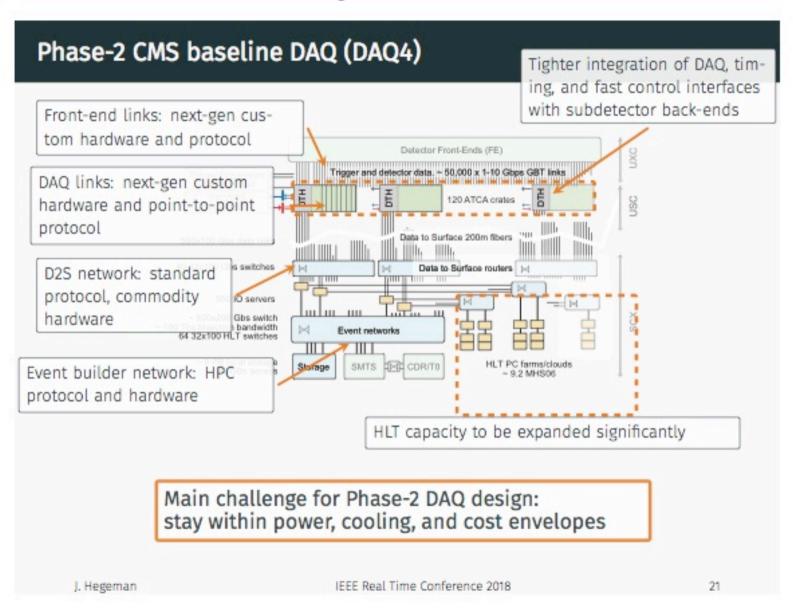

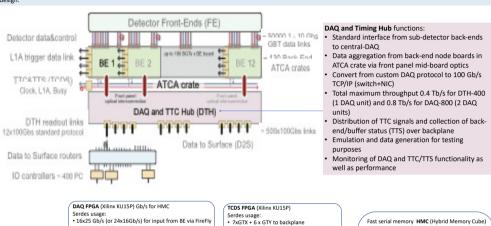

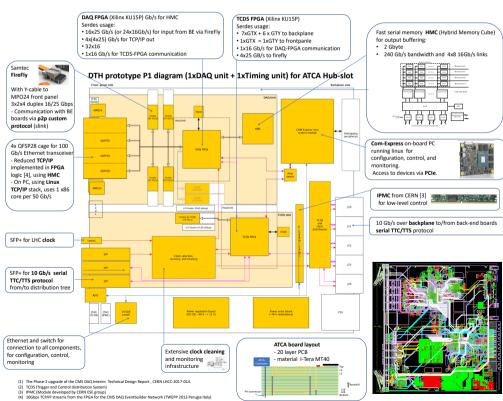

ABSTRACT: The CMS Detector will undergo a major upgrade for the Phase-2 of the LHC physics program, which will start around 2026. The detector will be read out at a rate of 750 kHz by some 50k high-speed optical links, for an average event size of 7.5 MB. In the baseline architecture for the Phase-2 DAQ [1], the optical links from detector frontends are aggregated in detector-dependent ATCA based back-end boards. A DAQ and Timing Hub (DTH) aggregates data stersams from multiple back-end boards over point-to-point links. The DTH combines these streams to feed high speed commercial 100 Gb/s optical links, forming the data-to-surface (D2S) network. It provides buffering for time decoupling and transmission using a reliable high-level protocol, such as TCP/IP. The D2S links carry the data to surface, connecting the DTH output via standard network to I/O servers for the event building. The DTH is also distributing trigger accept and timing signals, as well as trigger control codes for calibration and synchronisation to the back-end electronics, from where they are redistributed to the front-ends. This poster presents the system level functionality and performance requirements of the DTH. The DTH will have a modular design, based on Timing unit and a DAQ unit (with 0.4 Tb/s bandwidth). The first step of the DTH development roadmap (P1 for a DTH-400) is currently under design.

### **Design Choices**

#### ATCA

- infrastructure needed on board (IPMC, etc.)

- processor and software for configuration, control and monitor

- zync

- ComExpress PC on the board

- IPbus over ethernet

- pci-express over backplane

- FPGA serial links for input / output

- backplane

- mid-board optics (FireFly, etc )

## **Design Choices**

- Loss-less concentration / event-building

- Ethernet: custom protocol over UDP, converged ethernet, TCP/IP ?

- RDMA or others in FPGA

- Memory resources with large size and bandwidth

- Block-RAM

- recently appearing fast serial memory (Hybrid Memory Cube)

- Timing and Trigger control