#### Real Time systems Introduction

DOOO

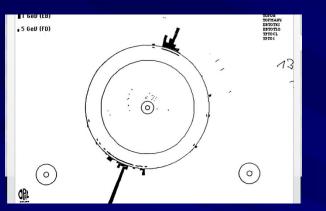

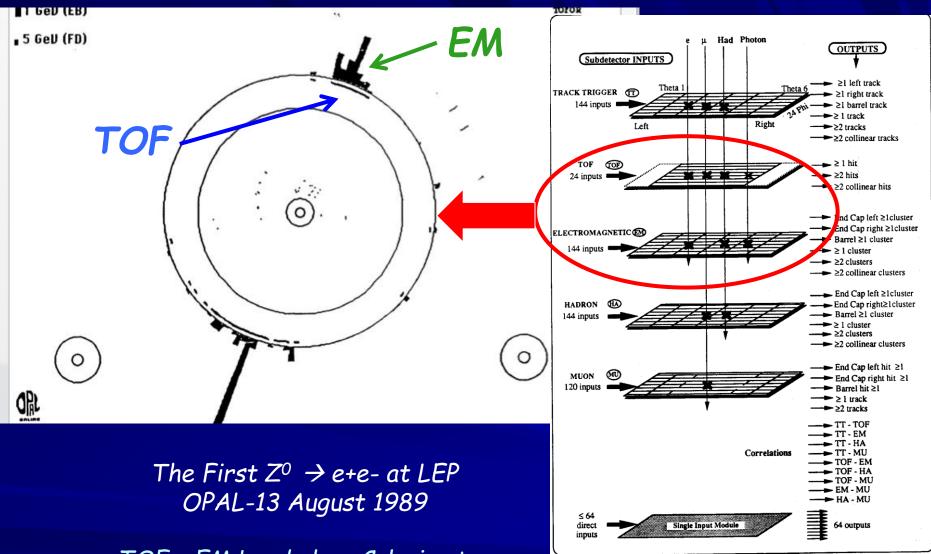

The First Z<sup>0</sup> → e+e- at LEP OPAL-13 August 1989

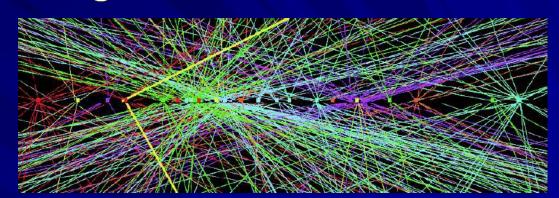

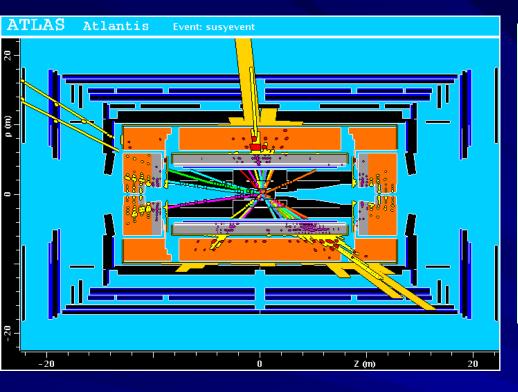

Z -> μμ event at LHC ATLAS 15 April 2012

P. Le Dû

parickledu@me.comr

Vietnam Real Time systems School

July 2016

Goals of these presentations Introduce the concept of 'REAL TIME' and its technological evolution in HEP over the last 40 years. Illustrated by some typical applications in various fields. July 2016 <u>\_</u> Vietnam Real Time system school

# Part # 1 & 2- What is Real Time ?' Definition of REAL TIME ? - Introducing the subject of this school - Context & Basic definitions & terminology A 45 years of HEP history 1969 - 2016 - From bubble chamber to today Evolution of components architectures , tools and techniques A view in the the future !

Application in other fields

## Thanks

Some material and lots of inspiration for these lectures was taken from various lectures

- Helmuth Speiler (LBNL)

- Philippe Farthouat (CERN)

- Christophe Delataille (IN2P3)

- Ted Liu (FNAL)

- G.Watts (UW)

- ... and many others

Some overlap with the other lectures but it is good to see the same topic from different sides **July 2016**

# Few words about Detectors

RADIATION DETECTION AND MEASUREMENT

Radiation Instrumentation The Bible Glenn Knoll

#### Particle detectors Colliders

#### Fixed target

#

Vietnam Real Time system school

#### Non accelerator

July 2016

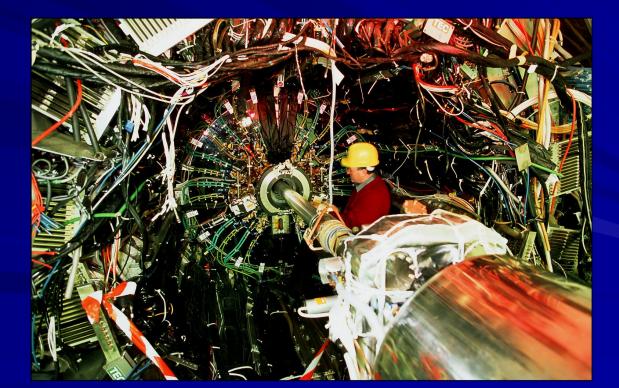

#### **Electronics in experiments**

- A lot of electronics in the experiments...

- Readout electronics :

- amplification, filtering... : Analog electronics

- Processing & Trigger electronics : Digital electronics (bits)

#### But also that !

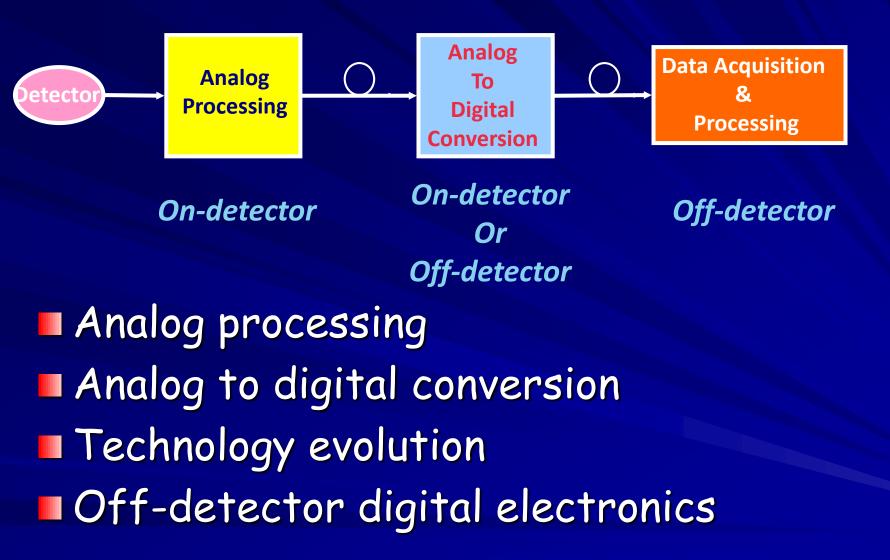

# The electronics blocks

#### Readout electronics : requirements

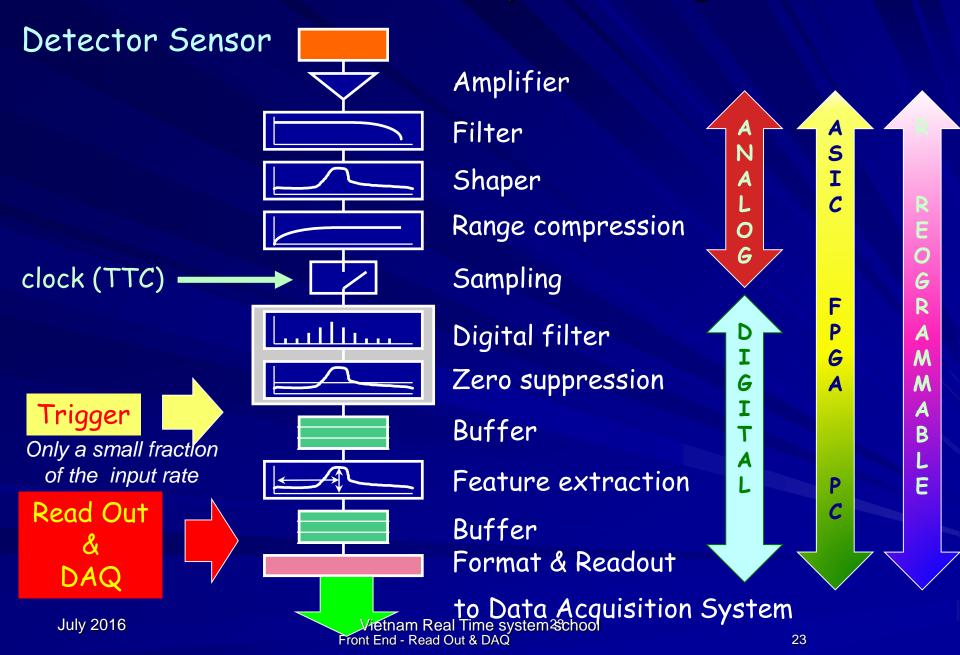

# Front End Electronics

#### Helmuth Speiler lectures http://www-physics.lbl.gov/~spieler/

#### **Requirements principles**

Sensors electronics must determine 1. presence of a particle 2. magnitude of signal 3.time of arrival Some measurements depend on sensitivity, i.e. detection threshold, e.g.: silicon tracker, to detect presence of a particle in a given electrode Others seek to determine a quantity very accurately, i.e. resolution, e.g. : calorimeter magnitude of absorbed energy; muon chambers time measurement yields position All have in common that they are sensitive to: 1. signal magnitude July 2016 luctuations Vietnam Real Time system school

#### What is "front-end" electronics`

- Front-end electronics is the electronics directly connected to the detector (sensitive element)

Its purpose is to

- acquire an electrical signal from the detector (usually a short, small current pulse)

- tailor the response of the system to optimize

the minimum detectable signal

energy measurement (charge deposit)

- event rate

- time of arrival

- insensitivty to sensor pulse shape

- digitize the signal and store it for further treatment

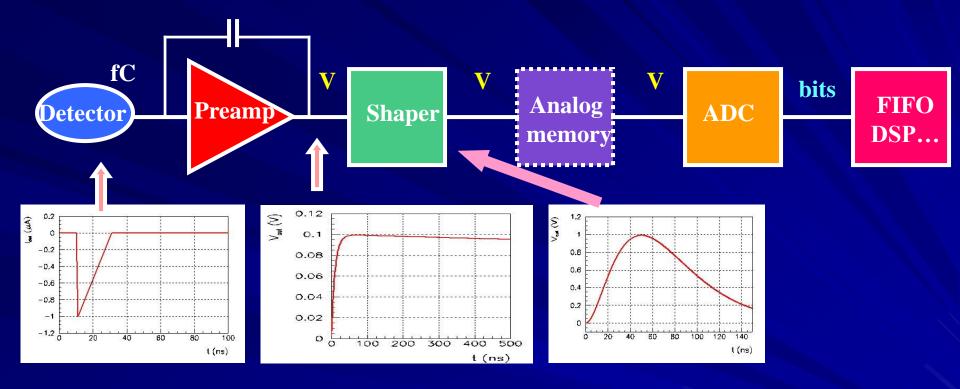

#### Overview of Front End readout electronics chain

Very small signals (fC) -> need amplification

- Measurement of amplitude and/or time

- (ADCs, discris, TDCs)

- Several thousands to millions of channels

# A more global view

July 2016

#### Evolution of basic parameters

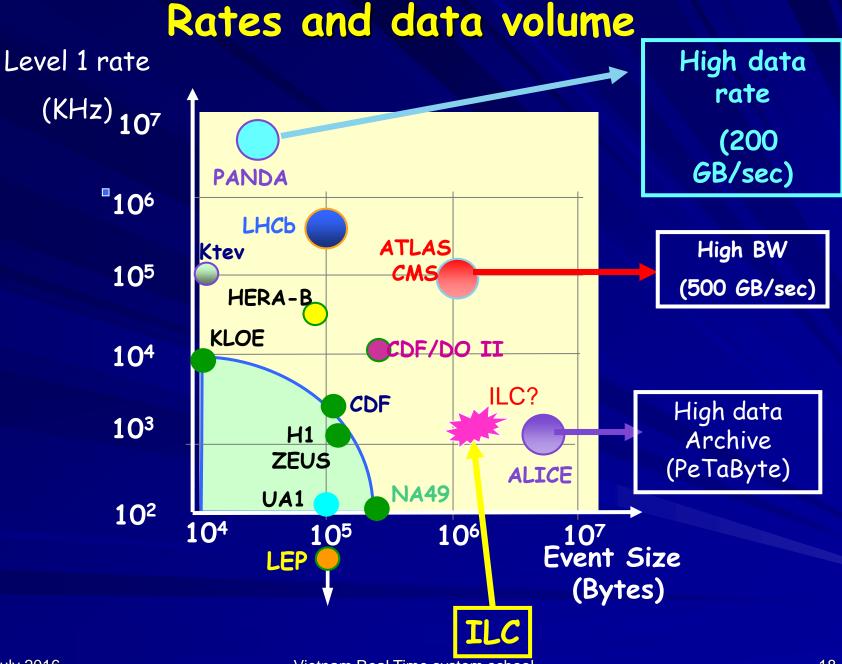

| Exp.<br>Year         | Collision<br>rate | Channel<br>count | L1A<br>rate    | Event<br>building              |                            | Processin<br>g.<br>Power |          | iolog<br>y |  |

|----------------------|-------------------|------------------|----------------|--------------------------------|----------------------------|--------------------------|----------|------------|--|

| UA' s<br>1980        | 3 µsec            | -                | -              | -                              | 5-10<br>MIPS               |                          | 150·     | -200       |  |

| LEP<br>1989          | 10-20<br>µsec     | 250 -<br>500K    | -              | 10<br>Mbit/sec                 | 100 MIPS                   |                          | 300·     | -500       |  |

| BaBar<br><u>1999</u> | 4 ns              | 150K             | 2 KHz          | 400<br>Mbit/s                  | 1000<br>MIPS               |                          | 400      |            |  |

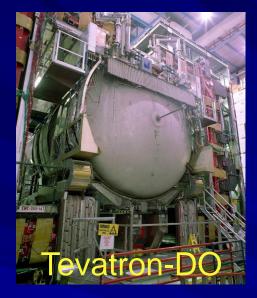

| Tevatron             | 396 ns            | ~ 800 K          | 10 - 50<br>KHz | 4-10<br>Gbit/sec               | 5.10 <sup>4</sup><br>MIPS  |                          | 500      |            |  |

| LHC<br>2010          | 25 ns             | 200 M*           | 100 KHz        | 20-500<br>Gbit/s               | >10 <sup>6</sup><br>MIPS   |                          | 5000     |            |  |

| ILC<br>2025 ?        | 330 ns            | 900 M*           | 3 KHz          | 10 Gbit/s                      | ~10 <sup>6</sup><br>MIPS ? |                          | > 3000 ? |            |  |

| * including pixels   |                   |                  |                | Sub-Detector                   |                            | LHC                      |          | ILC        |  |

|                      |                   |                  |                | Pixel                          |                            | 150 M                    |          | > 800 M    |  |

|                      |                   |                  |                | Microstrips                    |                            | ~ 10 M                   |          | ~30 M      |  |

|                      |                   |                  |                | Fine grain trackers            |                            | ~ 400 K                  |          | 1,5 M      |  |

|                      |                   |                  |                | Calorimeters                   |                            | 200 K                    |          | 30 -100 M  |  |

| July 2016 Vietnam Re |                   |                  |                | al Time syst <b>em scopo</b> l |                            | ~1                       | Μ        |            |  |

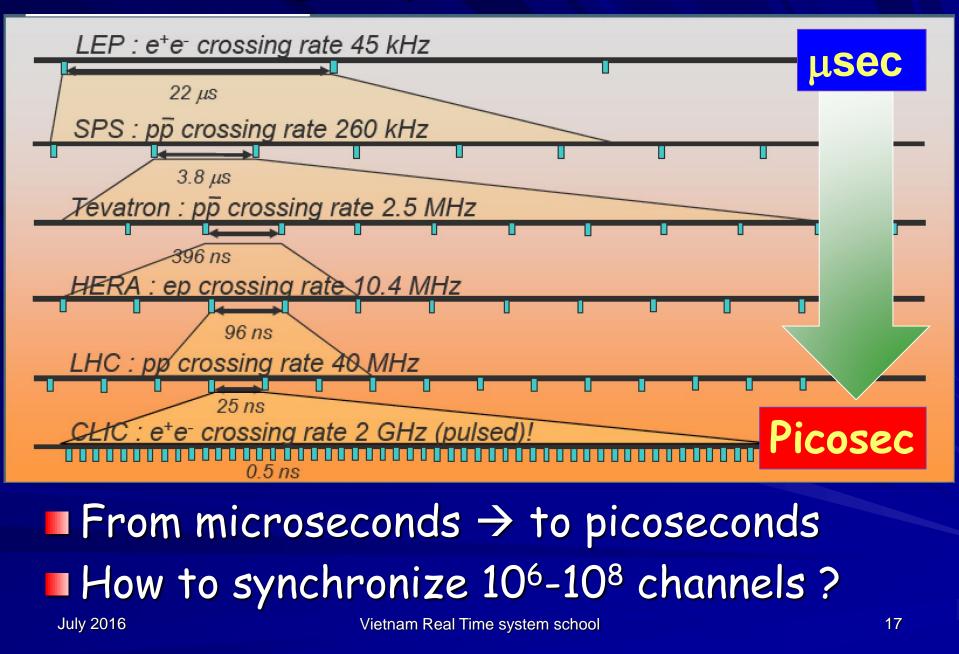

#### **Timing & synchronization issues**

#### July 2016

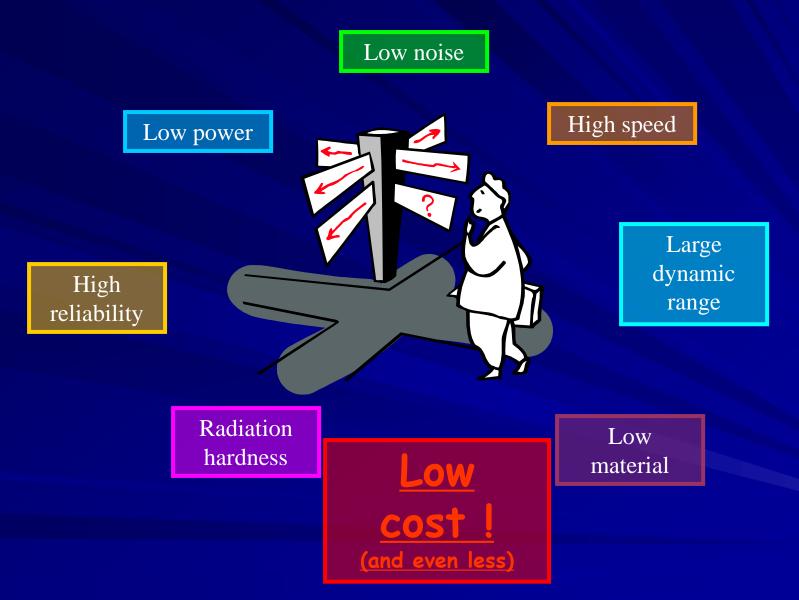

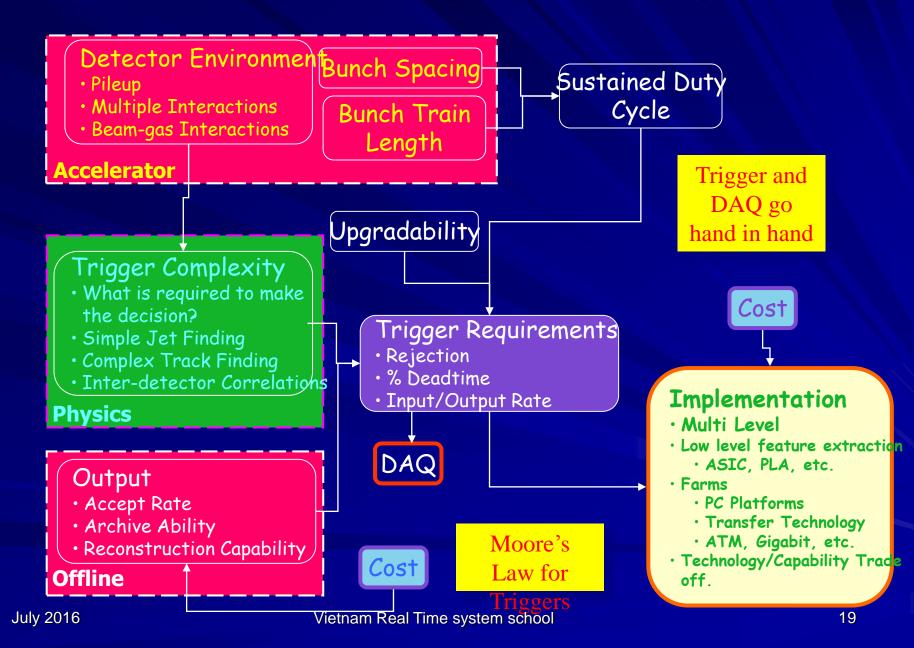

#### Constraints $\rightarrow$ a multiparameters problem

#### The Long Term issue challenge → 15 years of design-20 years of life

# Some basic terminology

July 2016

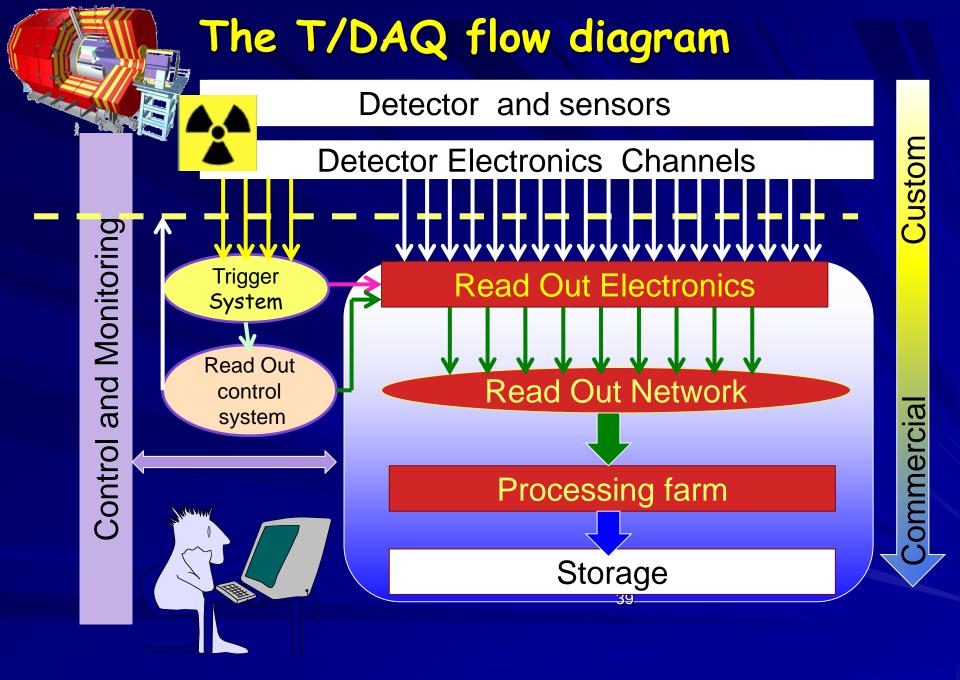

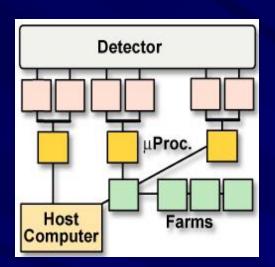

#### What Do We Need to Read Out a Detector ?

- A selection mechanism → "TRIGGER"

- Electronic readout of the sensors of the detectors → "front-end electronics"

- A system to collect the selected data →"DAQ"

- A Control System to configure, control and monitor the entire DAQ

- Time, money, students

#### The read-out chain processing flow

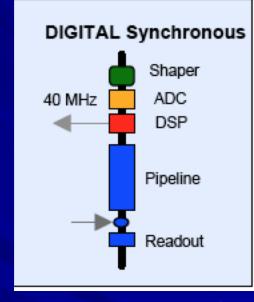

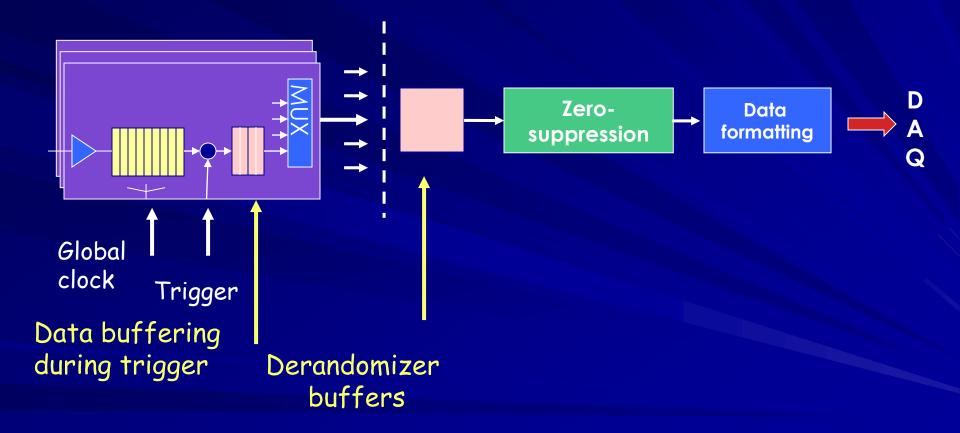

#### Synchronous readout

- All channels are doing the same "thing" at the same time

- Synchronous to a global clock  $\rightarrow$  The bunch crossing

- On-detector buffers (de-randomizers) are of the same size and their occupancy ("how full they are") depends only on the trigger-rate

- Output data-rate on each link is identical and depends only on trigger -rate

- Solution Lots of bandwidth wasted for zero's

- Price of links determine if one can afford this

- Solution No problems if occupancy of detectors or noise higher than expected

- But there are other problems related to this: spill over, saturation of detector, July 2016

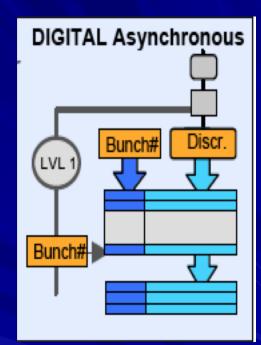

#### Asynchronous readout

#### Remove zeros on the detector itself

- Lower average bandwidth needed for readout links. Especially interesting for low occupancy detectors

- Each channel "lives a life of its own" with unpredictable buffer occupancies and data are sent whenever ready (asynchronous)

- In case of buffer-overflow a truncation policy is needed  $\rightarrow BIAS!!$

- Detectors themselves do not have 100% detection efficiency either.

- Requires sufficiently large local buffers to assure that data is not lost too often (Channel occupancies can be quite non uniform across a detector with same front-end electronics)

- DAQ must be able to handle this (buffering!)

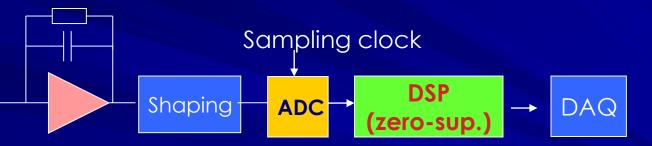

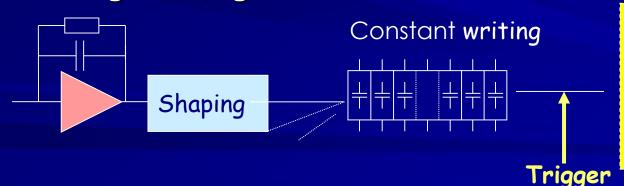

#### **Constantly sampled**

Needed for high rate experiments with signal pileup

- Shapers and not switched integrators

- Allows digital signal processing in its traditional form (constantly sampled data stream)

- Output rate may be far to high for what following DAQ system can handle

With local zero-suppression this may be an option for future high rate experiments (SLHC, CLIC)

## Zero-suppression

- Why spend bandwidth sending data that is zero for the majority of the time ?

- Perform zero-suppression and only send data with non-zero content

- Identify the data with a channel number and/or a time-stamp

- We do not want to loose information of interest so this must be done with great care taking into account pedestals, baseline variations, common mode, noise, etc.

- Not worth it for occupancies above ~10%

- Alternative:

- data compression

#### Synchronous readout

- All channels are doing the same "thing" at the same time

- Synchronous to a global clock (bunch crossing clock)

- Data-rate on each link is identical and depends only on trigger -rate

- On-detector buffers (de-randomizers) are of the same size and there occupancy ("how full they are") depends only on the trigger-rate

- Lots of bandwidth wasted for zero's

- Price of links determine if one can afford this

- Solution States in the second states of the seco

- But there are other problems related to this: spill over, saturation of detector, etc.

#### Synchronous readout

#### **On-detector**

#### Off-detector

#### Summary: Readout to DAQ

Large amount of data to bring out of detector

- Large quantity: ~millions in large experiment

- High speed: Gbits/s

- Point to point unidirectional

- Transmitter side has specific constraints

- Radiation

- Magnetic fields

- Power/cooling

- Minimum size and mass

- Must collect data from one or several front-end chips

- Receiver side can be commercially available module/components (use of standard link protocols when ever possible)

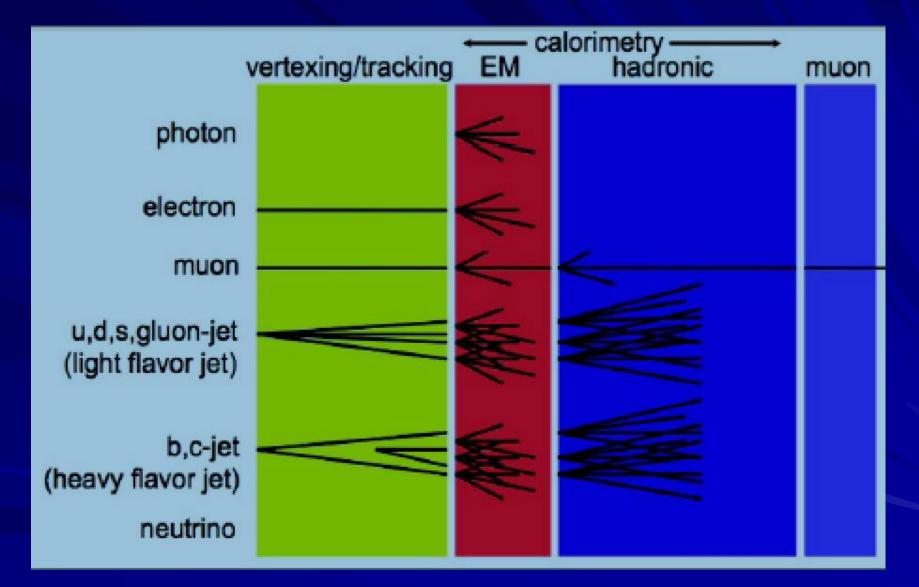

#### Physics signals & Trigger signatures

# The basics of T/DAQ

July-2016

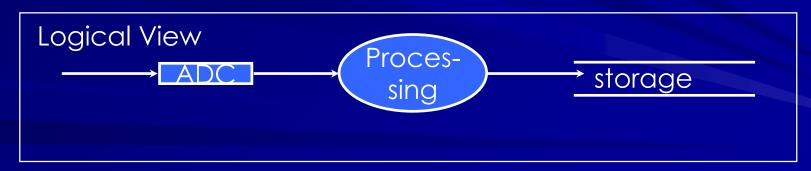

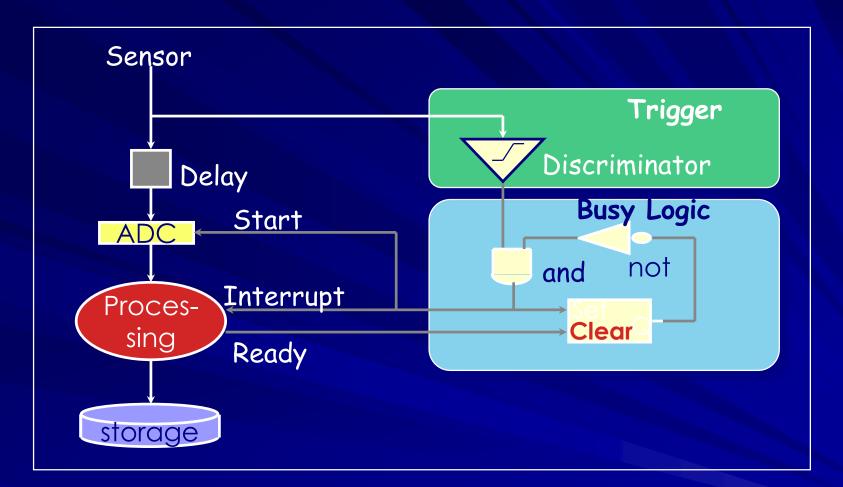

#### **Trivial DAQ**

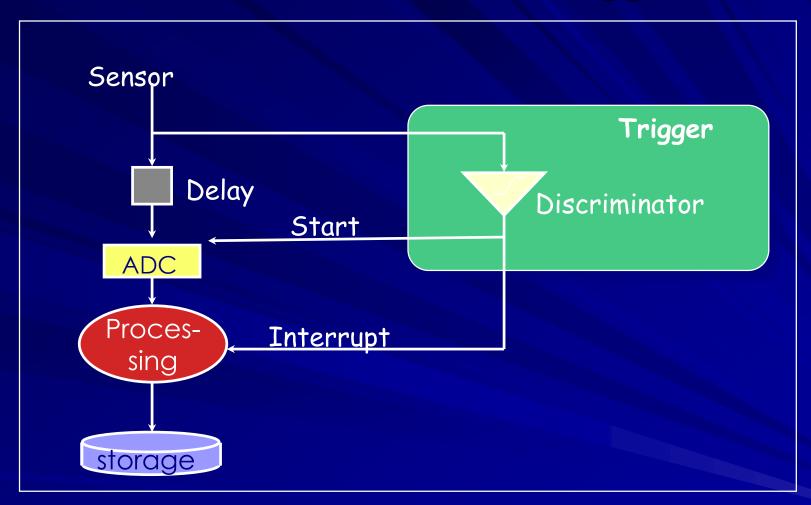

#### Trivial DAQ with a real trigger

# What if a trigger is produced when the ADC or processing is busy?

July 2016

#### Trivial DAQ with a real trigger (2)

# **Deadtime (%)** is the ratio between the time the DAQ is busy and the total time.

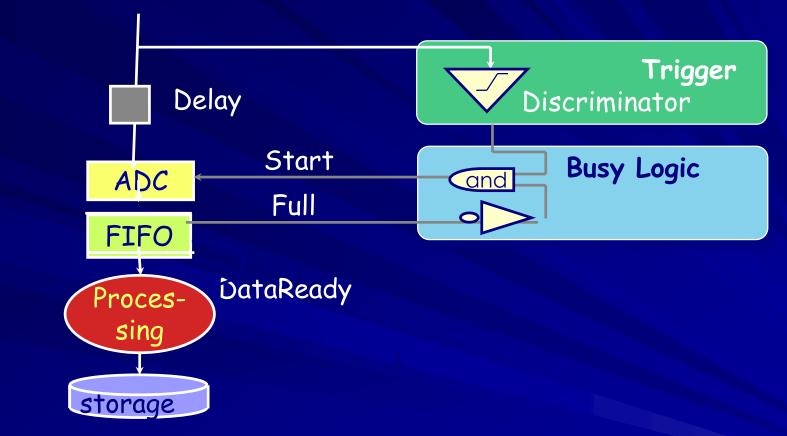

#### Trivial DAQ with a real trigger (3)

Sensor

**Buffers** are introduced to de-randomize data, to decouple the data production from the data consumption. ---> **Better performance**.

July 2016

# The final one

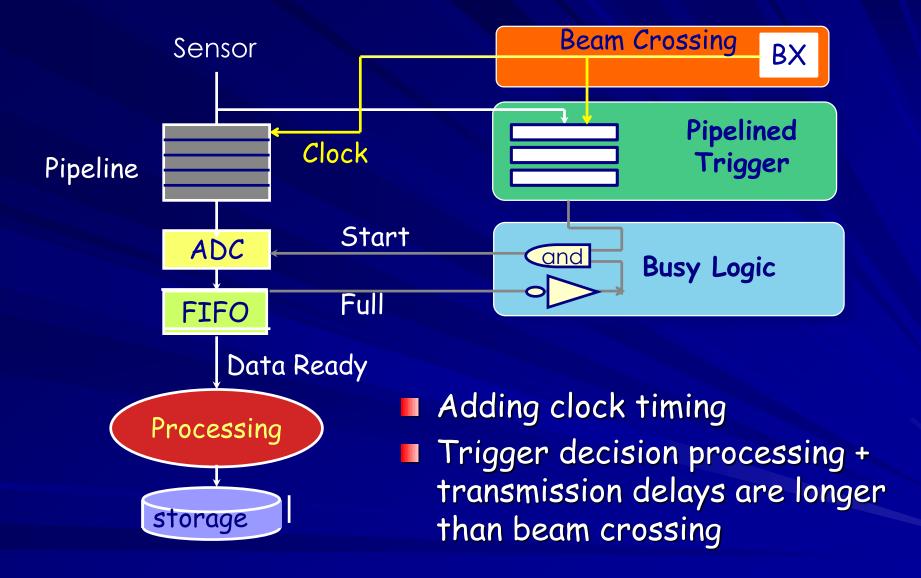

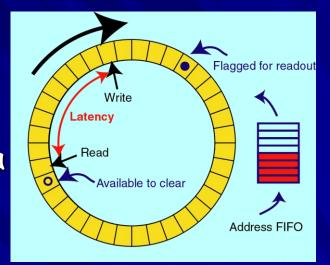

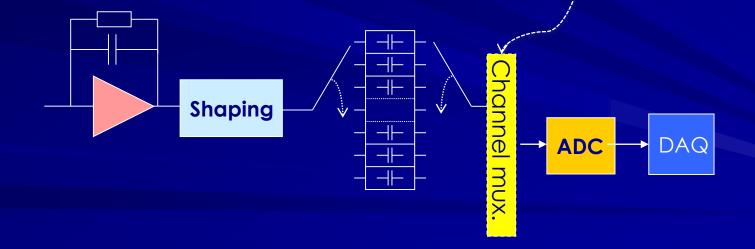

# **Terminology : buffer , pipeline & latency**

Trigger processing requires some data transmission and processing time to make decision so front-ends must buffer data during this time. This is called the trigger latency For constant high rate experiments a "pipeline" buffer is needed in all front-end detector channels: (analog or digital) (e.g. circular buffer  $\rightarrow$

Circular buffer

ADC

Channel

Mux

38

DAQ

July 2016

Vietnam Real Time system school

Lots of custom electronic Massive use of parallel processing in FPGAs (and some ASICs) Part of the electronics in radiation area Processing time typically 1 - 4 µs (limited by expensive buffer (?) memory on the detector) Common system for reliable transmission of timing and trigger decisions (TTC)  $\rightarrow$ in the future (partially) replaced by GBT

# DAQ (Read Out) summary

#### Scalability

change in event-size, luminosity (pileup!)

#### Robust

(very little dead-time, high efficiency, non-expert operators) → intelligent control-systems

#### Use industry-standard,

commercial technologies (long-term maintenance) → PCs, Ethernet

#### ■ Low cost $\odot \rightarrow$ PCs, standard LANs

- High band-width (many Gigabytes/s) → use local area networks (LAN)

- "Creative" & "Flexible" (open for new things) → use software and reconfigurable logic (FPGAs)

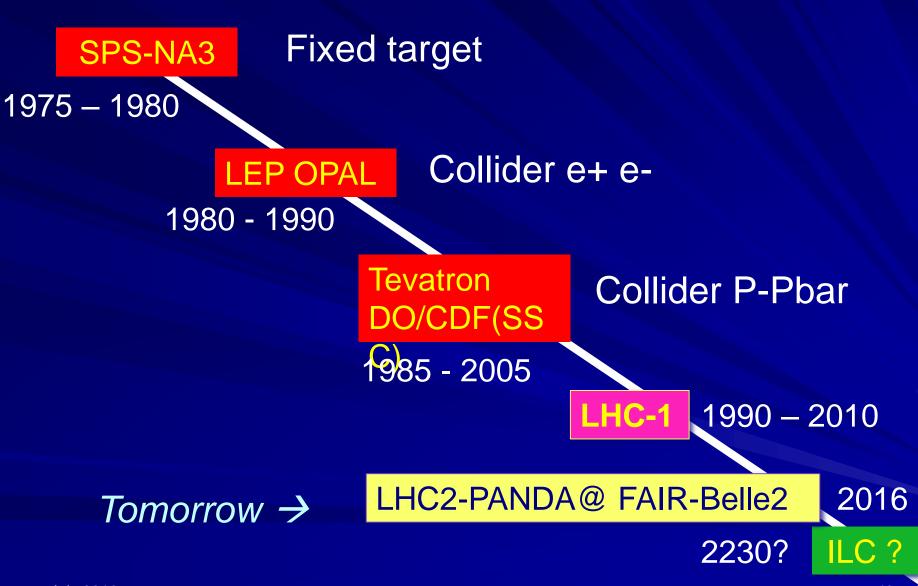

### 45 years of (r) evolution My life!

# History

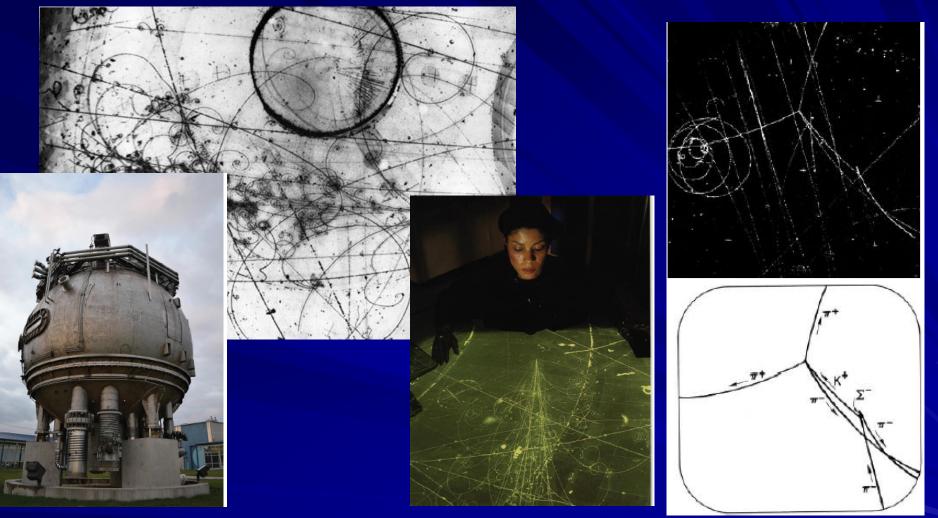

#### The prehistoric world the Bubble Chamber -1955-1975

Our Roots back to 'triggerless DAQ' July 2016

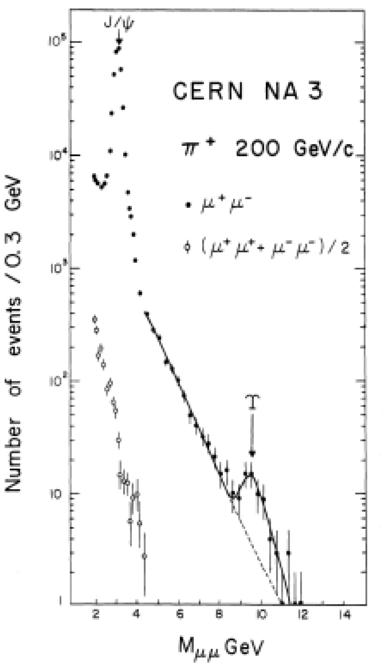

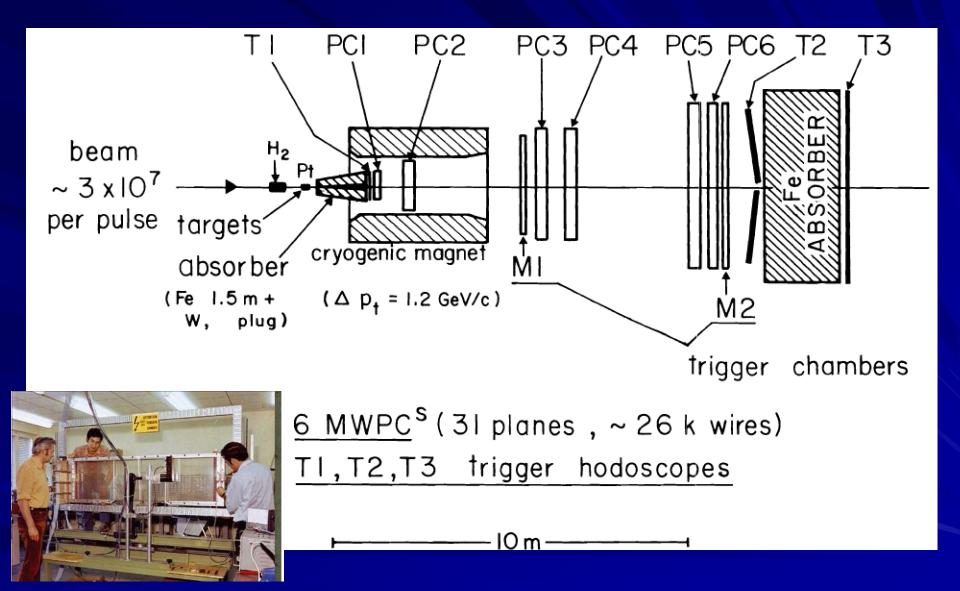

# A fixe target experiment NA3

# The 70's @ CERN SPS

July 2016

Vietnam Real Time system school

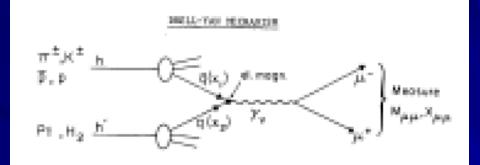

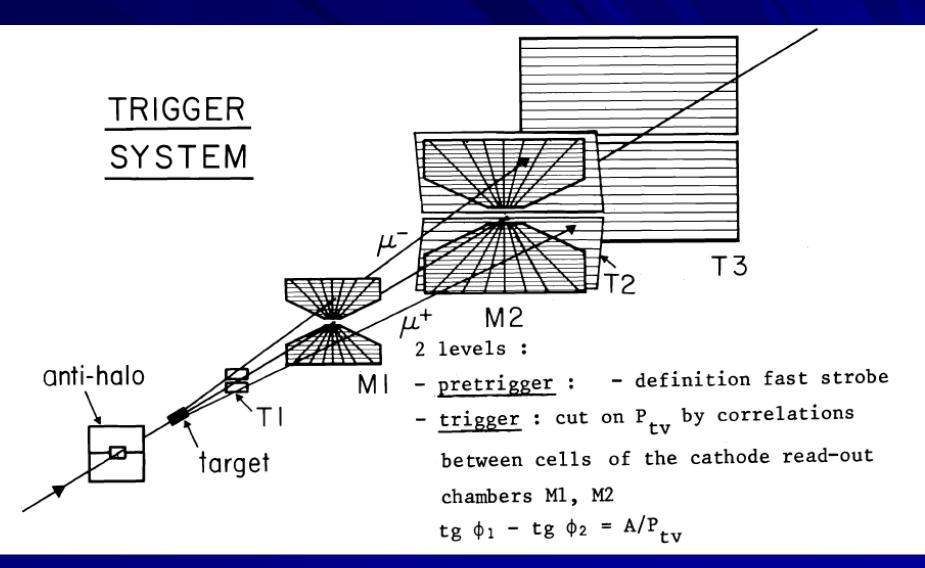

### **NA3** Physics

Harwired processor For real time calculation of dimuon mass and separate stream of data

July 2016 , pi-mon and distribution for at an Mieinam Real Time system school

### NA3 Set Up

### **Electronics Multiple event buffers**

Good for experiments with short spills and large spacing between spills (e.g. fixed target experiment like SPS @ CERN) → 2 sec spill and 7 sec interburst

Fill up event buffers during spill (high rate)

Readout between spills (low rate)

ADC can possibly be shared across channels (MUX)

Buffering can also be done digitally (in RAM)

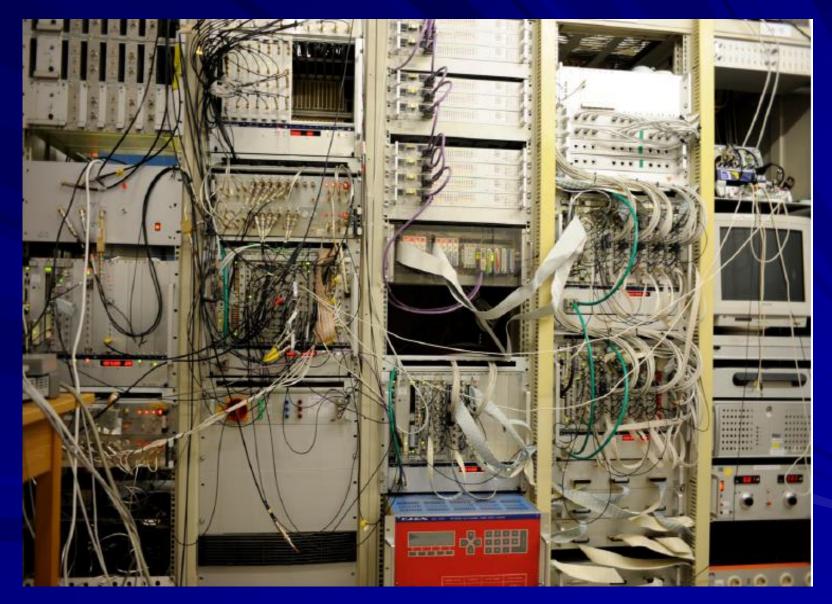

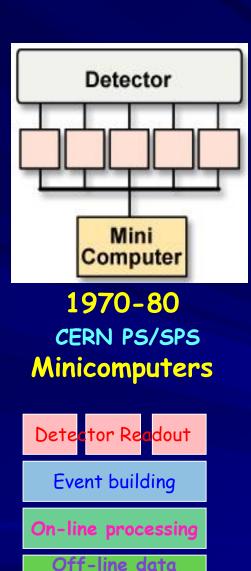

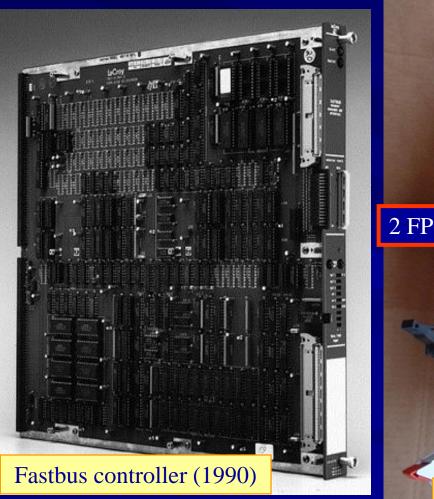

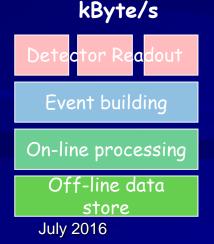

Evolution of DAQ technologies and architectures (1) "The old time of Minicomputer"

Trigger:

- NIM logic (50 Ohms cable)

- Hardwired custom design

- No pipelines

- Similar to today LVL1's

- Large deadtime possible during read Out

- DAQ : First standard : CAMAC

- The LeCroy time (ADC, TDC, PU)

- Rate kByte/s

- Minicomputers (16 bits)

- HP, Digital PDP 11-45, IBM 3070

### A lot of dead time & bad connections

July 2016

Vietnam Real Time system school

From S. Cittolin

50

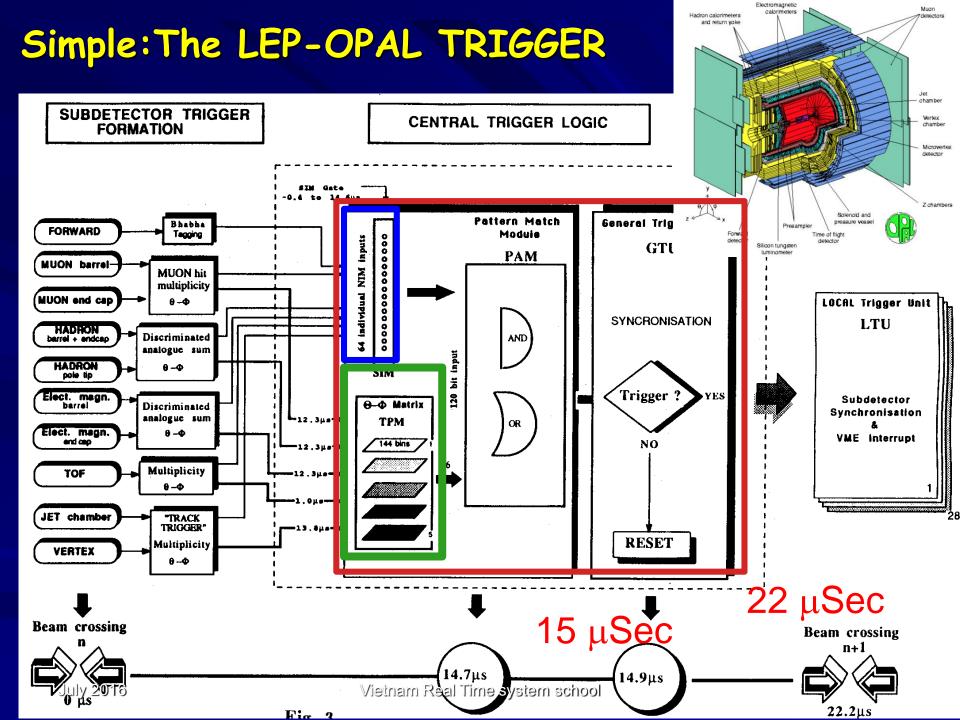

# 80's The LEP-OPAL

# The transition world

July 2016

Vietnam Real Time system school

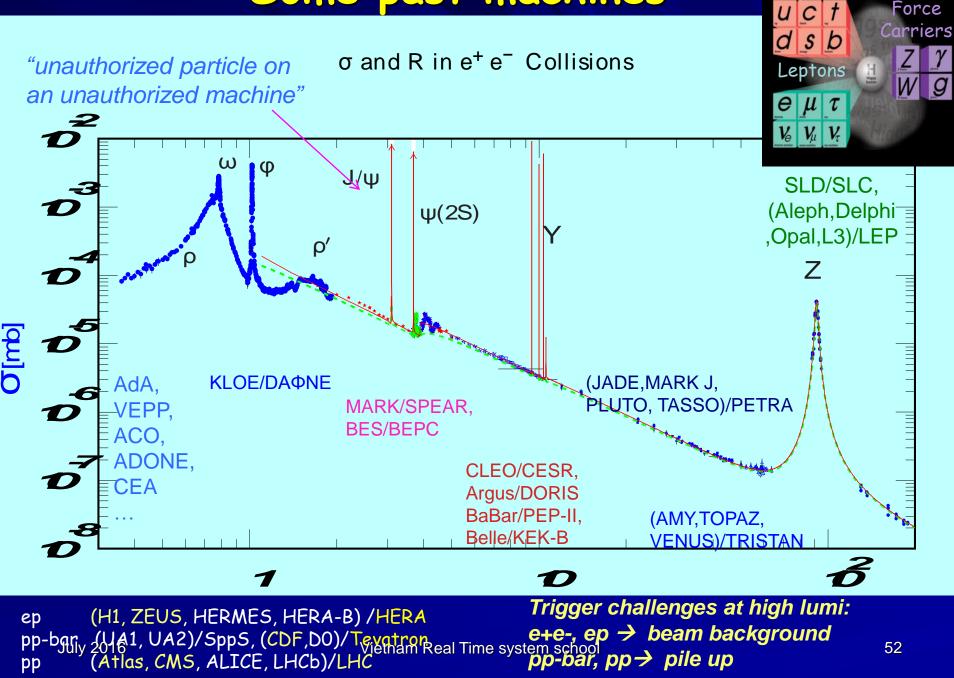

### Some past machines

Quarks

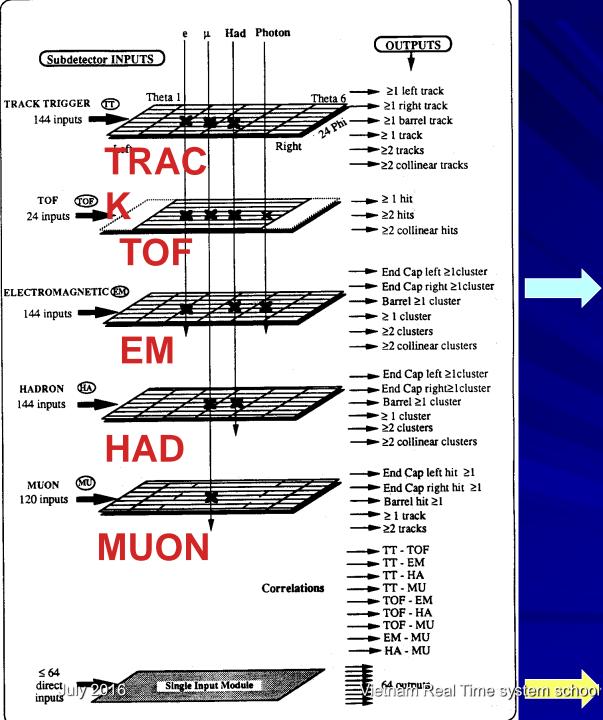

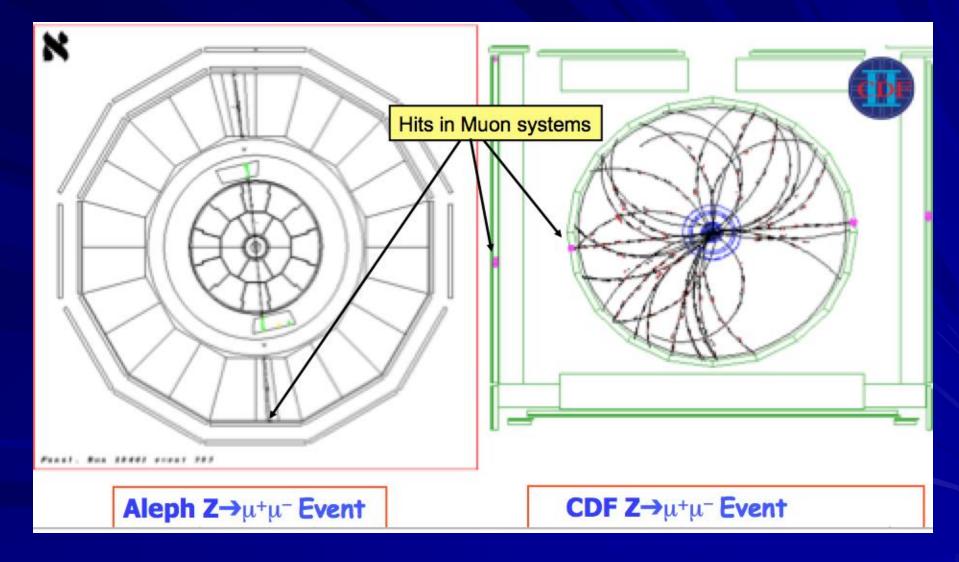

# **Requirements for e+e- Triggering**

Accept: (almost) all real collisions

Reject:

- very low angle e+e-

- Beam-gas/wall events tracks not from beam spot in r or z

- Trigger on simple event topology

- Time-Of-Flight coincidence

- Multiplicity of good tracks (from beam spot) low pt cuts (100s of MeV/c)

- Calorimeter activity: global energy and clustered energy in relative coarse spatial bins

- Simple combinations

### Time stamping

Beam Xing << detector response times (few nsec vs 100-1000ns)</li>

The OPAL Trigger Matrix - 24 Phi - 6 Eta - Total =144 trigger cells

64 'Phi' single input signals 80% of Trigger

55

### The LEP ZO first event

TOF + EM Lead glass Calorimeter

1980-90 LEP Microprocessors

Evolution of DAQ technologies and architectures (LEP) The birtday of microprocessors

- Custom hardware triggers

- HEP Standard → FASTBUS

- Embedded CPU

- Motorola 6800 → 68000

- 58 to 512 KB RAM Memory

- Industry Standard (VME)

- Rate → Mbytes/sec

- - Emulators 3081,370E, Transputers, farms (ACP)

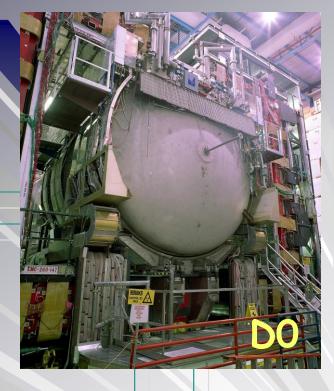

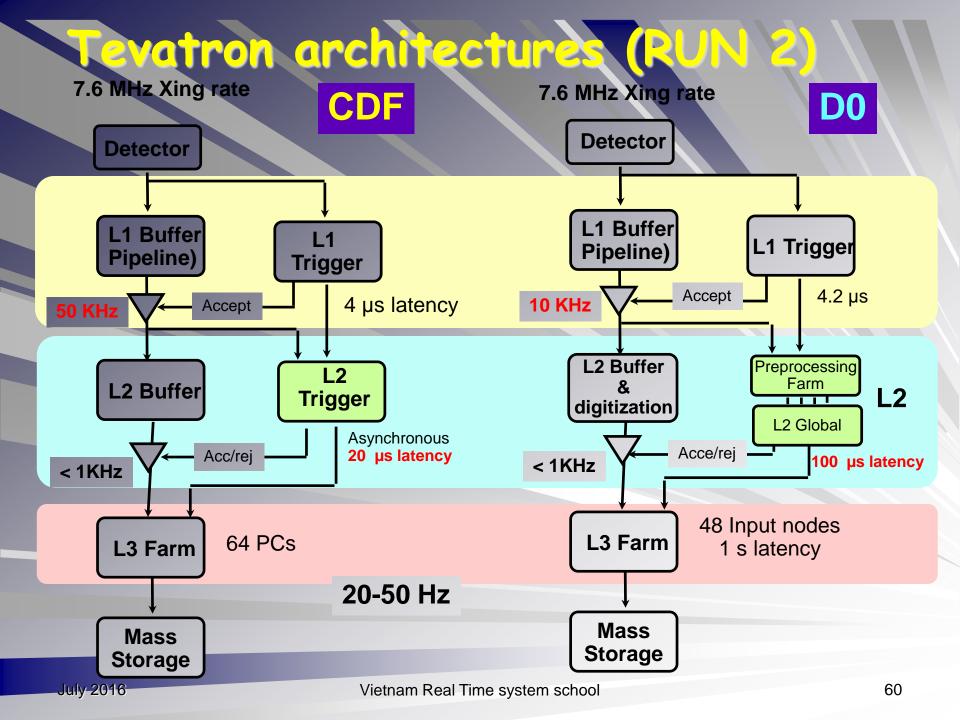

# Tevatron

# the beginning of modern time

Yietnam Real Time system school

# e+e+ vs pp environment

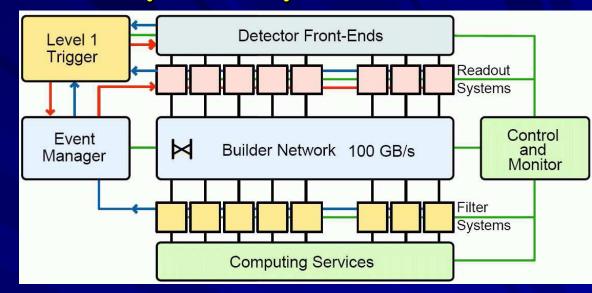

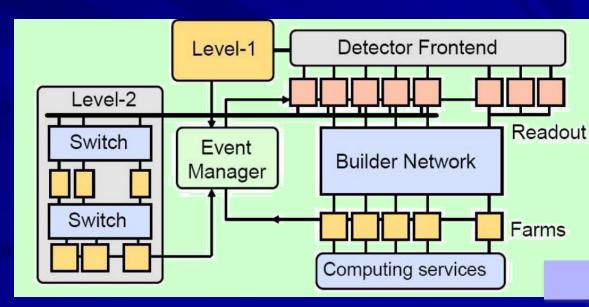

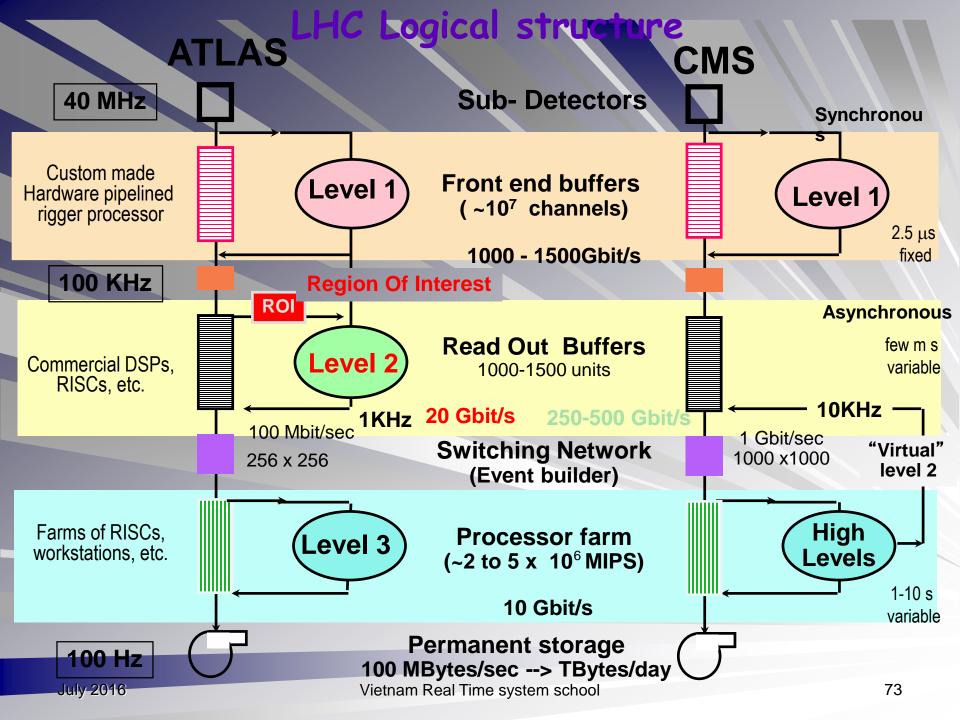

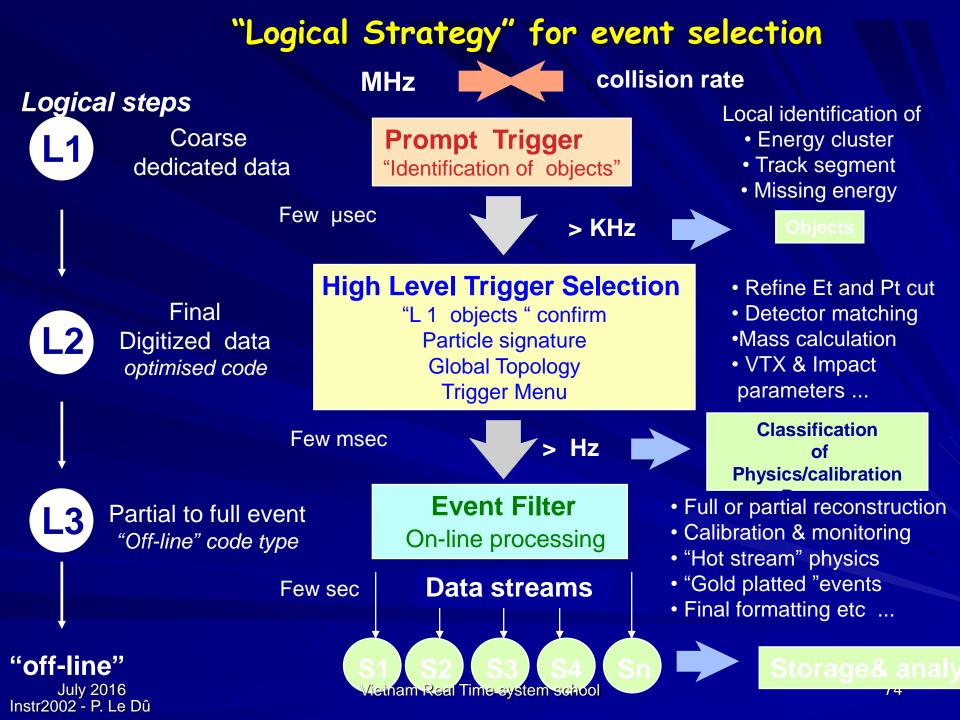

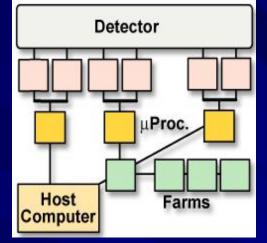

# Multilevels trigger and DAQ

#### Required rejection is orders of magnitude

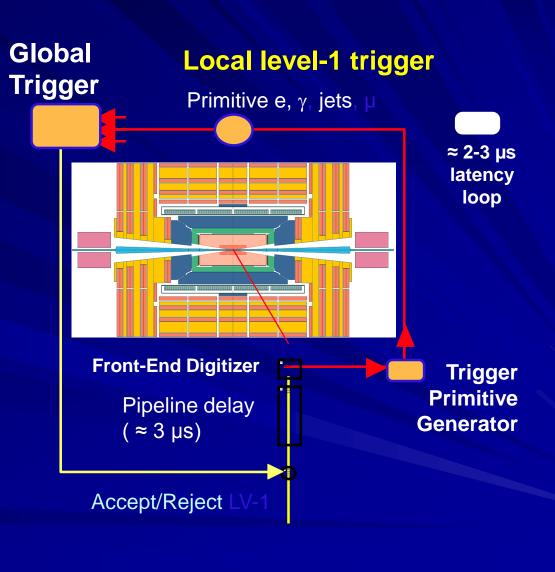

#### Level 1 is hardware based

- -Hardwired trigger system to make trigger decision with short latency. -Constant latency buffers in the front-ends

- -Crude signatures (hits and tracks, local energy deposit over threshold...)

- -Operates on reduced or coarse detector data

#### Level 2 is a composite

-Dedicated custom/DSP/FPGA processing or Processor based (standard CPU's or FIFO buffers with each event getting accept/reject in sequential order

Level 3 is a farm → General Purpose CPUs hundreds - thousands

Vietnam Real Fine system schoolses this scheme.

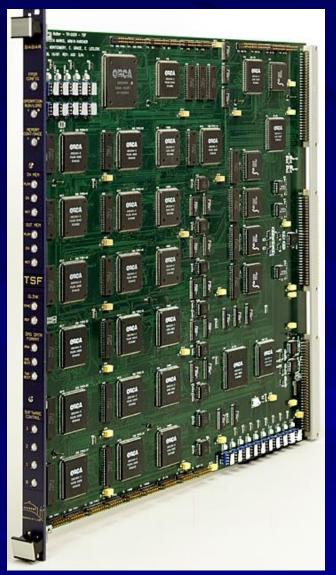

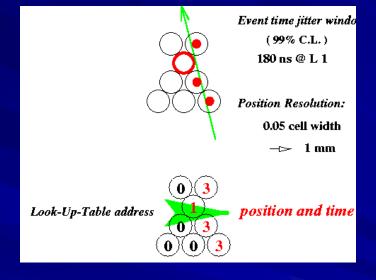

# LV1 examples

# Large custom boards

Track Segment Finder

# Example of evolution

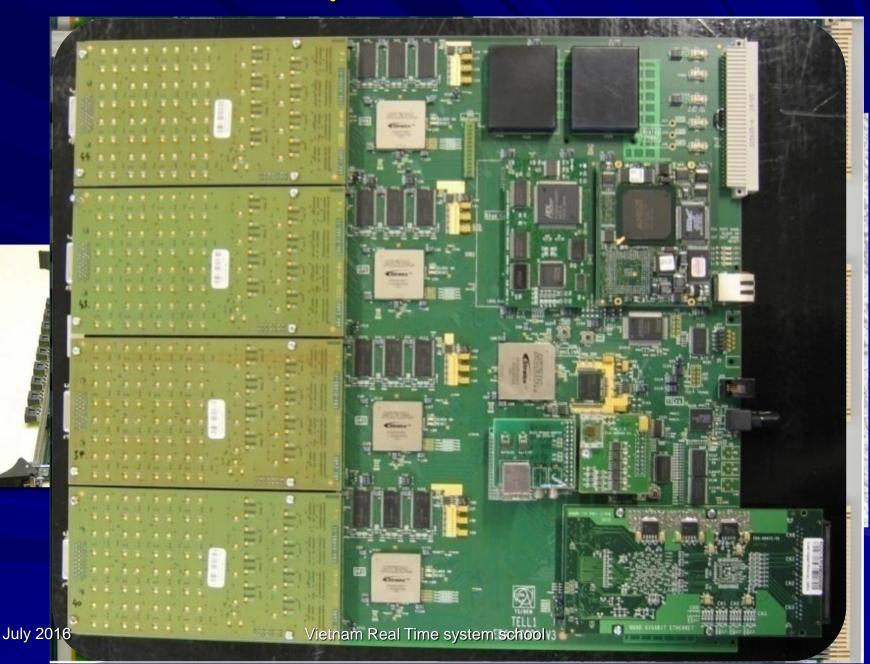

Demonstrator at the end of the 90's

Final version installed

Muon trigger board for ATLAS

- Handles 13 input links, each of them receiving 32-bit every 25ns

- ~17 Gb/s processed

# Examples of modules

# Evolution of digital electronics From arrays of circuits to FPGAs : programmable logic

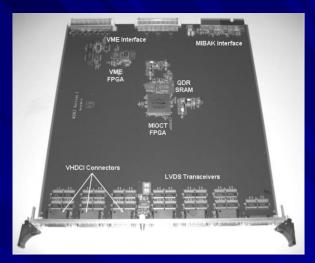

# LVL2 examples

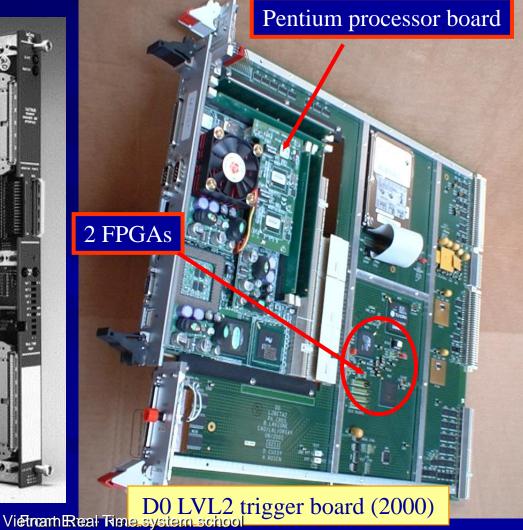

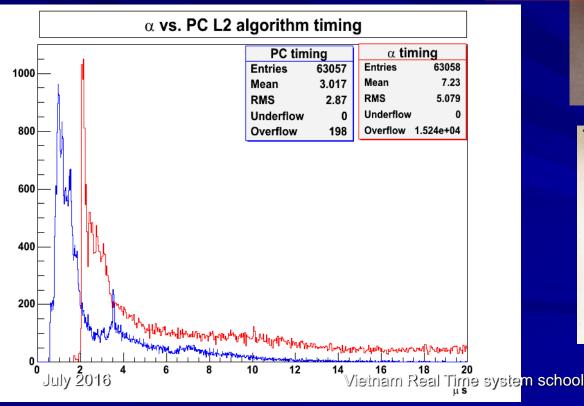

- Alpha = many years of efforts ....hardware and software

- PC (Commercial): few months to implement! No hardware !

Pentium processor board

2 FPGAs

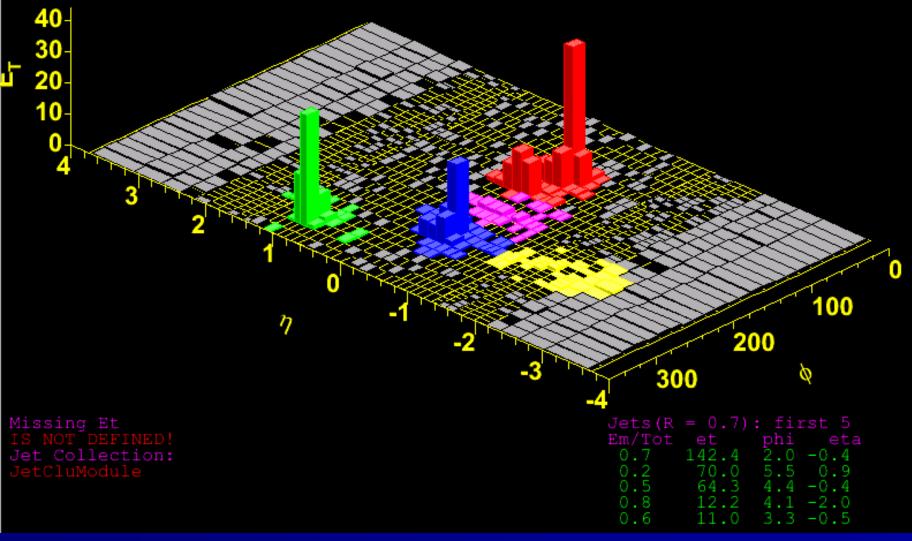

#### D0 LVL2 trigger board (2000)

Alpha Processor board

Event : 293170 Run : 198206 EventType : DATA | Unpresc: 0,1,5,8,9,10,11,12,13,16,51,53,23,55,24,56,25 Presc: 0,1,8,9,10,12,24,56,25

#### L2 Jet trigger in DO

July 2016

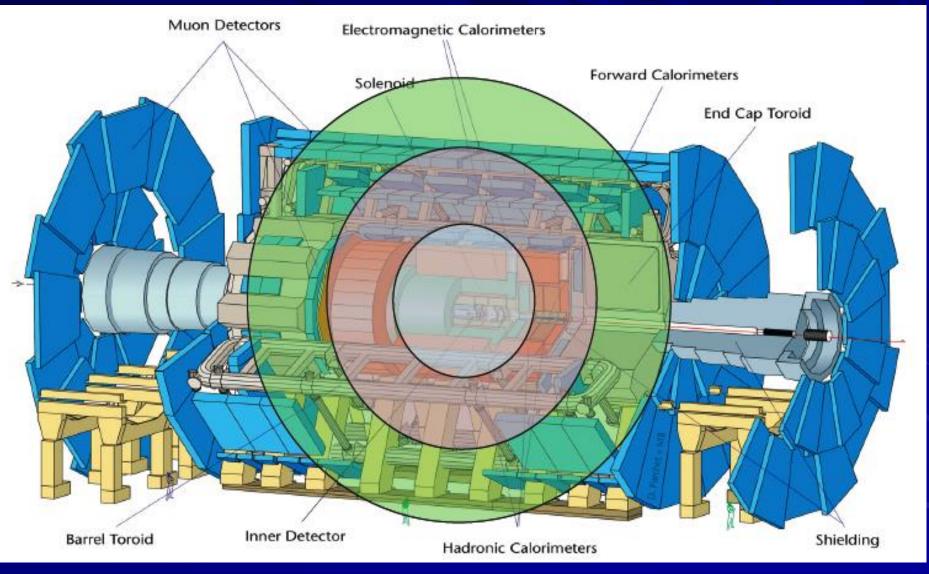

# $pp \rightarrow H + X \rightarrow \gamma\gamma + X Trigger and Data$ Acquisition for LHCexperiments

Vietnam Real Time system school

C.C.S.

NIAY

Run: 204769 Event: 71902630 Date: 2012-06-10 Time: 13:24:31 CE

# Challenges 1: Time of Flight

c =  $30^{2016}$  cm/ns  $\rightarrow$  in 25 ns, s = 7.5 m

# Distributing the L1 Trigger

- L1 decision has to be brought for each crossing to all the detector front-end electronics elements so that they can send of their data or discard it

- All experiments use common TTC system

| L1 trigger<br>latencies |                |

|-------------------------|----------------|

| ALICE                   | No<br>pipeline |

| ATLAS                   | 2.5 us         |

| CMS                     | 3 us           |

| LHCD <sup>2016</sup>    | 4 us           |

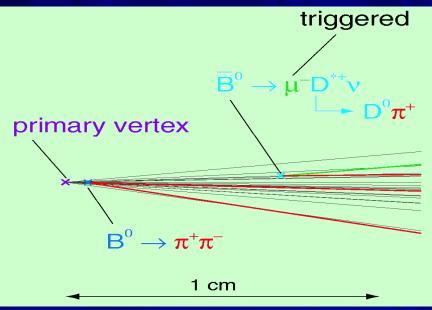

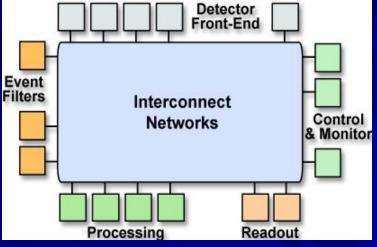

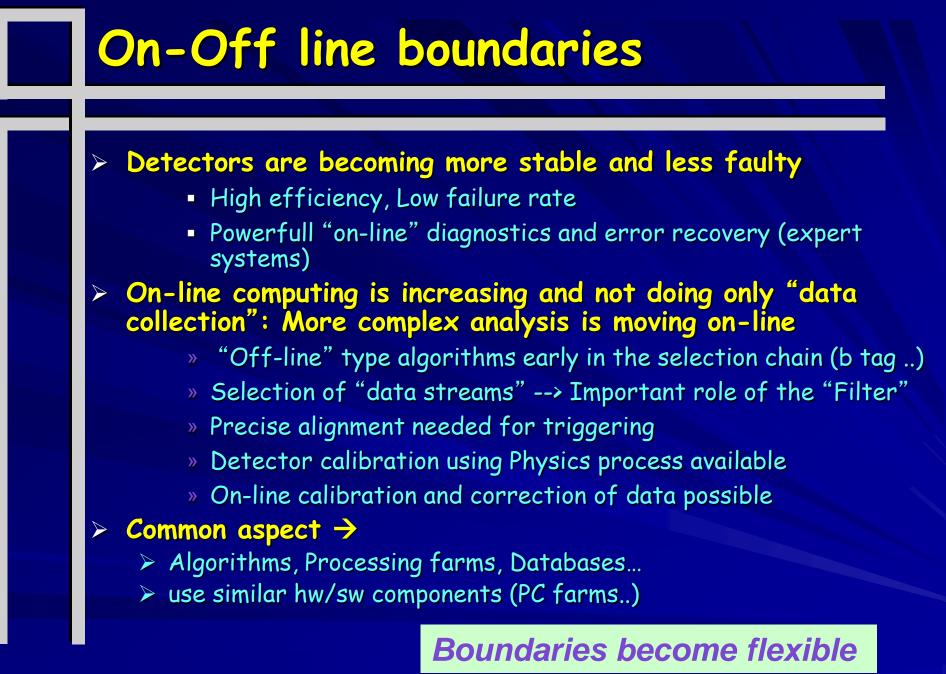

### After L1 $\rightarrow$ Two philosophies

Send everything, ask questions later (ALICE, CMS, LHCb)

Send a part first, get better question Send everything only if interesting (ATLAS)

#### **High Level Triggers**

Complicated Event structure with hadronic jets (ATLAS) or secondary vertices require full detector information Methods and algorithms are the same as for offline reconstruction

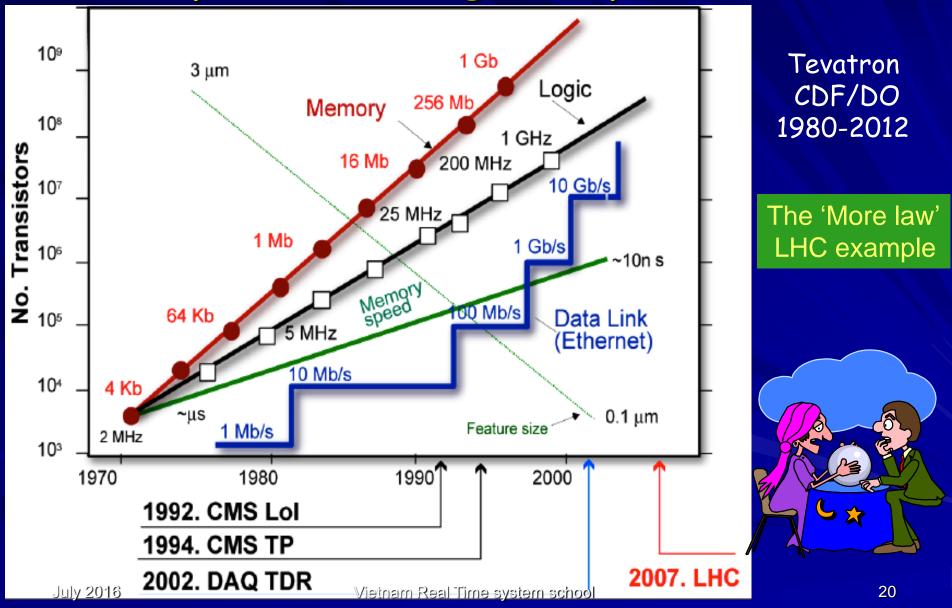

#### evolution of DAQ technologies and architectures

1970-80 CERN PS/SPS Minicomputers Readout custom design First standard: CAMAC

#### 1980-90 LEP

#### Microprocessors

HEP standards (Fastbus) Embedded CPU, Industry standards (VME) MByte/s

Vietnam Real Time system school

#### 2007 ... LHC (CMS) Networks/Grids

IT commodities, PC, Clusters Internet, Web, etc. **GByte/s**

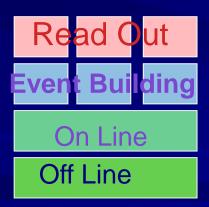

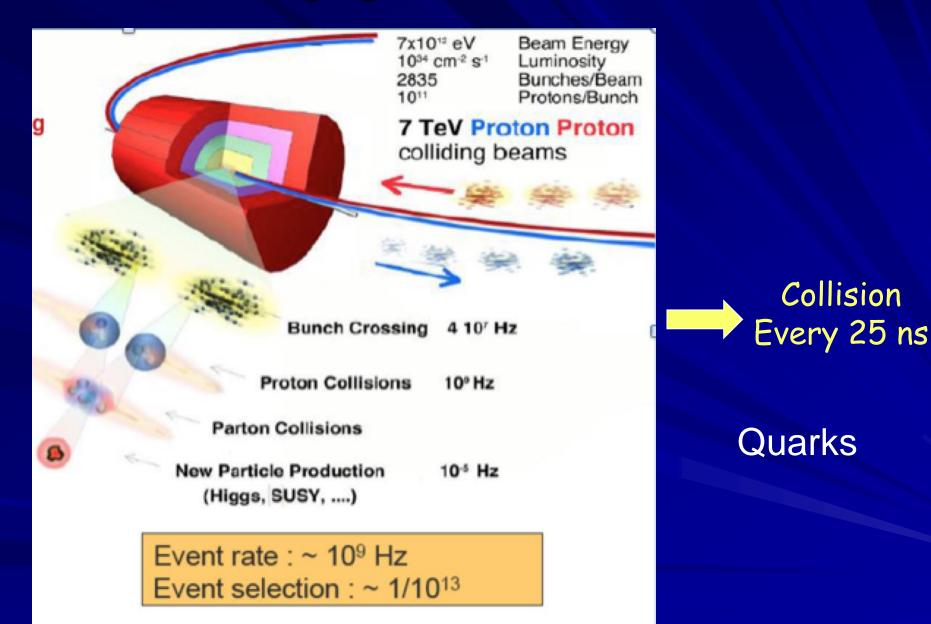

### Conclusions

### Present evolution (SLHC ...)

Higher level trigger decisions are migrating to the lower levels -> Software Migration is following functional migration

- Correlations that used to be done at Level 2 or Level 3 in are now done at Level 1.

- More complex trigger (impact parameter!) decisions at earlier times (HLT) → Less bandwith out of detector?

- Boundaries

- L2 and L3 are merging into High Levels Triggers

- DAQ and trigger data flow are merging

- On-line and off-line boundaries are flexible

- > Recent Developments in Electronics

- Line between software and hardware is blurring

- Complex Algorithms in hardware (FPGAs)

- Possible to have logic designs change after board layout

- Fully commercial components for high levels.

Hardware Triggers

### Summary of T/DAQ architecture evolution

#### Today

- Tree structure and partitions

- Processing farms at very highest levels

- Trigger and DAQ dataflow are merging

#### Near future

- Data and control networks merged

- Processing farm already at L2 (HLT)

- More complex algorithms are moving on line

- Boundaries between on-line and off-line are flexible

- Comodity components at HLT July 2016 Vietnam Real Time system school

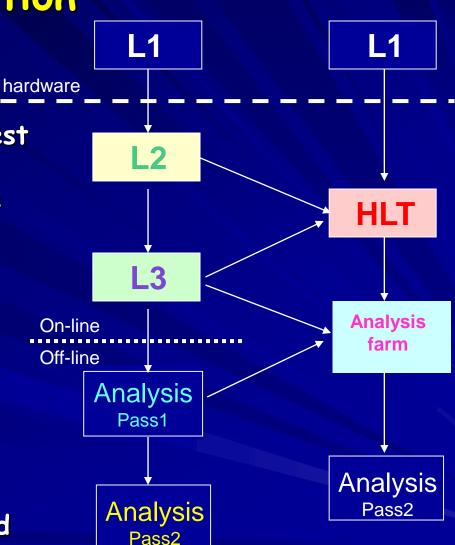

## **Evolution of Standards**

# Technology forecast summary

End of traditional parallel backplane bus paradigh

- Announced every year since ~1989

- VME-PCI still there

- watch PCI Express, RapidIO, ATCA

- Commercial networking products for T/DAQ

- Conferences:

- ATM, DS-Link, Fibre Channel, SCI

- Today: Gigabit Ethernet (  $1 \rightarrow 10 \rightarrow 30$  GB/s)

- The ideal processing / memory / IO BW device

- The past:

- Emulators (370E), Transputers, DSP's, RISC processors

- Today: FPGA's →

- Integrates receiver links, PPC, DSP's and memory

### Technology forecast (Con't)

#### Point-to-point link technology

- The old style: Parallel Copper Serial Optical

- The modern style: Serial Copper Parallel Optics

Today 10Gb/s → 30Gb/s

- Continuous increasing of the computing power (Clock)

Today : > 100 GBytes

2015: > Tera Bytes ...

#### Modern wisdom (about technology)

"People tend to overestimate what can be done in one year, and underestimate what can be done in 10 years."

# Introduction One minute on Physics

July-2016

Vietnam Real Time system school

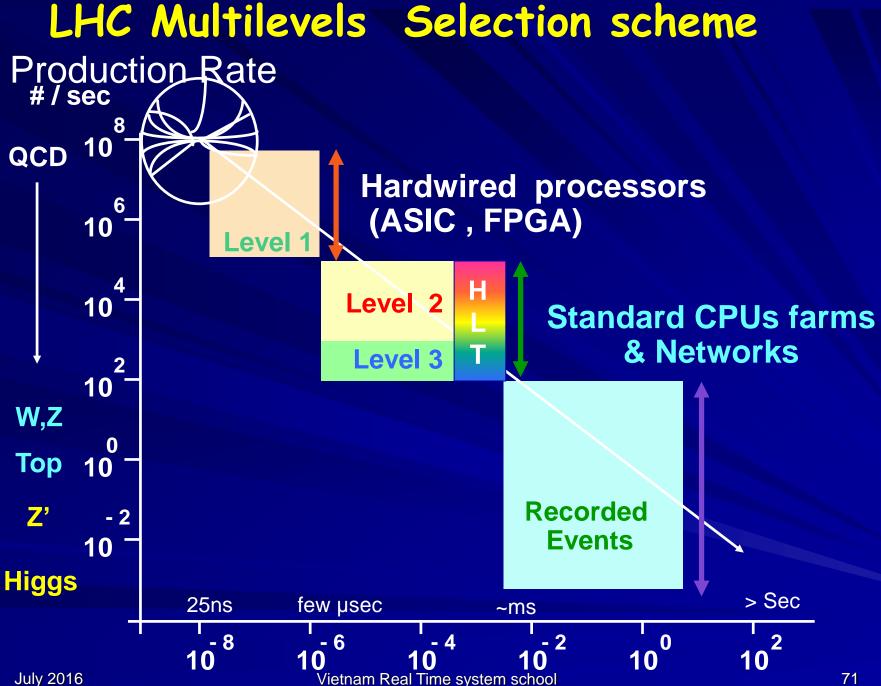

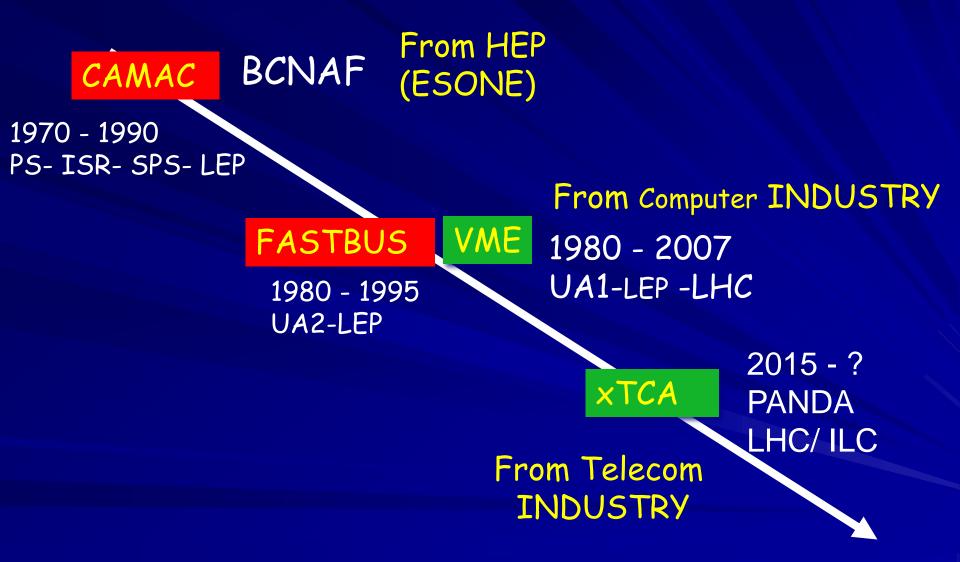

### Challenging : The LHC T/DAQ

July 2016

### The p-p machine challenges

pp collisions produce mainly hadrons with transverse momentum " $p_{+"} \sim 1 \text{ GeV} \rightarrow \text{minimum bias events}$ Interesting physics (old and new) has particles (leptons and hadrons) with large p<sub>t</sub>: -  $W \rightarrow e_V$ :  $M(W) = 80 GeV/c^2 p_t(e) \sim 30-40 GeV$ -  $H(120 \text{ GeV}) \rightarrow \gamma\gamma$ : p<sub>+</sub>(γ) ~ 50-60 GeV Impose high thresholds on the p<sub>+</sub> of particles - Implies distinguishing particle types; possible for electrons, muons and "jets";

- beyond that  $\rightarrow$  need complex algorithms

# The LHC challenge

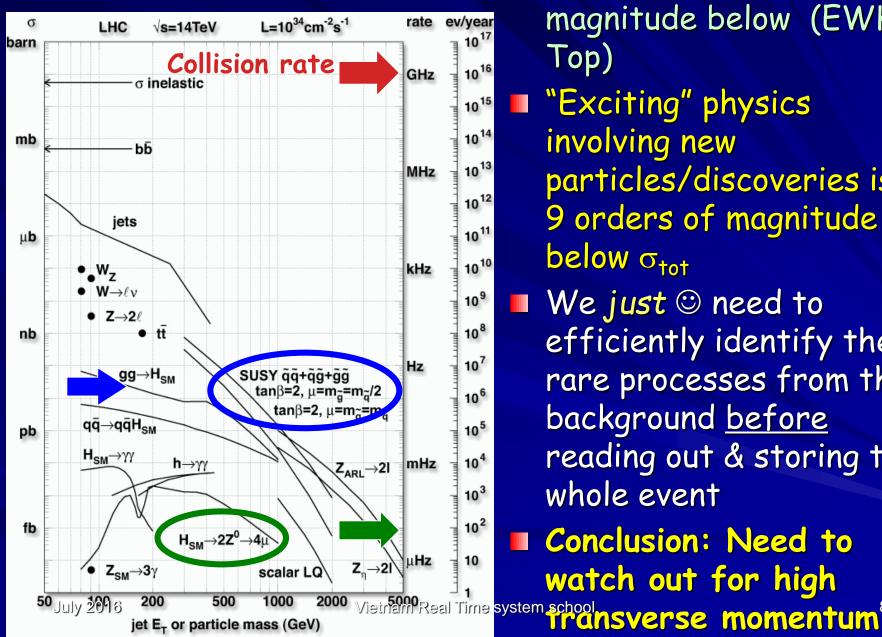

"Interesting" physics is about 6-8 orders of magnitude below (EWK & Top) "Exciting" physics involving new particles/discoveries is  $\geq$ 9 orders of magnitude below  $\sigma_{tot}$ We just

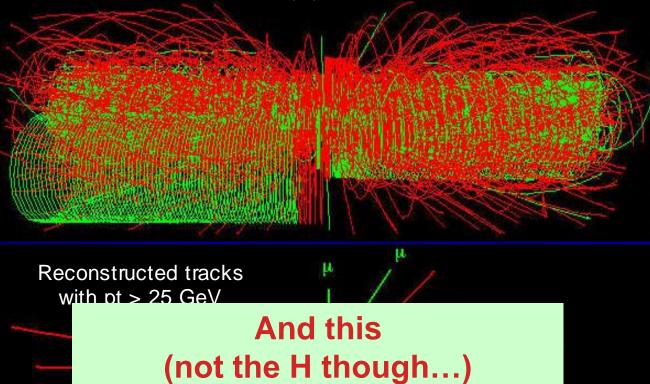

in need to efficiently identify these rare processes from the background <u>before</u> reading out & storing the whole event Conclusion: Need to watch out for high 88

#### pp Collisions at 14 TeV at 10<sup>34</sup> cm<sup>-2</sup>s<sup>-1</sup> Higgs→ZZ → 4 Muons + H→ 4 muons + 20-30 'overlapped' min bias:events

#### repeats every 25 ns

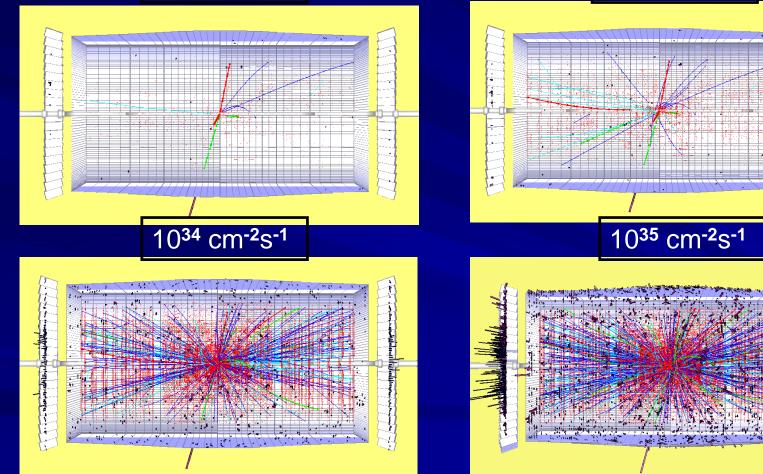

# For hadron collider: increasing luminosity could get one into deep trouble ...

$H \rightarrow ZZ \rightarrow \mu\mu ee$ ,  $M_H = 300 \text{ GeV}$  for different luminosities in CMS

#### 10<sup>32</sup> cm<sup>-2</sup>s<sup>-1</sup>

July 2016