**Paul Scherrer Institute, Switzerland IEEE NPSS distinguished lecturer**

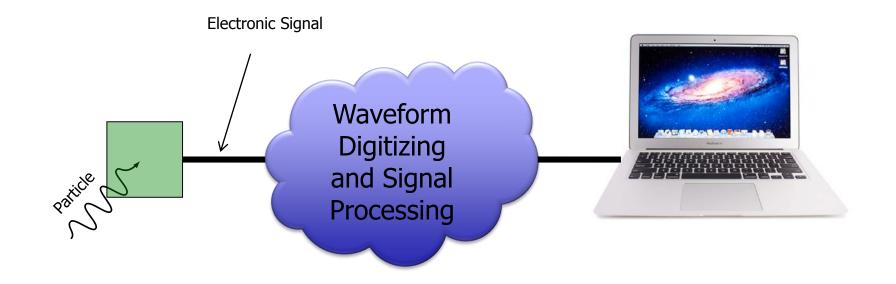

Stefan Ritt Front-end Electronics, Waveform Digitizing and Signal Processing

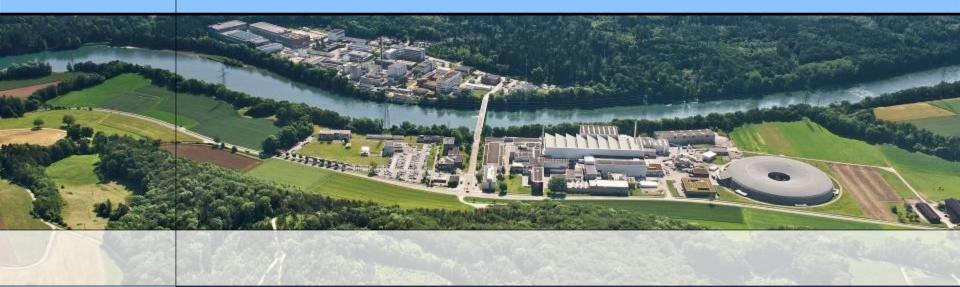

## "Manual" DAQ

1000 tracks per 25 ns A4 paper @ 5 g Truck load @ 40 t

How much paper per second?

### 200'000 t 5000 Trucks !!!

- ADC & TDC technologies

- Signal shaping

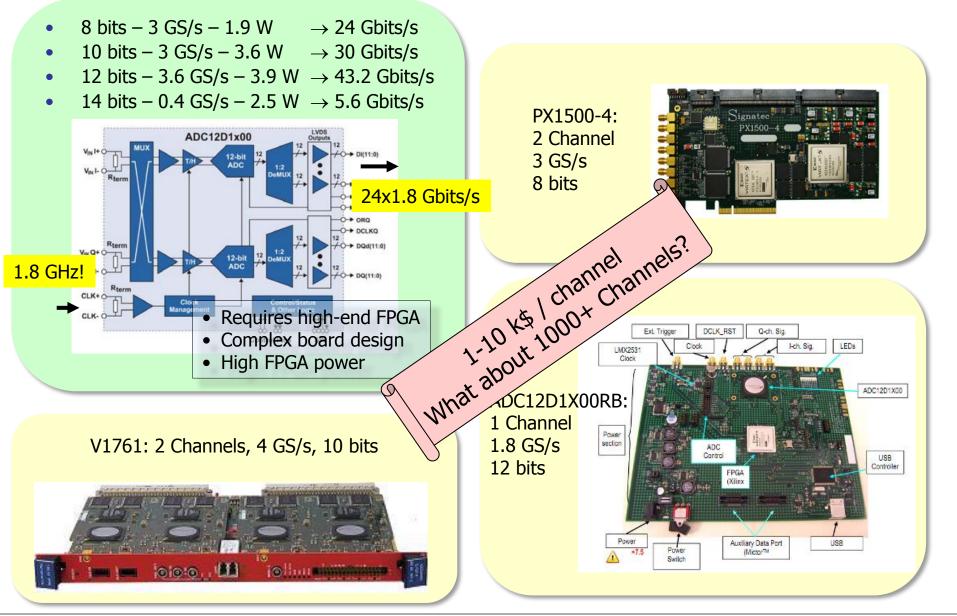

- Ultra-fast digitizing (>1 GSPS)

- Digital pulse processing

- Applications

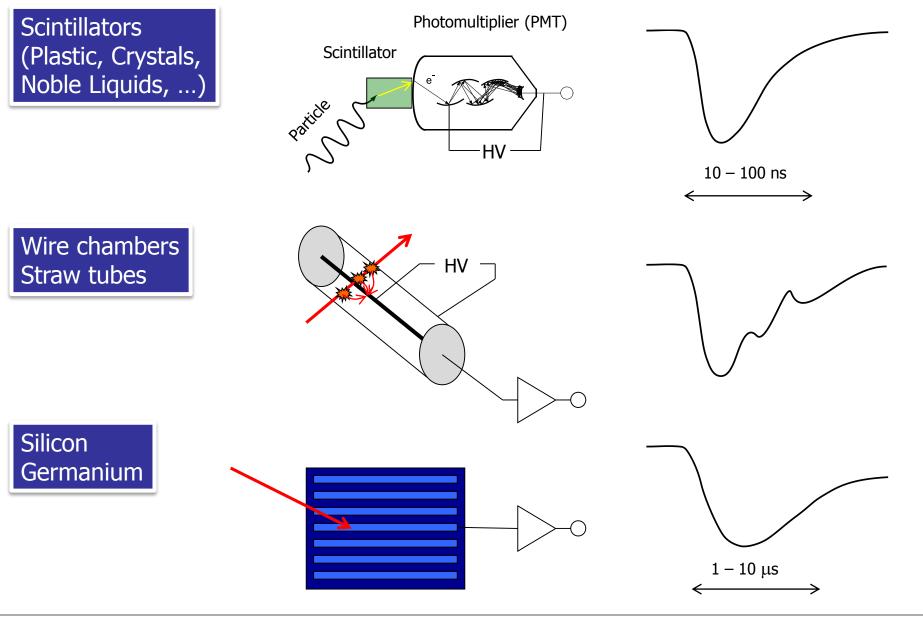

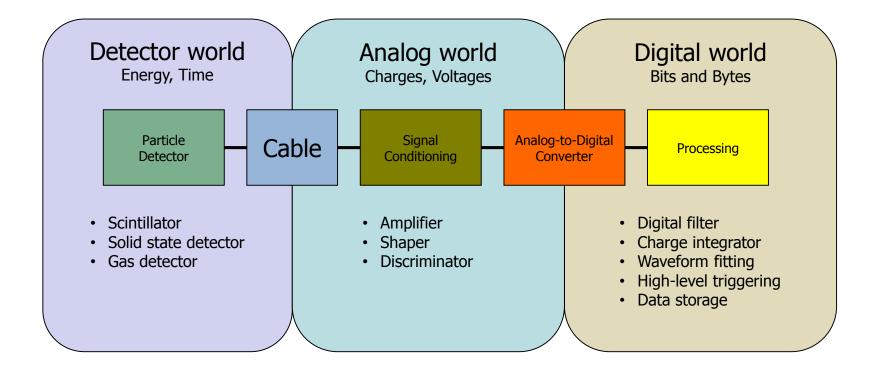

# **Signals in particle physics**

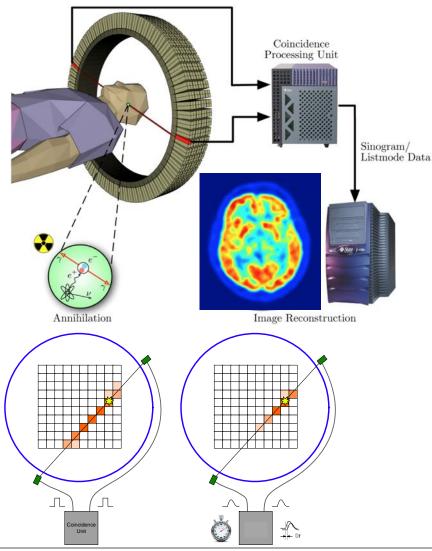

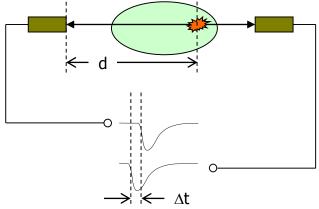

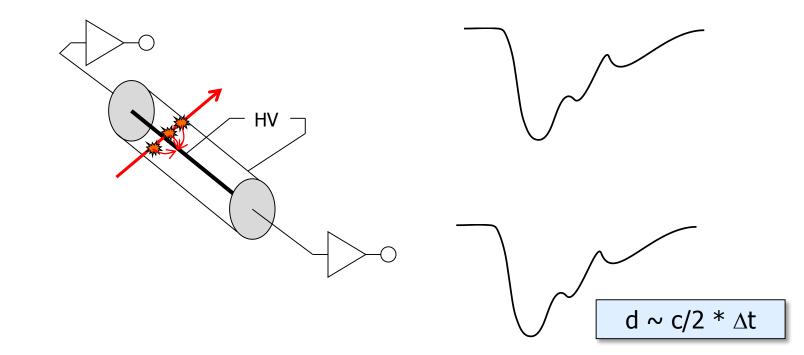

### Positron Emission Tomography

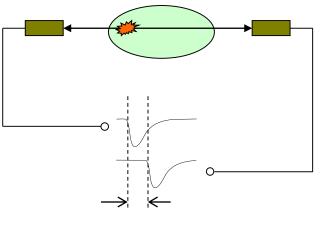

### Time-of-Flight PET

$d \sim c/2 * \Delta t$

e.g. d=1 cm  $\rightarrow \Delta t$  = 67 ps

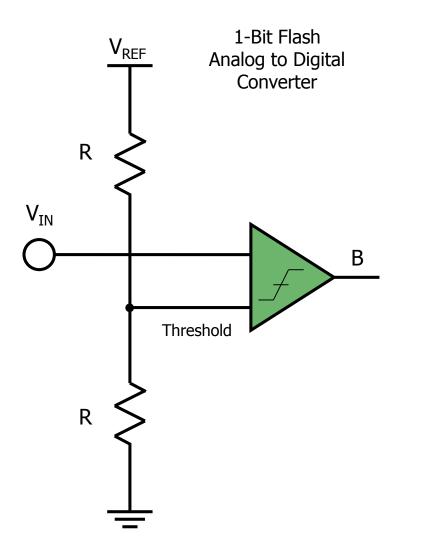

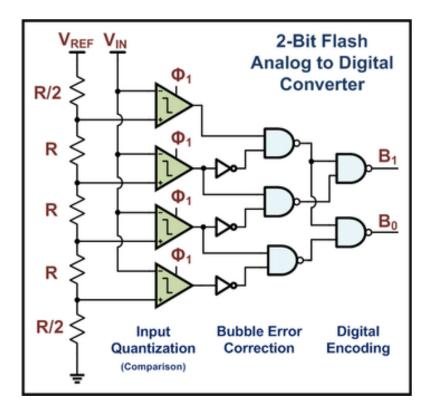

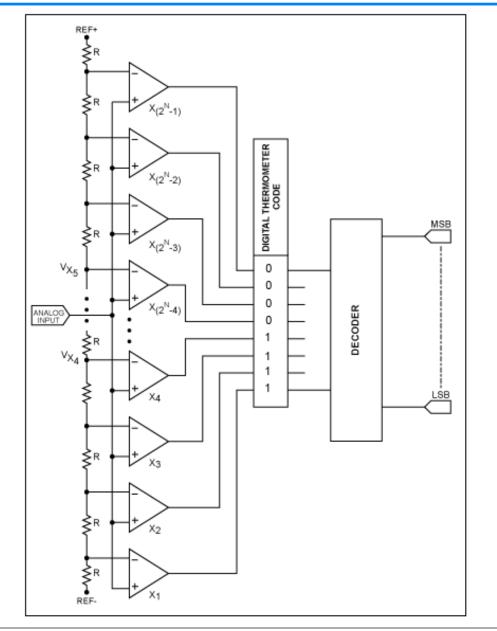

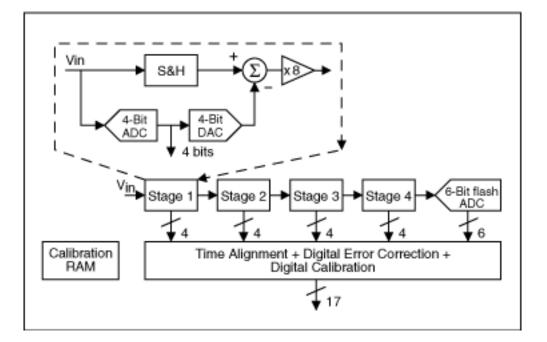

- Flash ADC very fast for small number of bits

- Requires 2<sup>n</sup> comparators

- Combine 4-Bit flash ADC with successive approximation logic

- Only requires 4-Bit flash ADC

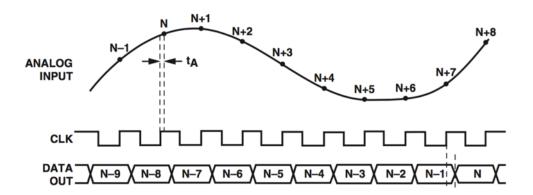

- Can convert one sample in each clock cycle

- Has a latency depending on the number of pipeline stages

- Most common technology for fast ADCs (> 10 MHz)

PAUL SCHERRER INSTITUT

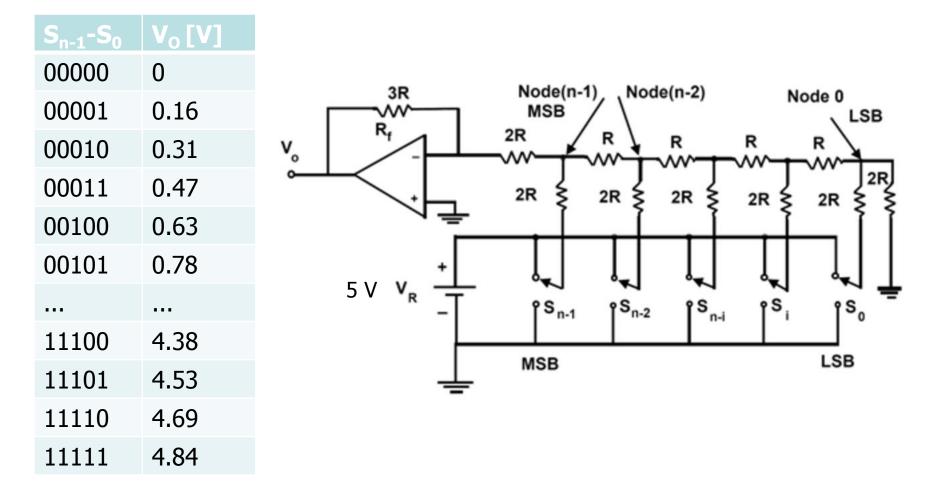

R-2R Ladder:  $0/V_R$  at  $S_0...S_{n-1}$  give binary weighted output  $V_o = S * V_R/32$

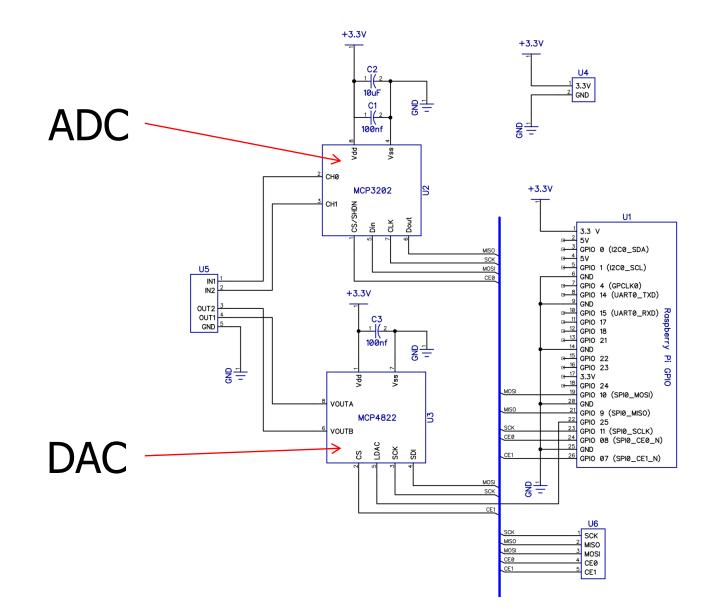

### **DAC Datasheet**

### MCP4821/MCP4822

### 12-Bit DACs with Internal $\mathbf{V}_{REF}$ and SPITM Interface

Description

### Features

- 12-Bit Resolution

- ±0.2 LSb DNL (typ.)

- ±2 LSb INL (typ.)

- Single or Dual Channel

- · Rail-to-Rail Output

- SPI™ Interface with 20 MHz Clock Support

- Simultaneous Latching of the Dual DACs with LDAC pin

- Fast Settling Time of 4.5 µs

- · Selectable Unity or 2x Gain Output

- · 2.048V Internal Band Gap Voltage Reference

- 50 ppm/°C V<sub>REF</sub> Temperature Coefficient

- 2.7V to 5.5V Single-Supply Operation

- Extended Temperature Range: -40°C to +125°C

#### Applications

- · Set Point or Offset Trimming

- Sensor Calibration

- Precision Selectable Voltage Reference

- Portable Instrumentation (Battery-Powered)

- Calibration of Optical Communication Devices

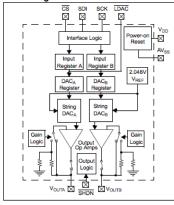

#### Block Diagram

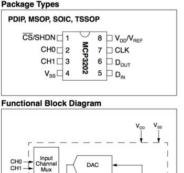

The Microchip Technology Inc. MCP482X devices are 2.7V–5.5V, Iow-power, Iow DNL, 12-bit Digital-to-Analog Converters (DACs) with internal band gap voltage reference, optional 2x-buffered output and Serial Perioheral Interface (SPI™).

The MCP482X family of DACs provide high accuracy and low noise performance for industrial applications where calibration or compensation of signals (such as temperature, pressure and humidity) are required.

The MCP482X devices are available in the extended temperature range and PDIP, SOIC and MSOP packages.

The MCP482X devices utilize a resistive string architecture, with its inherent advantages of low DNL error, low ratio metric temperature coefficient and fast settling time. These devices are specified over the extended temperature range. The MCP482X family includes double-buffered registers, allowing simultaneous updates using the LDAC pin. These devices also incorporate a Power-On Reset (POR) circuit to ensure reliable power-up.

#### Package Types

| 8-Pin PD<br>V <sub>DD</sub> 1<br>CS 2<br>SCK 3<br>SDI 4 | MCP4821 ( 50 | B VOUTA<br>7 AVSS<br>6 SHDN<br>5 LDAC                                      |  |

|---------------------------------------------------------|--------------|----------------------------------------------------------------------------|--|

| 8-Pin PD                                                | IP, SO       | IC, MSOP                                                                   |  |

| V <sub>DD</sub> 1<br><u> CS</u> 2<br>SCK 3<br>SDI 4     | MCP4822 (    | 8 V <sub>OUTA</sub><br>7 AV <sub>SS</sub><br>6 V <sub>OUTB</sub><br>5 LDAC |  |

### MCP4821/MCP4822

### 4.0 GENERAL OVERVIEW

The MCP482X devices are voltage-output string DACs. These devices include rail-to-rail output amplifiers, internal voltage reference, shutdown and reset-management circuitry. Serial communication conforms to the SPI protocol. The MCP482X devices operate from 2.7V to 5.5V supplies.

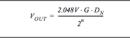

The coding of these devices is straight binary, with the ideal output voltage given by Equation 4-1, where G is the selected gain (1x or 2x),  $D_N$  represents the digital input value and n represents the number of bits of resolution (n = 12).

#### EQUATION 4-1: LSb SIZE

1 LSb is the ideal voltage difference between two successive codes. Table 4-1 illustrates how to calculate LSb.

| TABLE 4-1: | LSb SIZES |

|------------|-----------|

|------------|-----------|

| Device  | Gain | LSb Size    |

|---------|------|-------------|

| MCP482X | 1x   | 2.048V/4096 |

| MCP482X | 2x   | 4.096V/4096 |

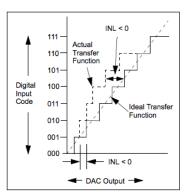

### 4.0.1 INL ACCURACY

INL error for these devices is the maximum deviation between an actual code transition point and its corresponding ideal transition point once offset and gain errors have been removed. These endpoints are from 0x000 to 0xFFF. Refer to Figure 4-1.

Positive INL represents transition(s) later than ideal. Negative INL represents transition(s) earlier than ideal.

FIGURE 4-1: INL Accuracy

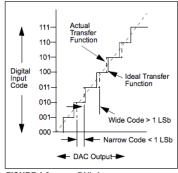

4.0.2 DNL ACCURACY

DNL error is the measure of variations in code widths from the ideal code width. A DNL error of zero would imply that every code is exactly 1 LSb wide.

FIGURE 4-2: DNL Accuracy.

4.0.3 OFFSET ERROR

Offset error is the deviation from zero voltage output when the digital input code is zero.

#### 4.0.4 GAIN ERROR

Gain error is the deviation from the ideal output,  $V_{REF} - 1$  LSb, excluding the effects of offset error.

© 2005 Microchip Technology Inc.

DS21953A-page 1

© 2005 Microchip Technology Inc.

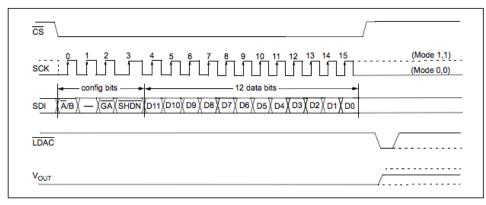

## Write Command

| Upper Half | f:  |     |      |     |     |     |       |

|------------|-----|-----|------|-----|-----|-----|-------|

| W-x        | W-x | W-x | W-0  | W-x | W-x | W-x | W-x   |

| A/B        | —   | GA  | SHDN | D11 | D10 | D9  | D8    |

| bit 15     |     |     |      |     |     |     | bit 8 |

| Lower Half |     |     |     |     |     |     |       |

|------------|-----|-----|-----|-----|-----|-----|-------|

| W-x        | W-x | W-x | W-x | W-x | W-x | W-x | W-x   |

| D7         | D6  | D5  | D4  | D3  | D2  | D1  | D0    |

| bit 7      |     |     |     |     |     |     | bit 0 |

- A/B: DACA or DACB Select bit bit 15

- 1 = Write to DAC<sub>B</sub>

- 0 = Write to DACA

- bit 14 Don't Care \_

- GA: Output Gain Select bit bit 13

- $1 = 1x (V_{OUT} = V_{REF} * D/4096)$  $0 = 2x (V_{OUT} = 2 * V_{REF} * D/4096)$

- bit 12 SHDN: Output Power-down Control bit

- 1 = Output Power-down Control bit

- 0 = Output buffer disabled, Output is high-impedance

- bit 11-0 D11:D0: DAC Data bits

12-bit number "D" which sets the output value. Contains a value between 0 and 4095.

| Legend            |                  |                     |                    |

|-------------------|------------------|---------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b | it, read as '0'    |

| -n = Value at POR | 1 = bit is set   | 0 = bit is cleared  | x = bit is unknown |

### **ADC Datasheet**

### MCP3202

### 2.7V Dual Channel 12-Bit A/D Converter with SPI Serial Interface

#### Features

- 12-bit resolution

- · ±1 LSB max DNL

- ±1 LSB max INL (MCP3202-B)

- ±2 LSB max INL (MCP3202-C)

- Analog inputs programmable as single-ended or pseudo-differential pairs

- On-chip sample and hold

- · SPI serial interface (modes 0,0 and 1,1)

- Single supply operation: 2.7V-5.5V

- 100 ksps max. sampling rate at V<sub>DD</sub> = 5V

- 50 ksps max. sampling rate at V<sub>DD</sub> = 2.7V

- Low power CMOS technology

- 500 nA typical standby current, 5 μA max.

- 550 µA max. active current at 5V

- Industrial temp range: -40°C to +85°C

- · 8-pin MSOP, PDIP, SOIC and TSSOP packages

### Applications

- · Sensor Interface

- Process Control

- · Data Acquisition

- · Battery Operated Systems

#### Description

The Microchip Technology Inc. MCP3202 is a successive approximation 12-bit Analog-to-Digital (A/D) Converter with on-board sample and hold circuitry. The MCP3202 is programmable to provide a single pseudodifferential input pair or dual single-ended inputs. Differential Nonlinearity (DNL) is specified at ±1 LSB, and Integral Nonlinearity (INL) is offered in ±1 LSB (MCP3202-B) and ±2 LSB (MCP3202-C) versions. Communication with the device is done using a simple serial interface compatible with the SPI protocol. The device is capable of conversion rates of up to 100 ksps at 5V and 50 ksps at 2.7V. The MCP3202 device operates over a broad voltage range (2.7V-5.5V). Lowcurrent design permits operation with typical standby and active currents of only 500 nA and 375 µA, respectively. The MCP3202 is offered in 8-pin MSOP, PDIP, TSSOP and 150 mil SOIC packages.

Control Logic

CS/SHDN DN CLK

Sample and Hold

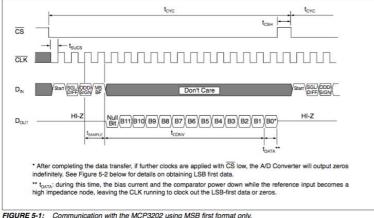

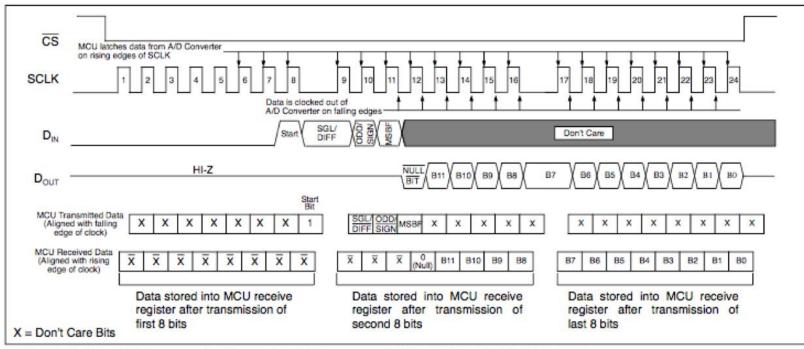

### SERIAL COMMUNICATIONS

#### 5.1 Overview

5.0

Communication with the MCP3202 is done using a standard SPI-compatible serial interface. Initiating communication with the device is done by bringing the CS line low. See Figure 5-1. If the device was powered up with the CS pin low, it must be brought high and back low to initiate communication. The first clock received with CS low and DIN high will constitute a start bit. The SGL/DIFF bit and the ODD/SIGN bit follow the start bit and are used to select the input channel configuration. The SGL/DIFF is used to select single ended or psuedo-differential mode. The ODD/SIGN bit selects which channel is used in single ended mode, and is used to determine polarity in pseudo-differential mode. Following the ODD/SIGN bit, the MSBF bit is transmitted to and is used to enable the LSB first format for the device. If the MSBF bit is high, then the data will come from the device in MSB first format and any further clocks with CS low will cause the device to output zeros. If the MSBF bit is low, then the device will output the converted word LSB first after the word has been transmitted in the MSB first format. See Figure 5-2. Table 5-1 shows the configuration bits for the MCP3202. The device will begin to sample the analog input on the second rising edge of the clock, after the start bit has been received. The sample period will end on the falling edge of the third clock following the start bit

On the falling edge of the clock for the MSBF bit, the device will output a low null bit. The next sequential 12 clocks will output the result of the conversion with MSB first as shown in Figure 5-1. Data is always output from the device on the falling edge of the clock. If all 12 data bits have been transmitted and the device continues to receive clocks while the  $\overline{CS}$  is held low, (and MSBF = 1), the device will output the conversion result LSB first as hown in Figure 5-2. If more clocks are provided to the device while  $\overline{CS}$  is still low (after the LSB first data has been transmitted), the device will clock out zeros indefinitely.

MCP3202

If necessary, it is possible to bring  $\overline{CS}$  low and clock in leading zeros on the  $D_N$  line before the start bit. This is often done when dealing with microcontroller-based SPI ports that must send 8 bits at a time. Refer to Section 6.1 for more details on using the MCP3202 devices with hardware SPI ports.

|                      | Config<br>Bits |              | Channel<br>Selection |     |     |

|----------------------|----------------|--------------|----------------------|-----|-----|

|                      | Sgl/<br>Diff   | Odd/<br>sign | 0                    | 1   | GND |

| Single Ended<br>Mode | 1              | 0            | +                    | -   |     |

|                      | 1              | 1            | -                    | +   | -   |

| Pseudo-              | 0              | 0            | IN+                  | IN- |     |

| DifferentiaL<br>Mode | 0              | 1            | IN-                  | IN+ |     |

TABLE 5-1: Configuration Bits for the MCP3202.

© 2006 Microchip Technology Inc.

© 2006 Microchip Technology Inc.

DS21034D-page 1

12-Bit SAR

Shift

Register

Dout

FIGURE 6-1: SPI Communication using 8-bit segments (Mode 0,0: SCLK idles low).

```

spi_buf[0] = 0x01; // Start

spi_buf[1] = 0xA0; // SGL/DIFF=1, ODD/SING=0, MS/BF=1

spi_buf[2] = 0x00;

wiringPiSPIDataRW(spi_fd0, spi_buf, 3);

// convert to Volts

t = (((spi_buf[1] & 0x0F) << 8) | spi_buf[2])/4096.0 * 3.3;

// convert to deg C (10 mV / deg. C)

t *= 100;

```

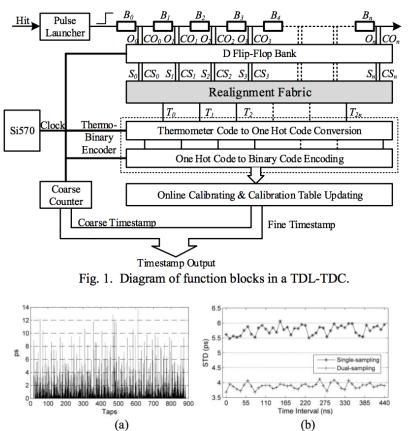

### Real Time 2016 Conference, Padova A 3.9 ps RMS Resolution Time-to-Digital Convertor Using Dual-sampling Method on Kintex UltraScale FPGA

Chong Liu, Yonggang Wang, Peng Kuang, Deng Li, Xinyi Cheng

Fig. 3. (a) Bin width of dual-sampling TDC after bin realignment. (b) RMS resolution of dual-sampling TDC and single-sampling TDC.

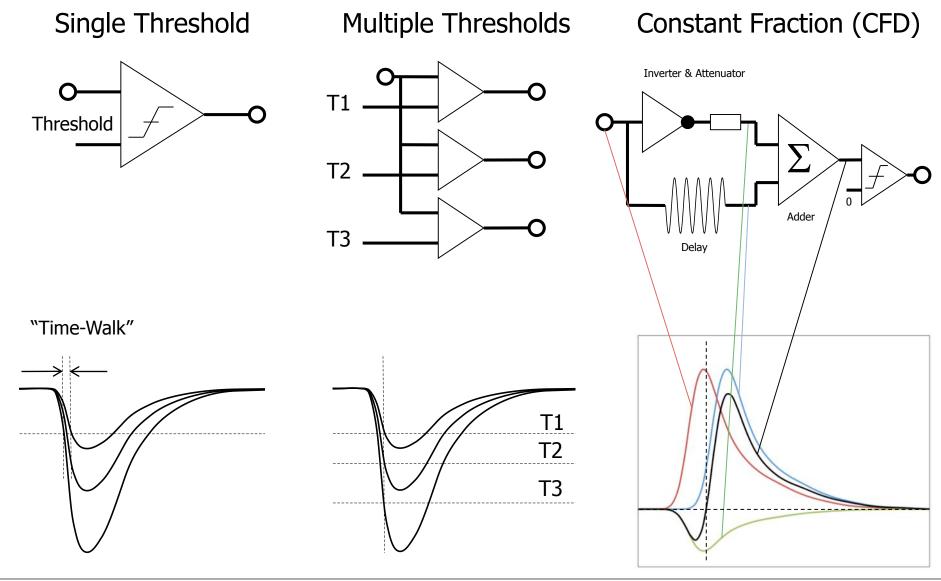

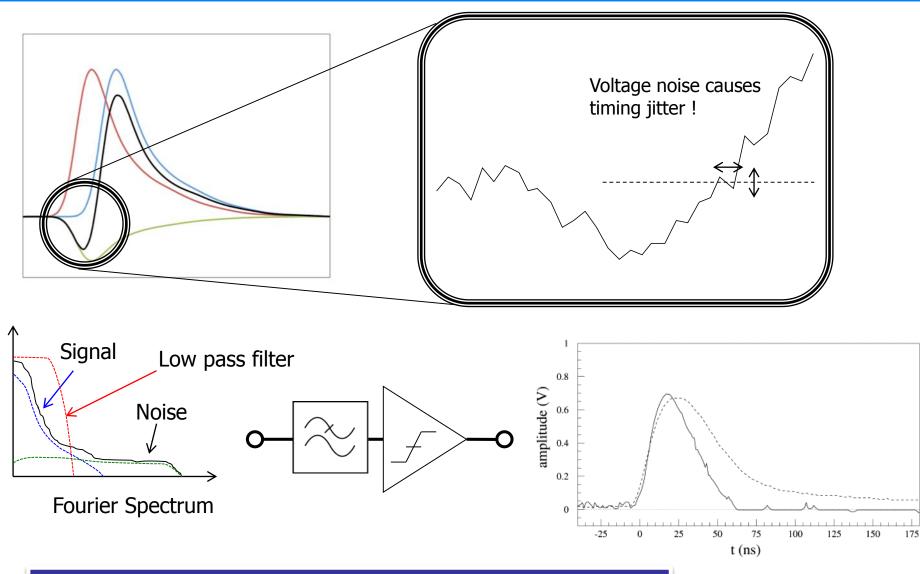

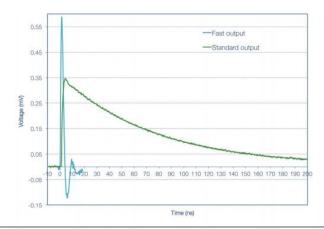

## **Influence of noise**

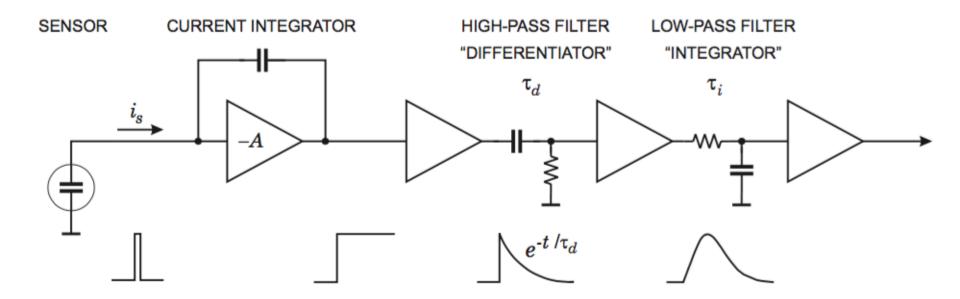

Low pass filter (shaper) reduces noise while maintaining most of the signal

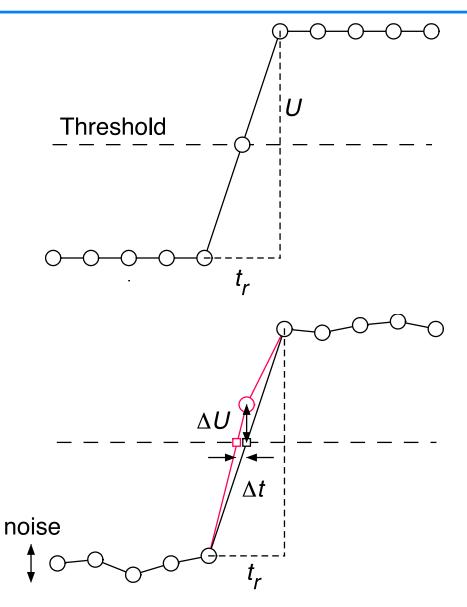

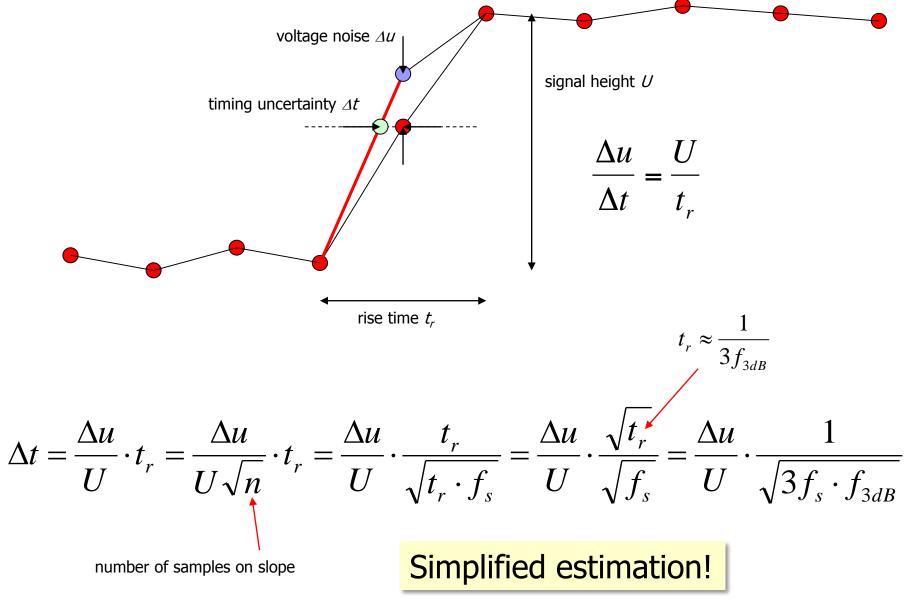

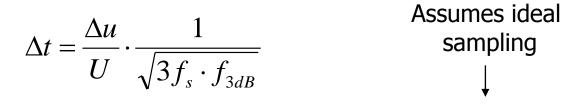

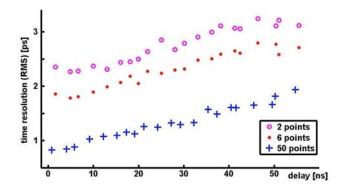

# **Noise limited time accuracy**

$$\frac{\mathsf{D}U}{\mathsf{D}t} \approx \frac{U}{t_r} \longrightarrow \mathsf{D}t = \frac{\mathsf{D}U}{U} \cdot t_r$$

All values in this talk are  $\sigma$  (RMS) ! FHWM = 2.35 x  $\sigma$

| U [mV] | ∆U<br>[mV] | t <sub>r</sub> | Δ <b>t</b> |

|--------|------------|----------------|------------|

| 100    | 1          | 1 ns           | 10 ps      |

| 10     | 1          | 3 ns           | 300 ps     |

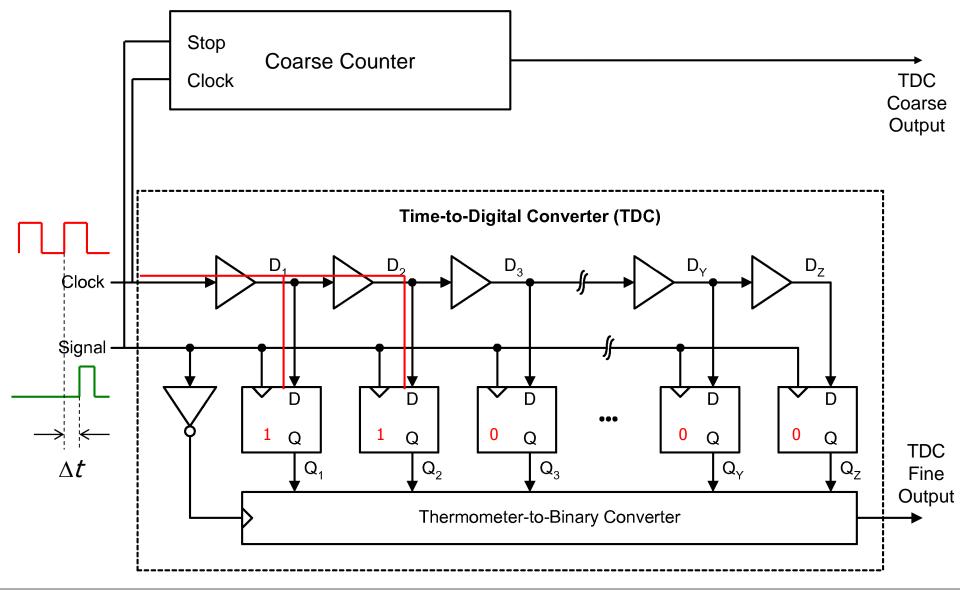

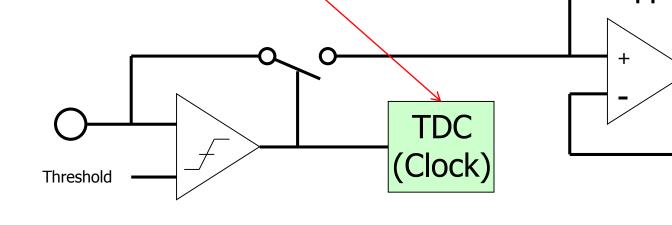

Most today's TDCs have ~20 ps LSB

How can we do better ?

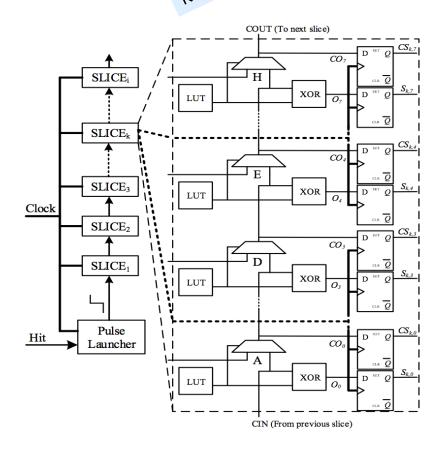

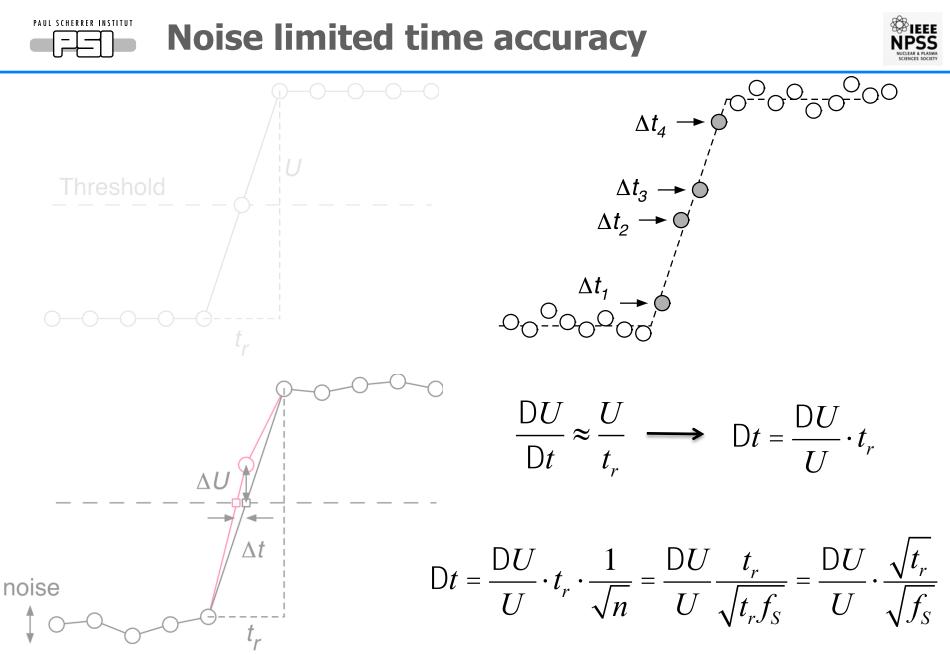

# **Example: CFG in FPGA**

<sup>B</sup>IEEE PSS

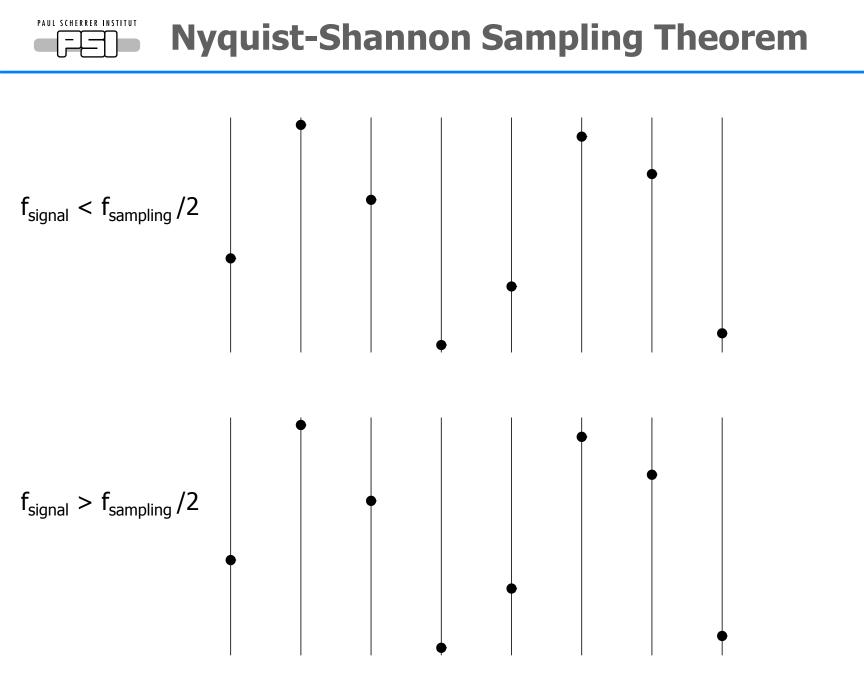

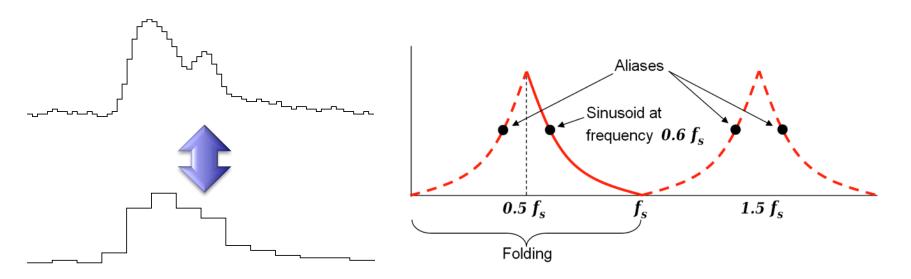

- Aliasing Occurs if  $f_{signal} > 0.5 * f_{sampling}$

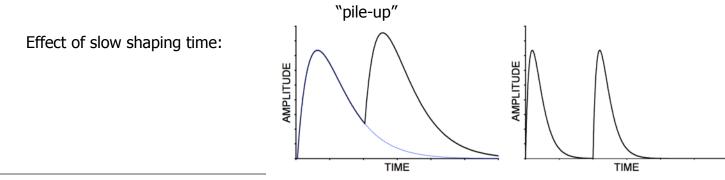

- Features of the signal can be lost ("pile-up")

- Measurement of time becomes hard

- ADC resolution limits energy measurement

- Need very fast high resolution ADC

ADC

~MHz

PSS

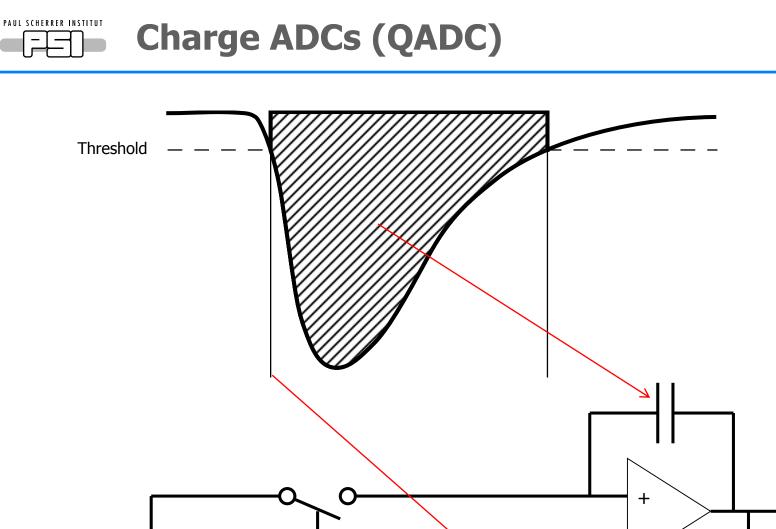

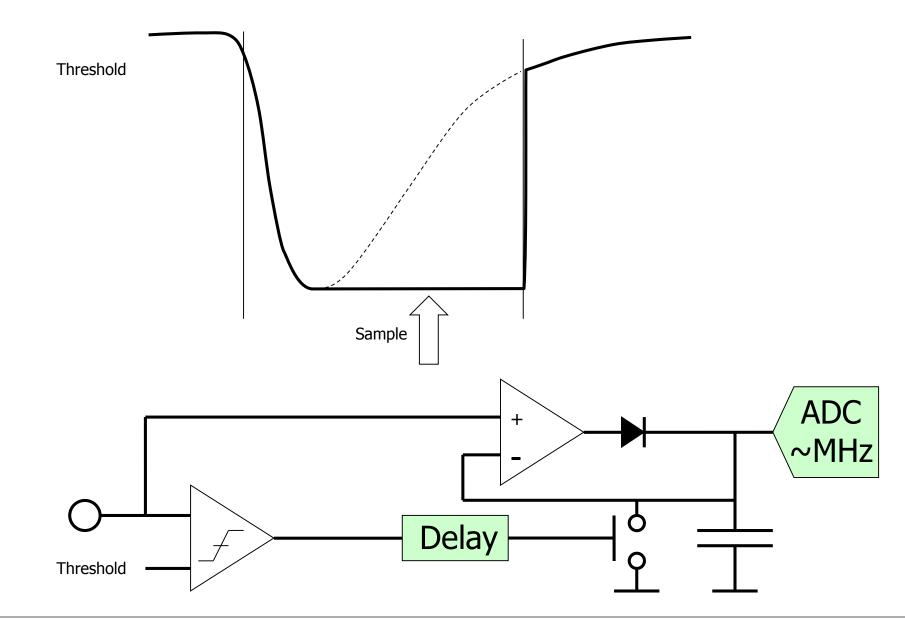

## **Peak sensing ADC**

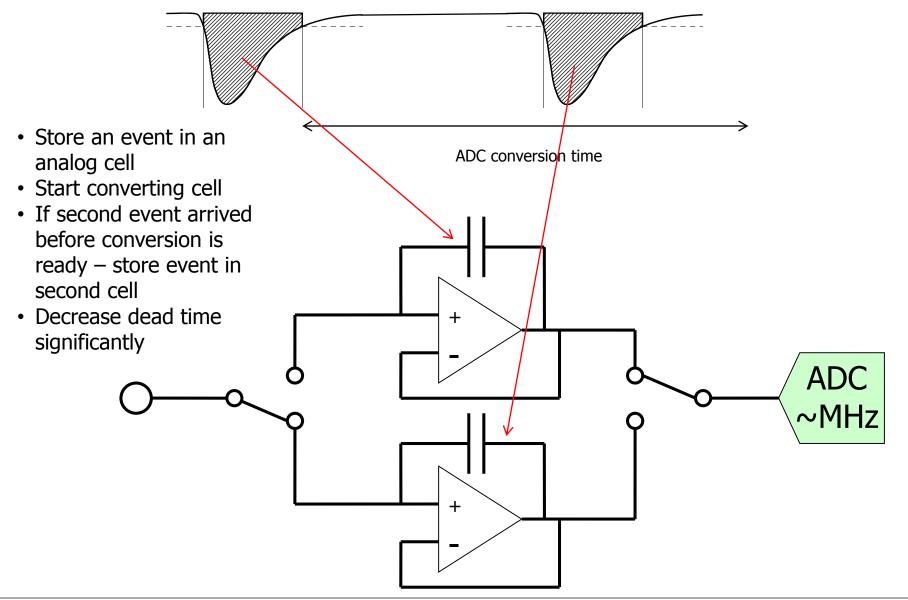

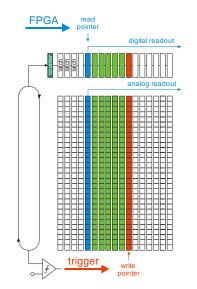

# **Double buffering**

Optimal parameters can greatly improve the signal-to-noise ratio

- Charge integration error due to signal "sitting" on fluctuating baseline (e.g. 50 Hz ground loop or artifact of shaper)

- Can be fixed by sampling baseline prior to signal (requires signal delay)

- Sample signal after peak for pile-up recognition

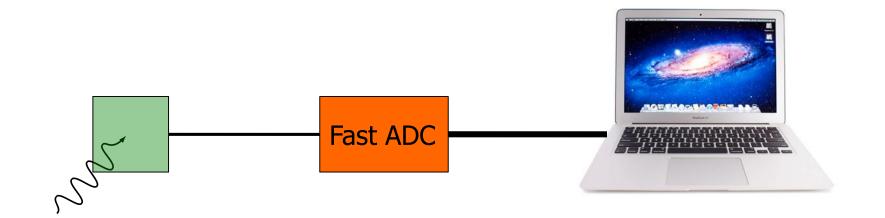

Direct fast sampling without shaping

- No shaping artifacts

- Less electronics

- All information if captured if

- $f_{\text{sampling}} > 2^* f_{\text{signal}} \text{ and } \text{LSB} < V_{\text{noise}}$

- Any shaping circuitry can only *remove* information

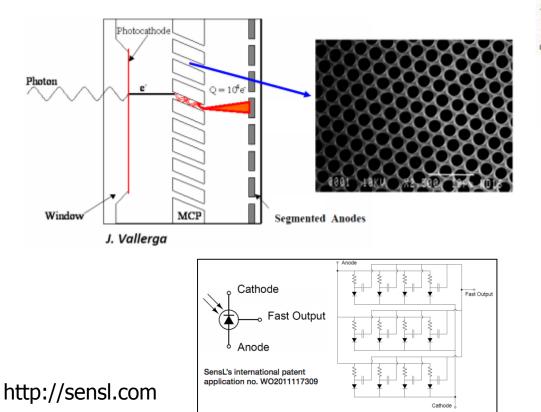

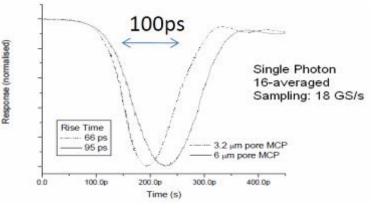

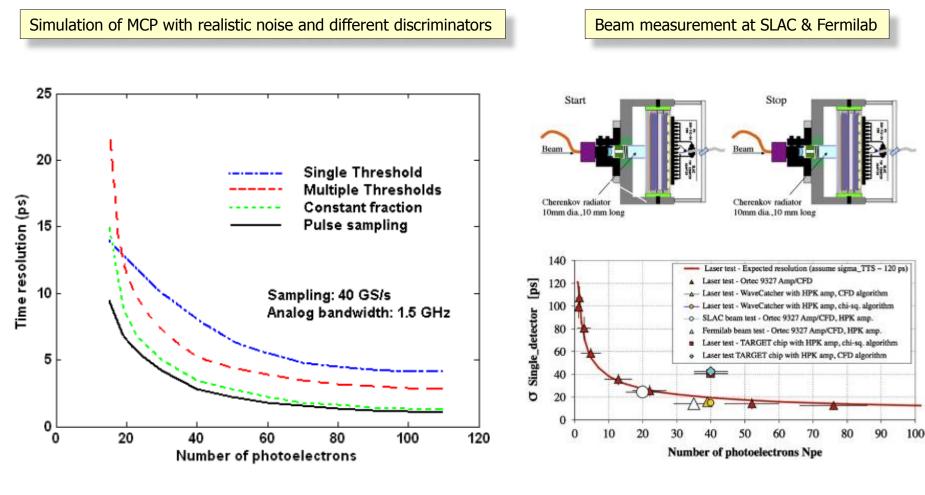

- Micro-Channel-Plates (MCP)

- Photomultipliers with thousands of tiny channels (3-10  $\mu$ m)

- Typical gain of 10,000 per plate

- Very fast rise time down to 70 ps

- 70 ps rise time  $\rightarrow$  **4-5 GHz BW**  $\rightarrow$  **10 GSPS**

- SiPMs (Silicon PMTs) are also getting < 100 ps

J. Milnes, J. Howoth, Photek

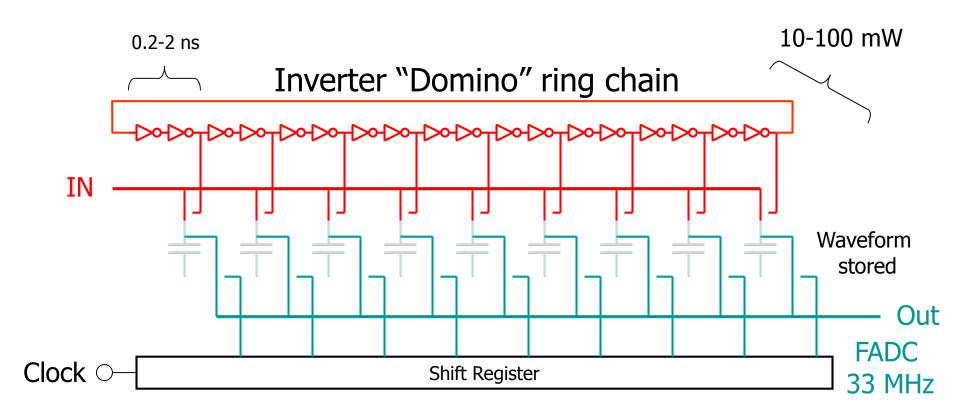

## "Time stretcher" $GHz \rightarrow MHz$

PAUL SCHERRER INSTITUT

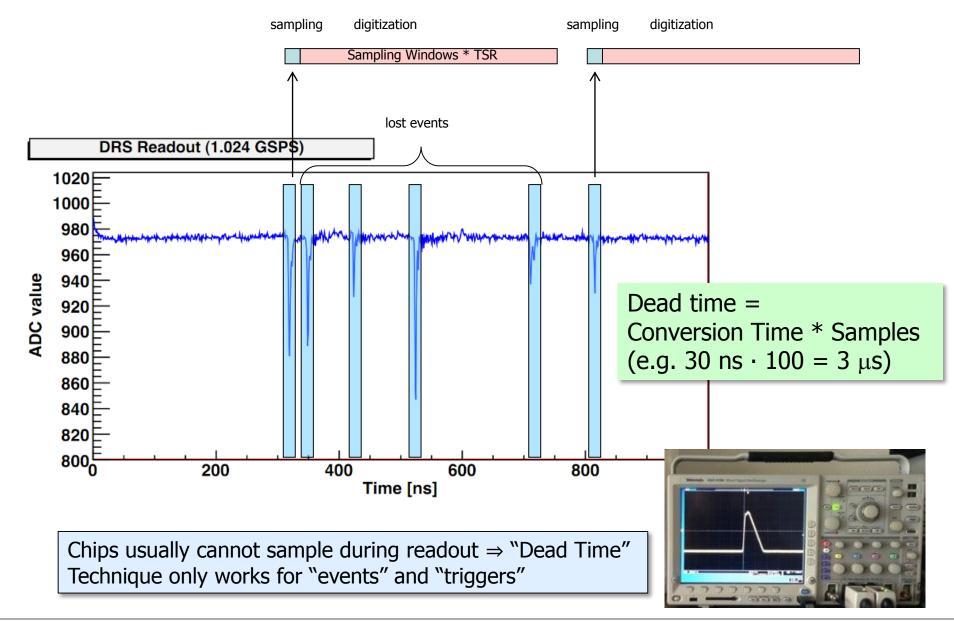

# Triggered Operation

PAUL SCHERRER INSTITUT

J.-F. Genat et al., arXiv:0810.5590 (2008)

D. Breton et al., NIM A629, 123 (2011)

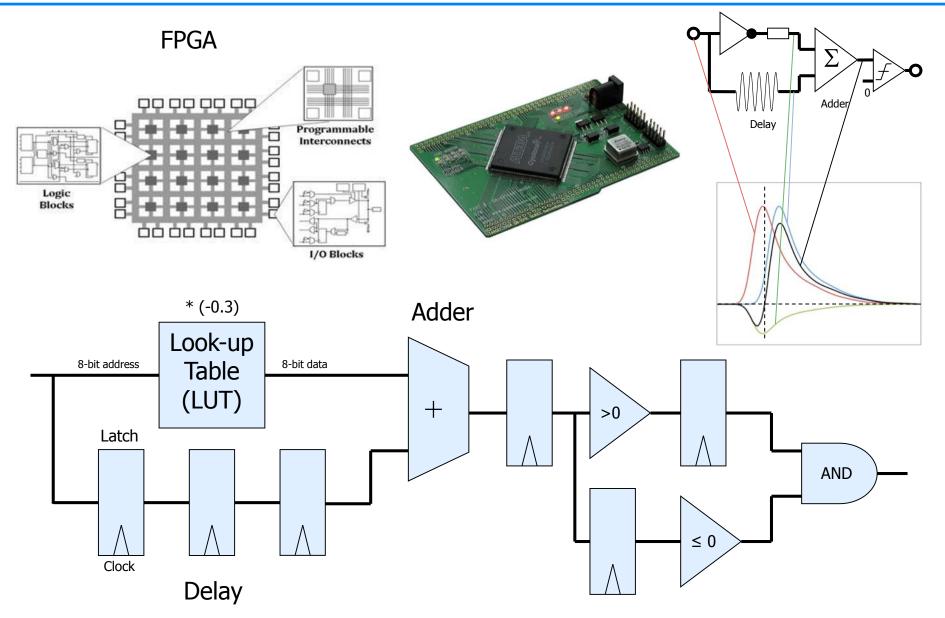

## How is timing resolution affected?

EEE

|                  | U      | $\Delta U$ | $f_{s}$ | f <sub>3db</sub> | Δt     |

|------------------|--------|------------|---------|------------------|--------|

| today:           | 100 mV | 1 mV       | 2 GSPS  | 300 MHz          | ~10 ps |

| optimized SNR:   | 1 V    | 1 mV       | 2 GSPS  | 300 MHz          | 1 ps   |

| next generation: | 1 V    | 1 mV       | 10 GSPS | 3 GHz            | 0.1 ps |

"Novel Calibration Method for Switched Capacitor Arrays Enables Time Measurements width Sub-Picosecond Resolution", D.A. Stricker-Shaver, S. Ritt, B.J. Pichler, IEEE **TNS 61** (2014), 3607

- Readout of straw tubes or drift chambers usually with "charge sharing": 1-2 cm resolution

- Readout with fast timing: 10 ps /  $\sqrt{10}$  = 3 ps  $\rightarrow$  0.5 mm

- Currently ongoing research project at PSI

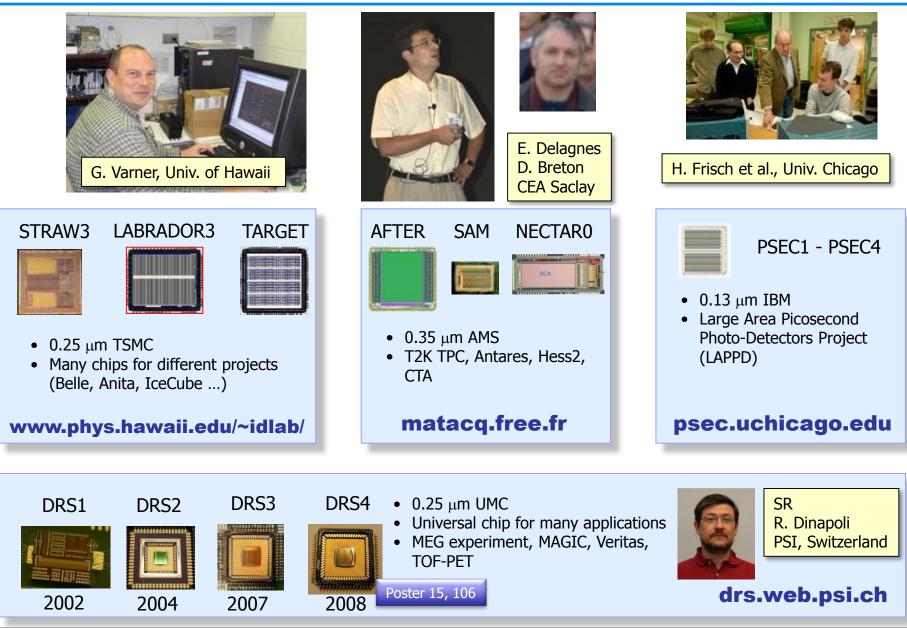

#### **Switched Capacitor Arrays for Particle Physics**

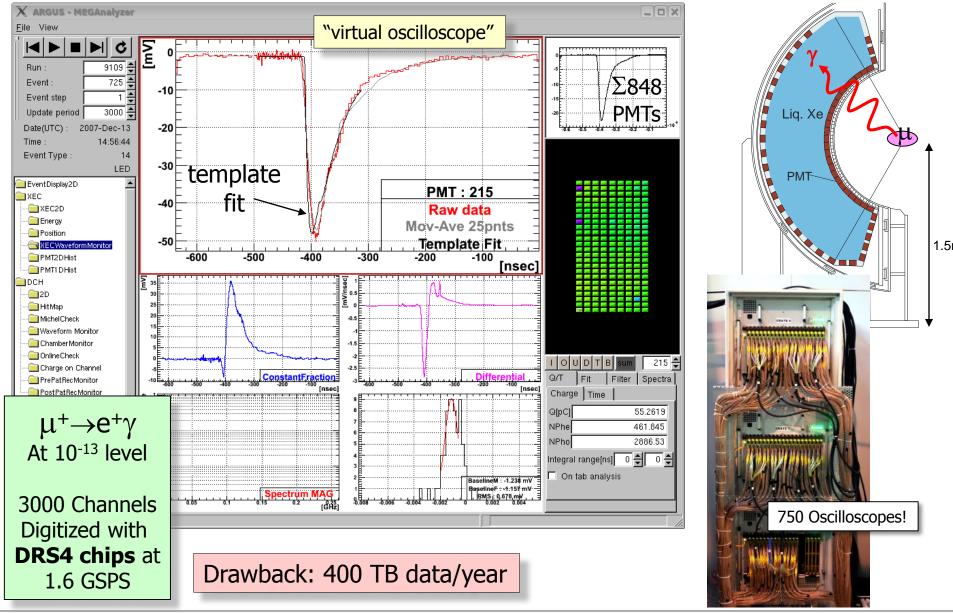

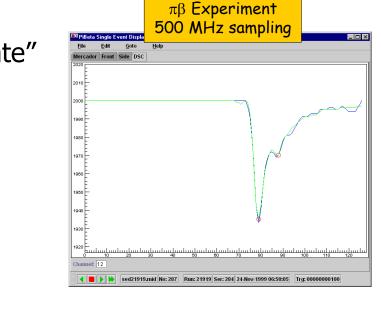

## **MEG On-line waveform display**

Events found and correctly processed 2 years (!) after the were acquired

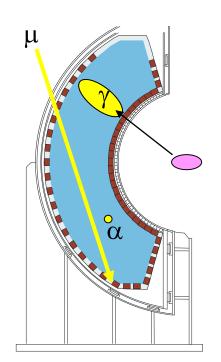

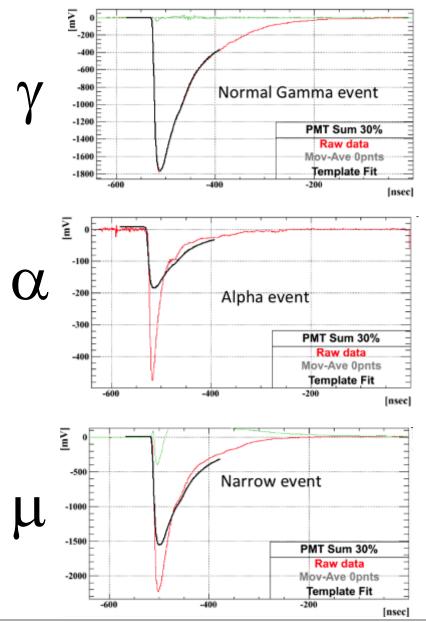

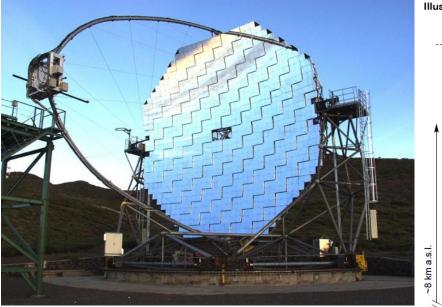

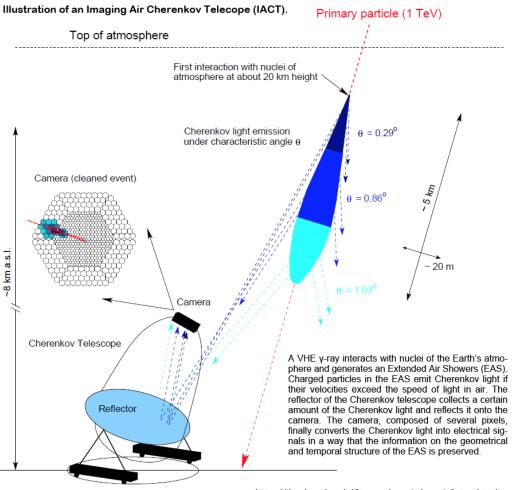

### **MAGIC Telescope**

http://ihp-lx.ethz.ch/Stamet/magic/magicIntro.html

La Palma, Canary Islands, Spain, 2200 m above sea level

https://wwwmagic.mpp.mpg.de/

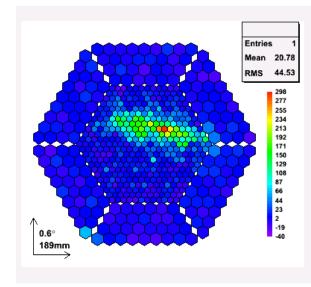

- Determine "standard" PMT pulse by averaging over many events  $\rightarrow$  "Template"

- Find hit in waveform

- Shift ("TDC") and scale ("ADC") template to hit

- Minimize  $\chi^2$

- Compare fit with waveform

- Repeat if above threshold

- Store ADC & TDC values

• At 1,000 kc/s less than 10% of events cannot be decoded.

4 channels 5 GSPS 1 GHz BW 8 bit (6-7) 15 k€

4 channels 5 GSPS 1 GHz BW 11.5 bits 1170 € USB Power

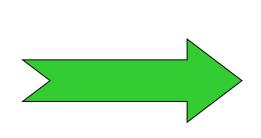

## **New chips**

#### CEA/Saclay

- SAMPIC Waveform TDC

- Record short (64 bins) waveforms

- Digitize on-chip

- Data-driven read out

#### DRS5 (PSI, planned)

- Self-trigger writing of 128 short 32-bin segments (4096 bins total)

- Storage of 128 events

- Accommodate long trigger latencies

- Quasi dead time-free up to a few MHz,

- Possibility to skip segments

- $\rightarrow$  second level trigger

- Digitization is a key element of all particle physics experiments

- General trend to faster digitization and waveform analysis in digital domain (embedded CPUs, FPGAs)

- This talk can only give you a glimpse

## • Further information

Summary

- H. Spieler, "Semiconductor Detector Systems", Oxford Univ. Press, 2005

- G. Knoll, "Radiation Detection and Measurement", Wiley, 2010

- Conferences (with short courses): IEEE NSS-MIC (Strasbourg, France, Nov. 2016) IEEE Realtime (Williamsburg, VA, June 2018)

- Become IEEE NPSS member

PAUL SCHERRER INSTITUT

# The IEEE Nuclear and Plasma Sciences (NPSS) Distinguished Lecturers Program

- Provides high quality scientific and technical lectures on a broad range of topics in the nuclear and plasma sciences

- Sponsors the presentation of lectures to NPSS-affiliated chapters, IEEE sections, and IEEE student chapters

- Makes lectures available to other IEEE entities as well as to non-IEEE organizations, including colleges and universities

For more information, go to www.ieee-npss.org

## NPSS IS THE TECHNICAL SOCIETY THAT COVERS...

- --- Computer Applications in Nuclear and Plasma Sciences

- --- Fusion Technology

- --- Nuclear Medical and Imaging Sciences

- --- Particle Accelerator Science and Technology

- --- Plasma Science and Applications

- --- Pulsed Power Science and Technology

- --- Radiation Effects

- --- Radiation Instrumentation

For more information, go to **www.ieee-npss.org**

$\bullet$

## The Nuclear and Plasma Society Sponsors...

- Radiation Instrumentation (Nuclear Science Symposium)

- Nuclear Medical and Imaging Sciences (Medical Imaging Conference)

- Particle Accelerator Science and Technology (Particle Accelerator Content of Content o

- Computer Applications in Nuclear and Plasma Sci. (Real-Time Conference)

- Radiation Effects (Nuclear and Space Radiation Effects Conference)

- Plasma Science and Applications (International Conference on Plasma

- Fusion Technology (Symposium on Fusion Engineering)

Pulsed Power Science and Technology (Pulsed Power Conference)

*IEEE Transactions on Nuclear Science IEEE Transactions on Plasma Science*

For more information, go to www.ieee-npss.org

## WHY JOIN THE IEEE NPSS?

- Membership in NPSS provides regular communication and direct technical interchange with the foremost international practitioners of the nuclear and plasma sciences and engineering through its meetings and publications

- NPSS Members and Affiliates receive:

- Electronic access to the Transactions on Nuclear Science, the Transactions on Plasma Science, and all NPSS Conference Records via Xplore

- NPSS Newsletter published four times per year

- Reduced rates on print subscriptions to NPSS publications

- Significant discounts on registration rates for NPSS Conferences

- As IEEE members, they also receive:

- Subscriptions to the monthly magazine SPECTRUM and also

- The Institute, a monthly news supplement

- Low rates on IEEE's many publications

For more information, go to **www.ieee-npss.org**