# HVCMOS sensor technology R&D

LUIGI VIGANI INFIERI WORKSHOP FERMILAB, 18/10/2016

# Current status of LHC pixel detectors

# **Standard Planar Silicon Detectors**

- Complex signal processing

- ✓ 25 ns in-time efficiency

- ✓ Radiation hard (≈  $5x10^{15} n_{eq}$  /cm<sup>2</sup>)

- ✓ High rate capability (≈MHz/mm<sup>2</sup>)

- ✓ Good spatial resolution (≈10÷15 µm)

- High efficiency (>99%)

- x Large material budget

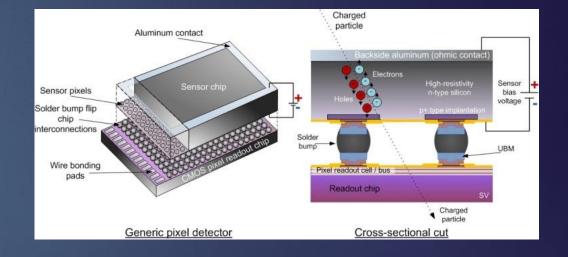

- x Complex and laborious module production

- x bump-bonding / flip-chip

- x Many production steps

**Expensive**

# CMOS technology: an alternative

- Commercial process

- Mature

- Cheap

- Allows for Monolithic Pixels

- ► No hybridization

- Wafer scale processes

- Can achieve very small sizes

- ► O(25x25 µm²)

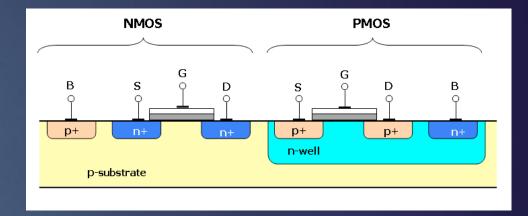

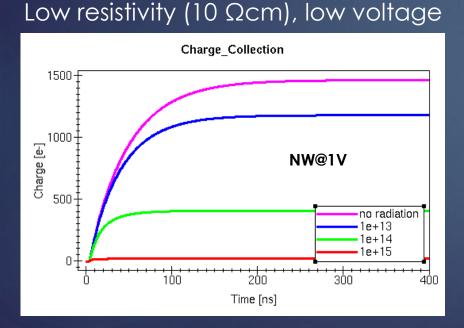

- CMOS Standard: low voltage, low resistivity

- No depletion region -> Charge collection only by diffusion (no drift)

- Small signal

- ► Slow

# CMOS technology: LHC requirements 4

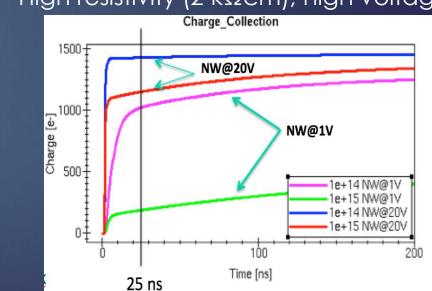

- Fast charge collection (< 25ns "in-time" efficient)</p>

- Reasonably large signal (~4000 e-)

- Short collection distance to avoid trapping (rad hardness)

### High resistivity (2 kΩcm), high voltage

Simulations by Tomasz Hemperek (Bonn)

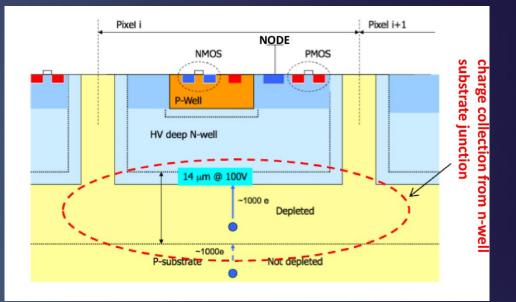

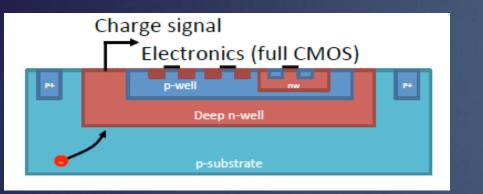

# CMOS technology: add-ons

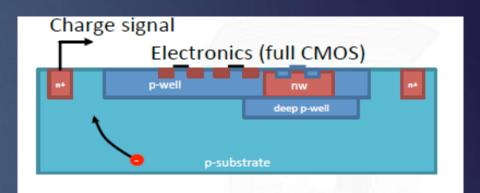

CMOS component inserted inside deep N-well

- Isolation from high voltage

- Depletion region created between deep N-well and backside of p-substrate

- High resistivity wafers

- Multiple nested wells

- Backside processing

# CMOS technology: configurations

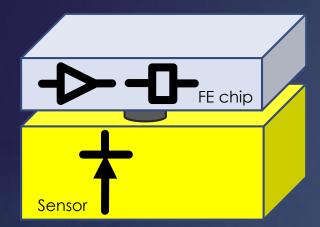

Standard Hybrid CMOS passive sensor

**CMOS Passive Pixels**

FE chip FE chip FE chip Preamp

**CMOS active Hybrid** Bump-bonded or glued

CMOS Strip Project (Chess)

6

Fully monolithic

**CCPD** Detectors

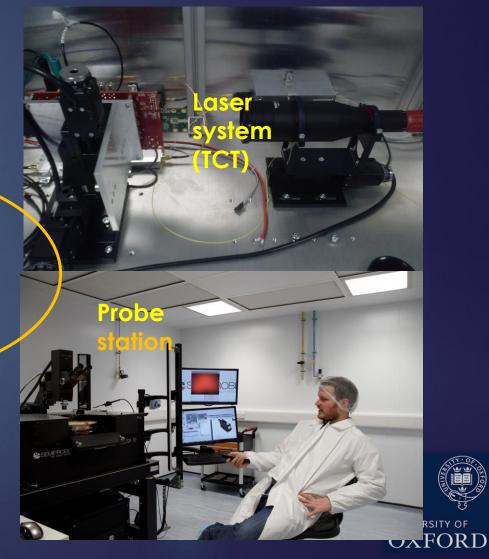

# Oxford Physics Microstructure Detector facility

Two clean rooms: • Class 10k (ISO7) 120 m<sup>2</sup> • class 100 (ISO5) 40 m<sup>2</sup>

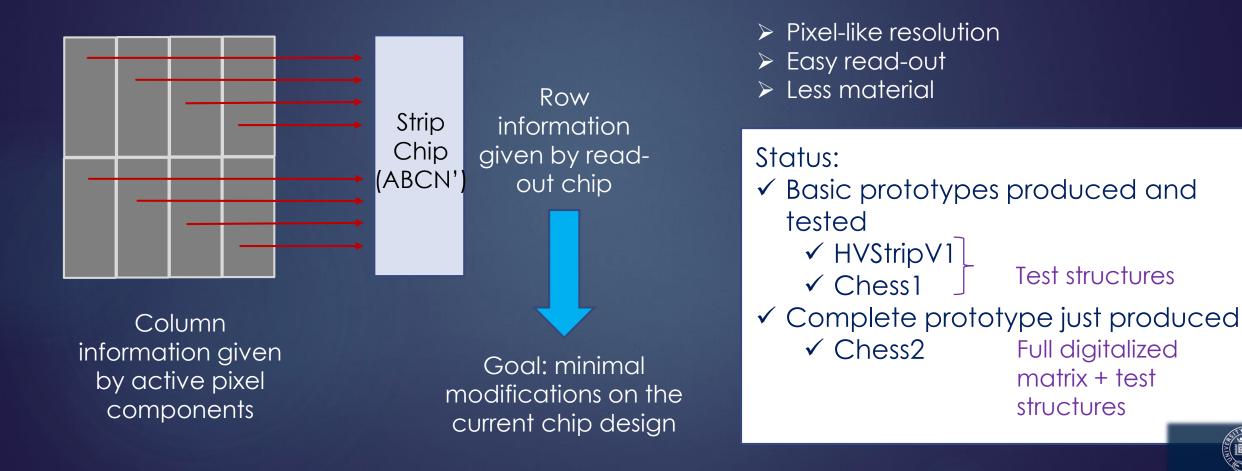

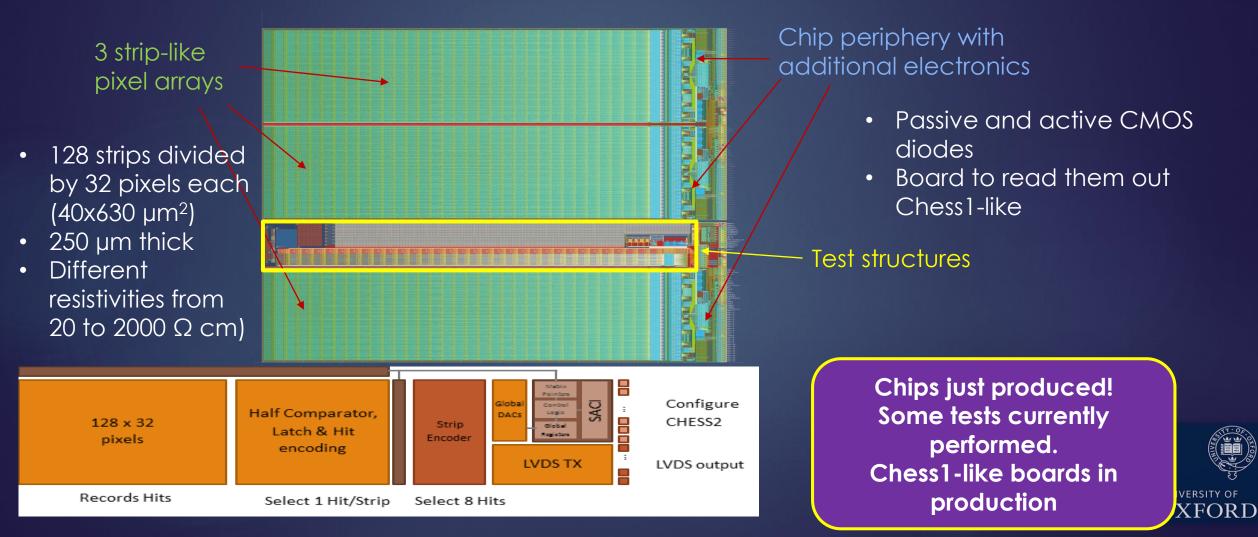

# CMOS Strip

# "Strixels" Concept

UNIVERSITY OF

# CMOS Strip: HVStripV1

AMS35 Technology

22x2 channels, 40x400 µm<sup>2</sup> each

- ▶ 750 µm total thickness

- 5  $\Omega$  cm resistivity

- Up to 80 V bias

I. Peric

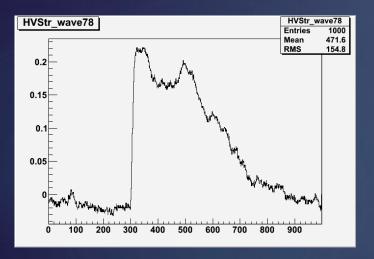

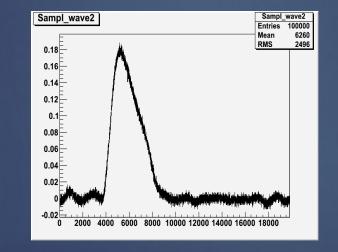

Only analogue output investigated (one channel at a time)

(Bias 60 V)

(Noise ≈70e-)

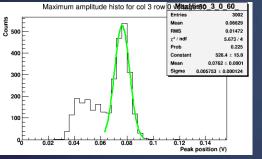

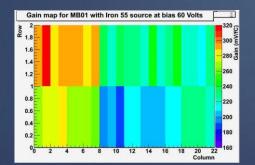

### Fe<sup>55</sup> characterization

Single spectrum

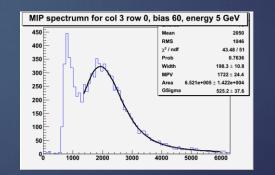

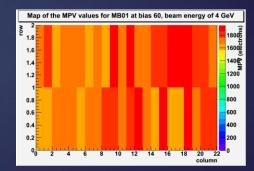

### Test Beam at DESY (3 GeV electrons)

### Single spectrum

MPV map

Charge Most Probable Value

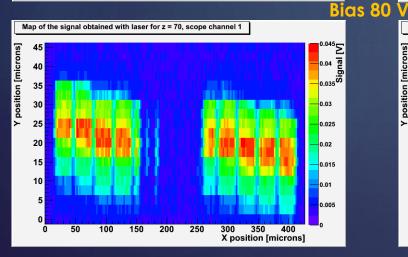

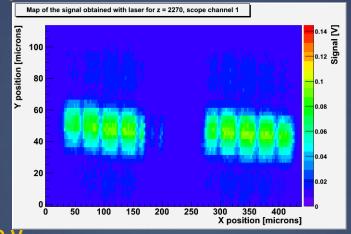

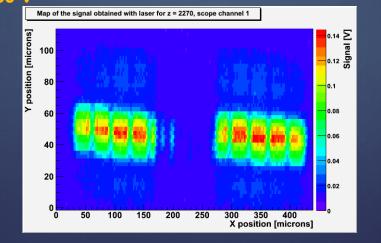

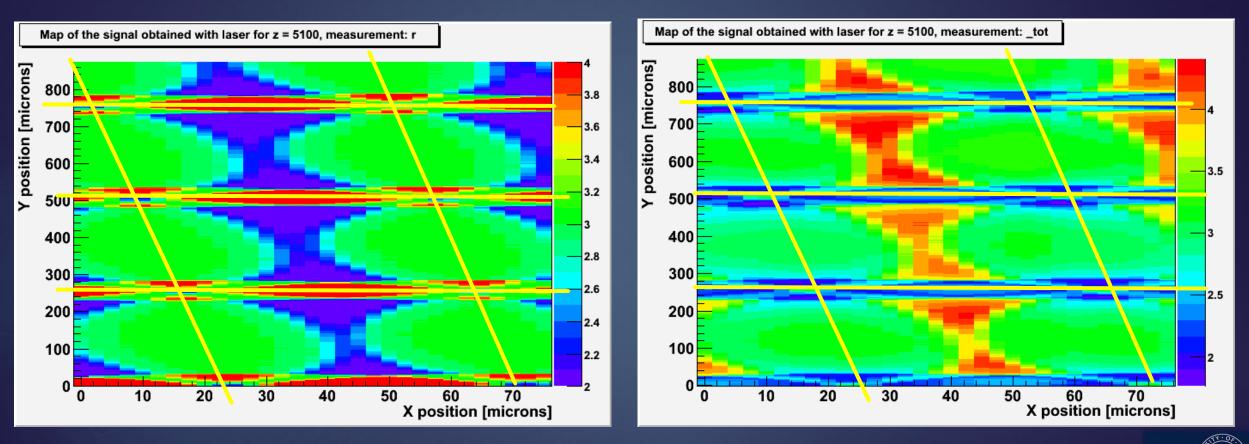

# CMOS Strip: HVStripV1 Laser characterization

# 11

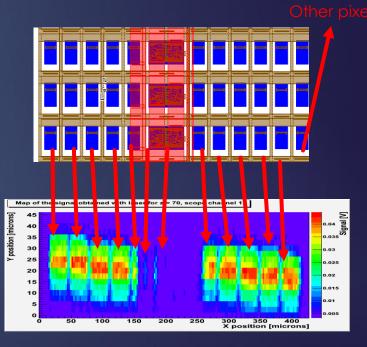

### Red Laser (640nm) Bias 10 V Map of the signal obtained with laser for z = 70, scope channel 1 <sup>0.045</sup>∑ 45 position [microns] 0.04 0.035 [micr 40 35 position 0.03 30 25 0.025 ≻ ≻ 20 0.02 0.015 0.01 0.005 200 250 400 0 50 100 150 300 350 X position [microns]

### Infrared Laser (1060nm)

### Matching with design

# CMOS Strip: HVStripV1

# 12

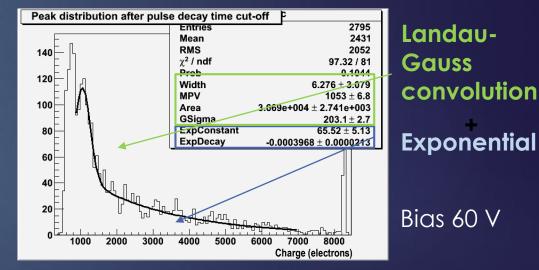

### Irradiation

- Birmingham: 27 MeV protons from the cyclotron

- Fluence of about 8x10<sup>14</sup> n<sub>eq</sub>/cm<sup>2</sup>

### Signal significantly degraded after irradiation

Recovered after annealing and changing of DACs

### Despite noise, Landau peak observed with Sr<sup>90</sup> (Cambridge)

- Exponential function to parameterize the observed background

- MIP peak observed, lower MPV than

unirradiated (~60%)

OXFORD

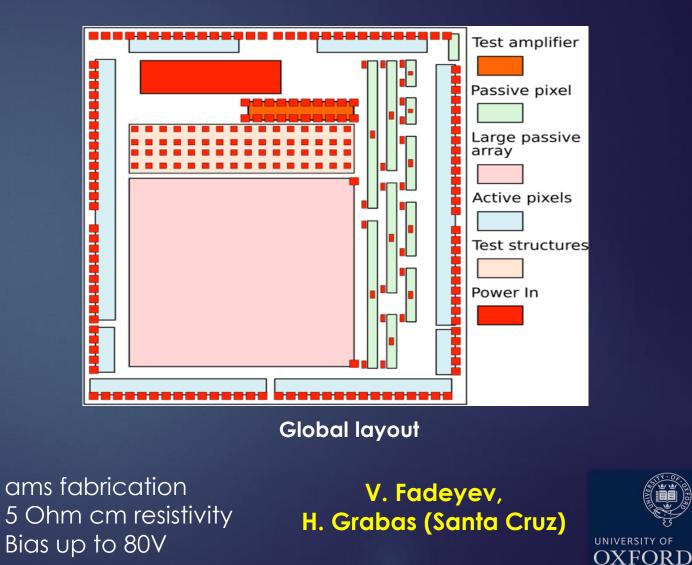

- Complex device with many different structures

- We focus on Active Pixel Arrays (APA)

- 72 channels in total, divided in 8 types (APA1,...,APA8)

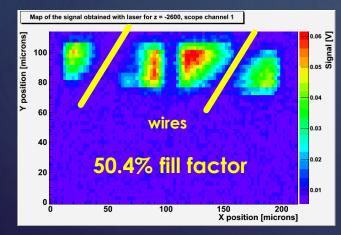

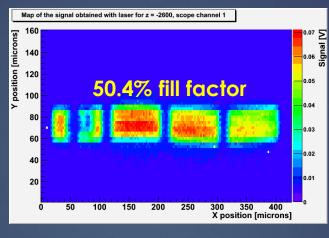

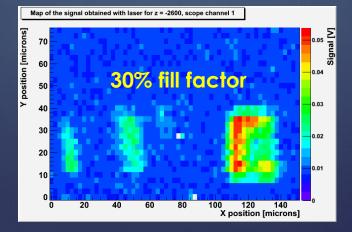

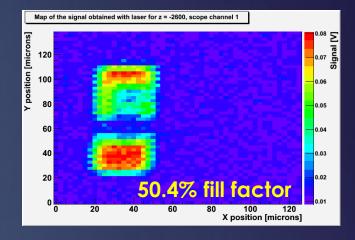

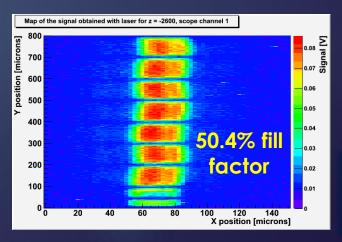

| APA # | Pixel size            | Fill Factor |

|-------|-----------------------|-------------|

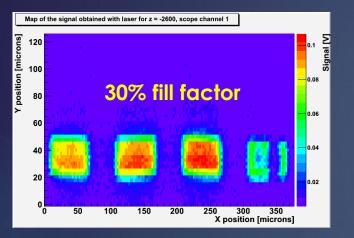

| APA01 | 45x100µm <sup>2</sup> | 30%         |

| APA02 | 45x100µm <sup>2</sup> | 50.4%       |

| APA03 | 45x200µm <sup>2</sup> | 30%         |

| APA04 | 45x200µm <sup>2</sup> | 50.4%       |

| APA05 | 45x400µm <sup>2</sup> | 30%         |

| APA06 | 45x400µm <sup>2</sup> | 50.4%       |

| APA07 | 45x800µm <sup>2</sup> | 30%         |

| APA08 | 45x800µm <sup>2</sup> | 50.4%       |

•

•

•

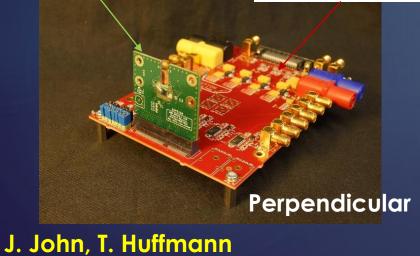

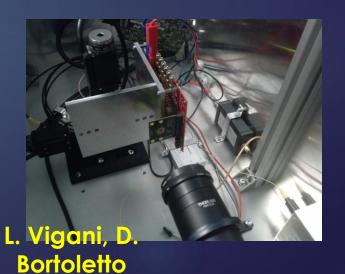

### Laser characterization

### Read out system:

- Motherboard + Daughterboard

- 10 channels readable at the same time

- 6 DACs to regulate

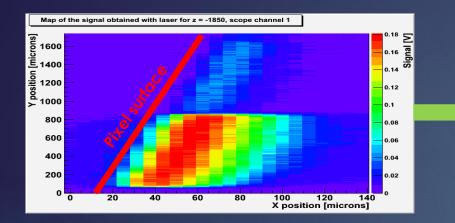

### **Edge TCT**

### Daughterboard

(Oxford)

### **Motherboard**

Parallel

Two configurations of mother-daughterboard connection for 2 different laser scans

14

**Front TCT**

UNIVERSITY OF **OXFORD**

### Front TCT

### APA5

APA4

### APA6

APA3

### APA2

APA8

UNIVERSITY OF OXFORD

### **Edge TCT**

APA8 (800 µm pitch on that side)

Slightly tilted about laser axis (less than 2 degrees)

Slow DAC configuration: mainly diffusion

Sharing with nearby pixel

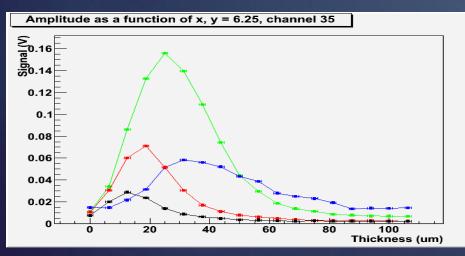

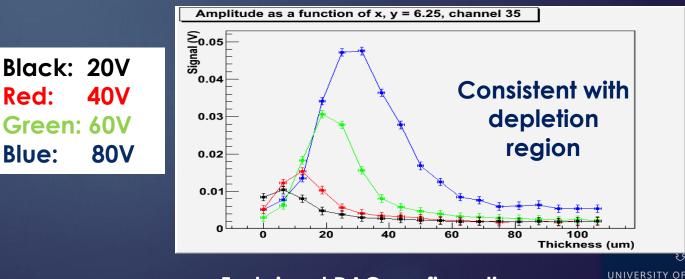

### Signal as a function of depth, bias dependence:

Fast signal DAC configuration

OXFORD

Slow signal DAC configuration

17

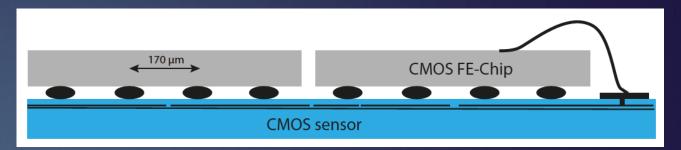

First example of monolithic CMOS sensor for a strip detector

# C4 bumps: come with chip fabrication at low cost

- No fine-pitch bumping

- Flip-chipping in-house (large pitch)

- Cheap large feature size technology

- Large sensors

- Wafer based flip-chipping

- Can have in-pixel AC coupling and voltage redistribution layers

Prototype with 2 areas to test 2 coupling alternatives

T. Hemperek, F. Hugging, H. Kruger, J. Janssen, D. Pohl (UBonn), A. Macchiolo (MPI M), L. Gonella (Birmingham)

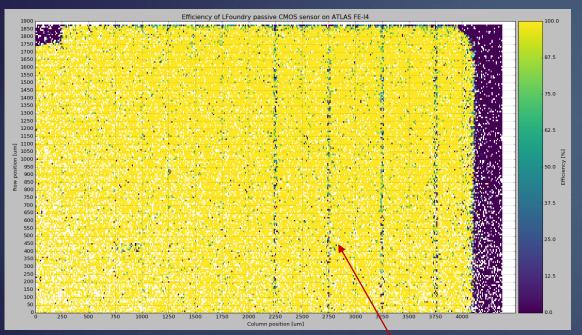

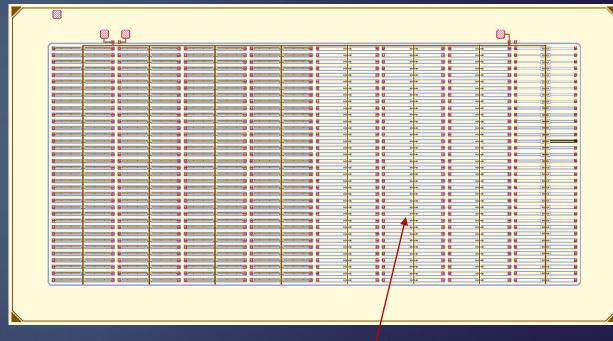

- LFoundry 150 nm CMOS technology

- 2 kΩ cm p-type bulk

- ATLAS FE-I4 pixel pitch (50x250 µm<sup>2</sup>)

18

- 300 µm thick Backside

- processed

Different n-well widths: Different fill factors

UNIVERSITY O

OXFORD

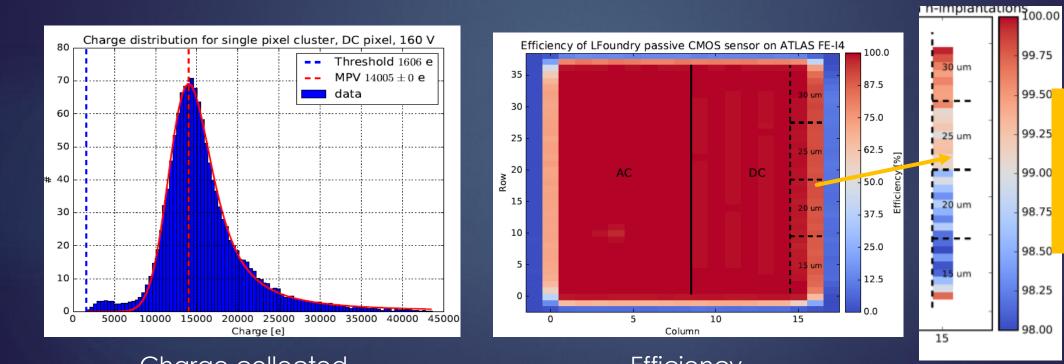

### Test Beam at ELSA (Bonn)

- ▶ 3 GeV electrons, -160V bias

- Only 2 FE-I4 planes telescope  $\longrightarrow$  No in-pixel resolution.

**Smaller fill** factor = smaller efficiency?

UNIVERSITY OF

OXFORD

19

Charge collected Depletion depth about 200 µm

Efficiency DC area seems to have less effective columns

D. Pohl, J. Janssen (Bonn)

99.75

99.50

99.25

99.00

98.75

98.50

98.25

98.00

um

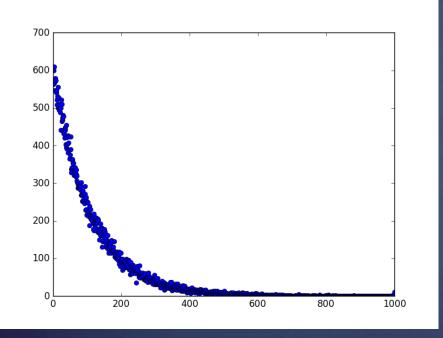

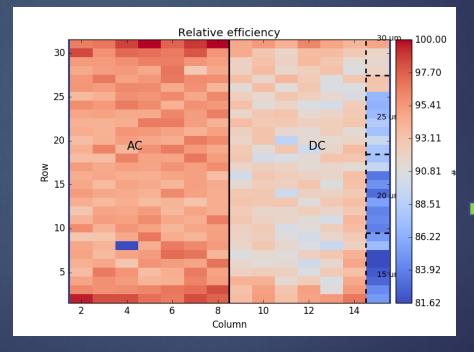

Source scan

## Americium

### Full-coverage source

# Efficiency behavior confirmed

20

Single pixel time difference distribution for source decay. From exponential: rate. Differences in pixel rate due to difference in efficiency: Relative efficiency map

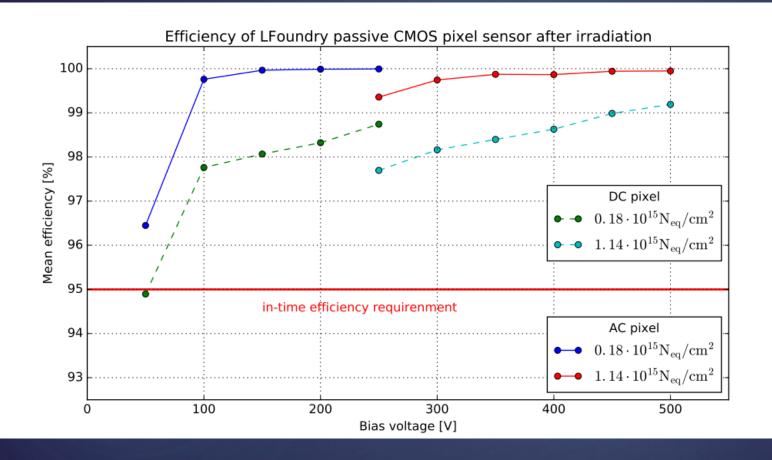

### Test beam after Irradiation

Good radiation hardness!

21

Efficiency

22

### Test Beam at SPS (CERN)

### Mimosa telescope

### D. Pohl, J. Janssen (Bonn)

Fine resolution

Design

Efficiency map

Good match!

Efficiency drop in DC part related to contacts in voltage distribution.

### Laser scan

Average TOT (charge collected)

Average cluster size

50x250 µm<sup>2</sup> reticule, slightly tilted

# CMOS Pixels: active to monolithic

2 versions:

# ► CCPD\_LF

- Amplifier and discriminator inside the sensor

- Analogue signal

- T. Hemperek, F. Hugging, H. Kruger, T. Hirono, N. Wermes (Bonn)

### Electronics inside the collection well

- Large fill factor for high Charge Collection Efficiency and rad-hardness

- Larger capacitance (larger noise)

- Full CMOS, isolation via deep p-well (PSUB)

# Next goal: fully monolithic sensor

- Two possible read-outs:

- Custom board (analogue only)

- Capacitive glued to FE-I4

- o LFoundry 150 nm

### Electronics outside the collection well

- Small fill factor, no competing wells

- Lower capacitance (lower noise)

LF monopix

Full CMOS, isolation via deep n- and p-well

# Conclusions

- Good prospects for CMOS technology in High Energy Particle Physics

- Great interest from many institutions

- ATLAS has many projects under development

- Both Pixels and Strips

- All types of CMOS (passive, active and monolithic)

- Many issues must be fully addressed yet

- Radiation hardness

- Effective cost

- ► In-time efficiency

- Eventual displacement inside the tracker

NEXT

Fully monolithic devicesFull functional modules

# Backup: HVStripV1 irradiated Sr<sup>90</sup> spectrum

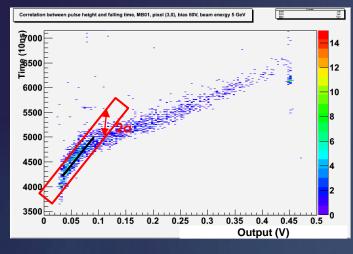

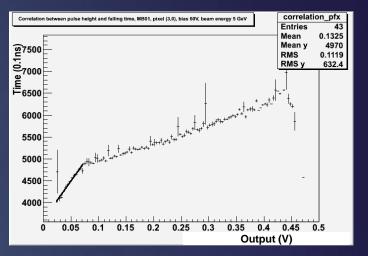

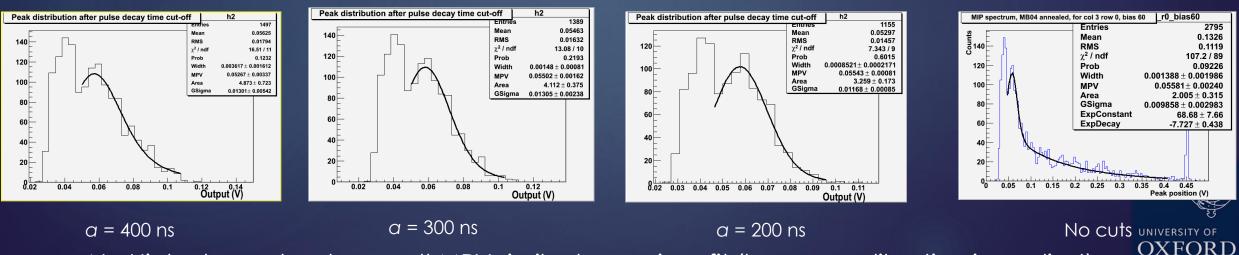

Signal-peaking time correlation: the higher the signal, the longer it takes to reach the peak. Two different slopes are observed, one for low and one for high charge region.

Cut close to the slope for the signal region

26

X profile

No High charge background! MPV similar to previous fit (here no calibration is applied).

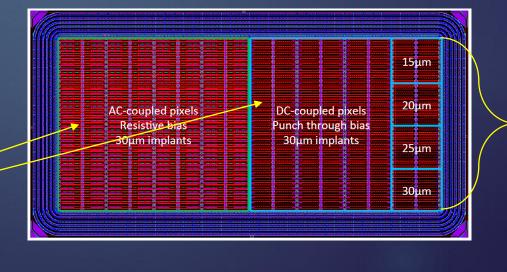

# Backup: passive CMOS pixels

**Pixel Layout Variants** universität**bonn** Implant Gap width width 20µm 30µm n-implant 25µm 25µm (30µm width) 30µm 20µm 15µm 35µm n-implant (25µm width) Bias dot (punch-though) layout not changed n-implant Implant length not changed (20µm width) Implant width variation covers ~200 $\mu$ m of the implant n-implant length (15µm width) Bias dot "p-stop"

# UNIVERSITY OF OXFORD

# Backup: passive CMOS pixels

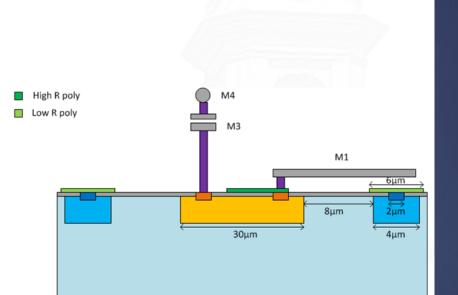

## AC coupling

- MIM cap between M3 and M4 used for the AC coupling

- implemented a up to 10pF capacitor into each pixel

- high resistive poly-silicon layer used for bias resistor

- 15 M $\Omega$  resistor in each pixel

- contributes to the input capacitance  $\rightarrow$  relevant for noise

- low resistive poly-silicon layer used for field plate on top of pstop

- improvement of breakdown behavior

- p-stop consists a contact to apply an external voltage

# Backup: passive CMOS pixels

More details:

- ► For the outer ITk pixel layers:

- AC coupled passive CMOS sensors on 8" CZ wafers

- No fine pitch bump bonding necessary

- Simplified module production, Flip-chip can be done in-house

- Cost reduction to 1 / 3

- Stripped down FE-65 from inner layer:

- ► No leakage current compensation circutry necessary

- $\blacktriangleright$  Larger pixel pitch and less pixels  $\rightarrow$  Lower power

- Wafers can be ordered already equipped with C4 bumps

- For the module concept:

- Module without larger gap pixel