# A new generation of MAPS for the ALICE Inner Tracking System

# J.W. van Hoorne - CERN

WG11 – Detector Design Meeting

CERN, December 19<sup>th</sup>, 2016

# Outline

# 1. Introduction

- Present ALICE detector and upgrade plans

- Upgrade of the ALICE Inner Tracking System (ITS)

## 2. ALPIDE

- Concept

- Key results

## 3. Future developments

- Process modifications for enhanced depletion

- Silicon-only vertex detector?

## 4. Summary

# Outline

# 1. Introduction

- Present ALICE detector and upgrade plans

- Upgrade of the ALICE Inner Tracking System (ITS)

- 2. ALPIDE

- Concept

- Key results

- 3. Future developments

- Process modifications for enhanced depletion

- Silicon-only vertex detector?

- 4. Summary

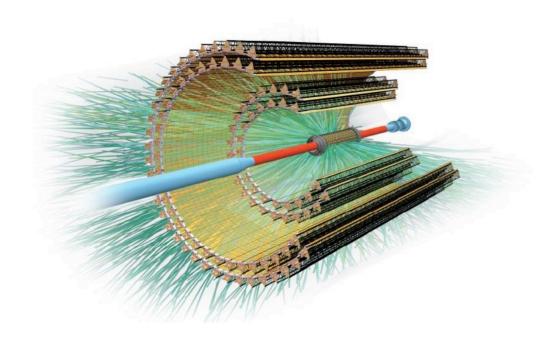

# ALICE experiment and upgrade plans

## 1. Introduction

- ALICE prepares major upgrade of experimental setup in LS2 of LHC in 2019/2020

- Targets:

- Large sample of recorded events: 10 nb<sup>-1</sup> Pb-Pb plus pp and p-Pb data -> gain factor 100 in statistics over originally approved program

- Significant improvement of tracking and vertexing capabilities at low p<sub>T</sub>

- → also present ITS needs to be upgraded!

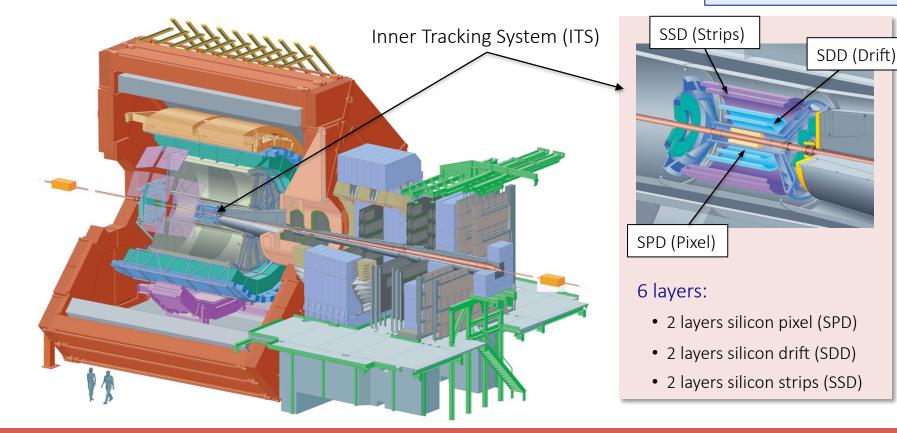

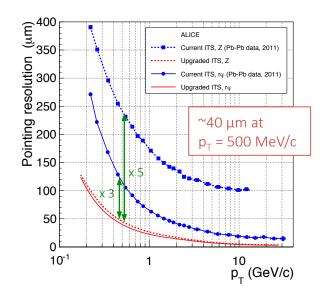

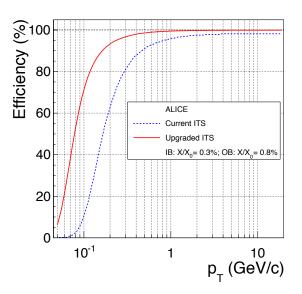

# ITS upgrade: design objectives

## 1. Introduction

Improve pointing resolution by a factor ~3 in r- $\varphi$  and ~5 in z at p\_T=500MeV/c (~40  $\mu m$  at p\_T = 500 MeV/c )

- reduce beam pipe radius: 29mm → 19mm

- get closer to IP: 39mm → 22mm (innermost layer)

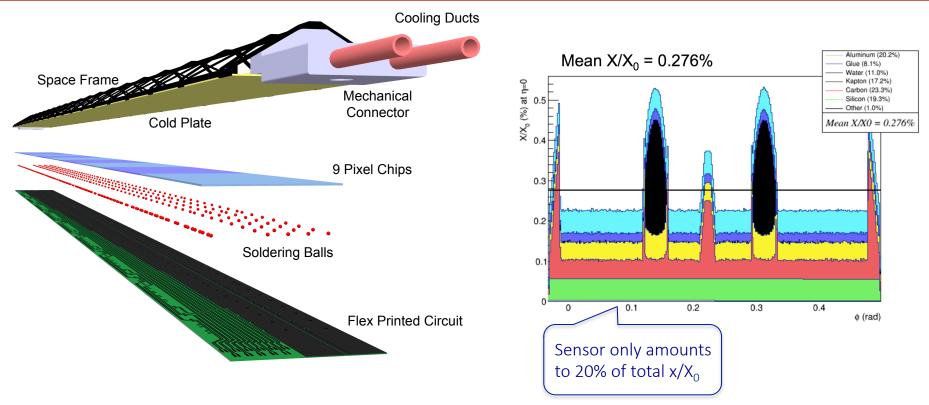

- reduce material budget: ~1.14%  $x/X_0 \rightarrow$  ~0.3%  $x/X_0$  (inner layers)

- $\rightarrow$  less material  $\rightarrow$  reduce power consumption

- reduce pixel size:  $50x425\mu m^2 \rightarrow O(30x30\mu m^2)$

### Improve tracking efficiency and $p_T$ -resolution at low $p_T$

• increase granularity: 6 layers  $\rightarrow$  7 layers, only pixel sensors

## Fast readout

readout of Pb-Pb at up to 100 kHz (presently 1kHz) and 400kHz for pp

## Fast insertion/removal of detector modules

• possibility to replace non-functioning detector modules during yearly shutdown

### → Decision to fully replace present ITS

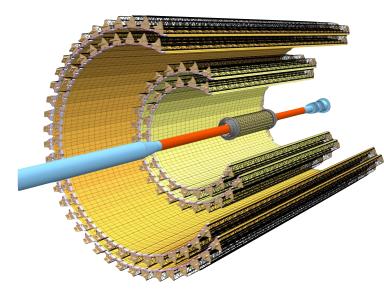

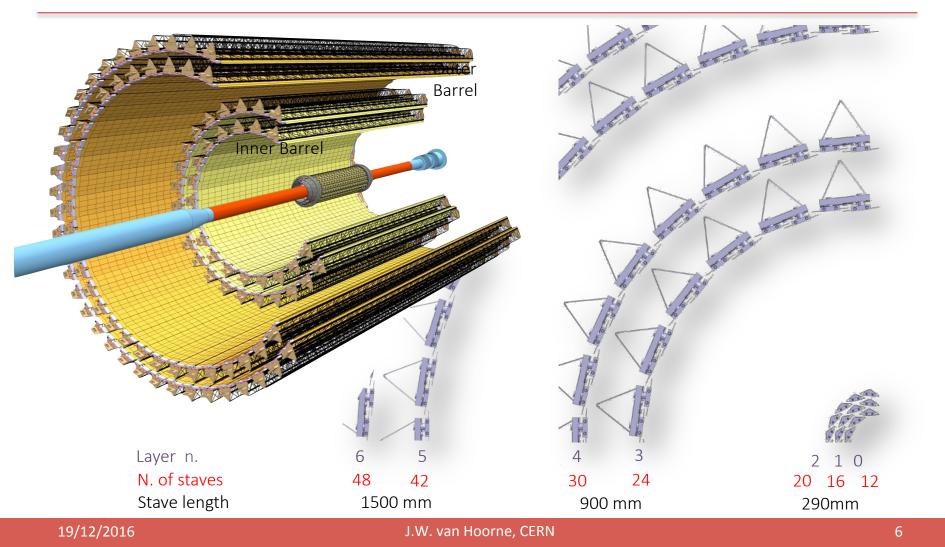

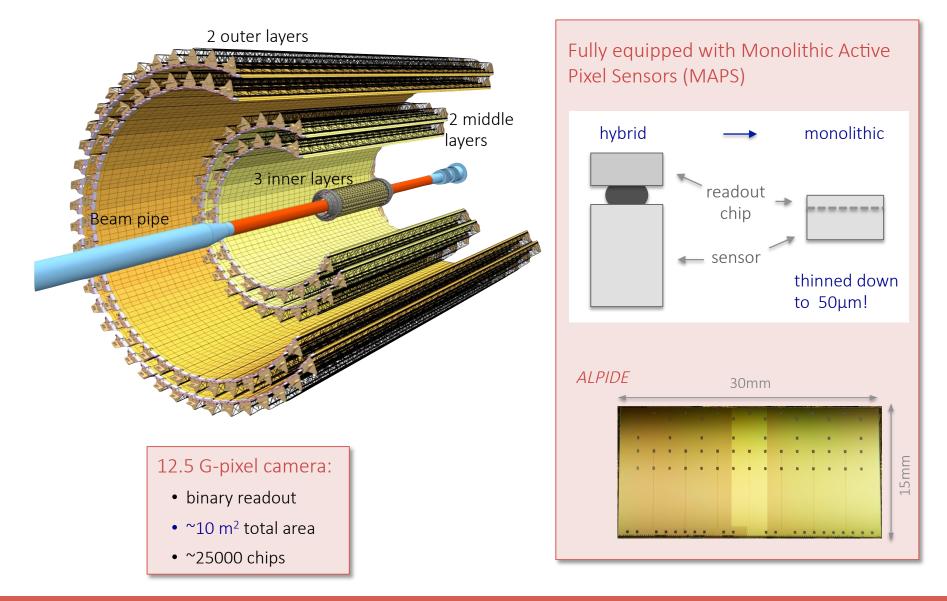

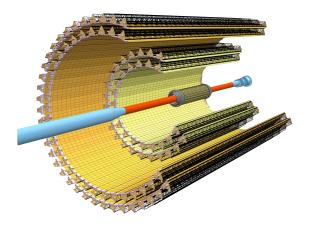

# Layout of new ALICE Inner Tracking System

## 1. Introduction

## 7-layer geometry:

- r-coverage: 23 mm 400 mm

- $\eta$ -coverage:  $|\eta| \le 1.22$  for tracks from 90% luminous region

- 3 Inner Barrel layers: 0.3% x/X<sub>0</sub> per layer

- 4 Outer Barrel layers: 1% x/X<sub>0</sub> per layer

# Layout of new ALICE Inner Tracking System

1. Introduction

#### 19/12/2016

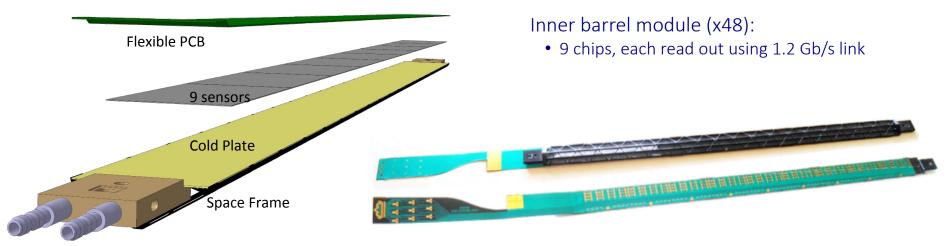

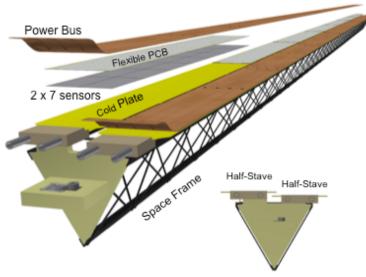

# Stave layout 1. Introduction

### Inner Barrel stave

## **Outer Barrel**

## Outer barrel module (x1800)

• 2×7 chips (1 master, 6 slaves), locally interconnected, read out using 2×400 Mb/s links

#### 19/12/2016

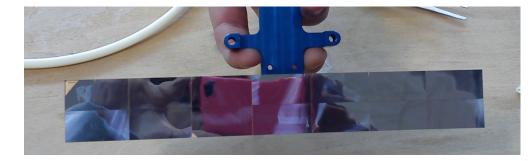

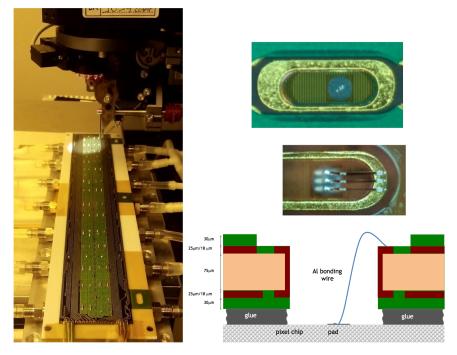

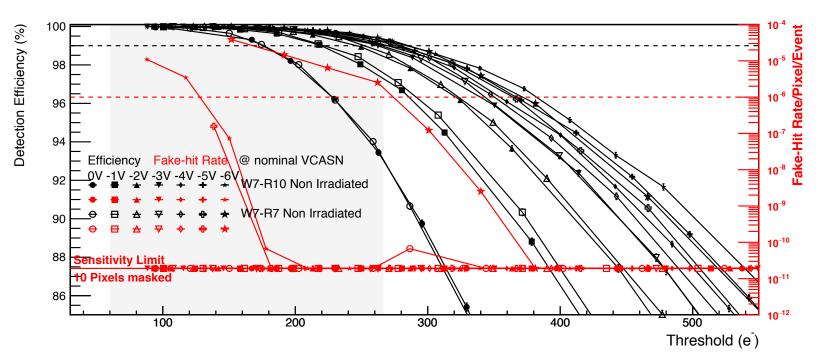

# Module assembly

## 1. Introduction

Module (HIC – hybrid integrated circuit): chips glued and wire-bonded to flexible PCB

Chip placement + gluing to flexible PCB

Wire bonding

- Placement is handled by automated custom-made machine (distributed to 6 assembly sites worldwide)

- Flexible PCB is glued to chips

• Chips are wire bonded through vias in the FPCB distributed over full chip surface

## Detector

# 5m cable

# Readout units

|  | 3 |

|--|---|

|  |   |

- Readout logic fully integrated into ALPIDE

- ALPIDE can directly drive 5m cables using integrated high-speed transmitters (up to 1.2 Gb/s)

- No further electronics on detector

- 1.2 Gb/s (data IB)

- 400 Mb/s (data OB)

- 80 Mb/s (ctrl IB/OB)

- Clock

- Power

- Total: 192 Readout Units

- Distribute trigger and control signals

- Interface data links to ALICE DAQ

- Control power supplies of chips

# Outline

- 1. Introduction

- Present ALICE detector and upgrade plans

- Upgrade of the ALICE Inner Tracking System (ITS)

## 2. ALPIDE

- Concept

- Key results

- 3. Future developments

- Process modifications for enhanced depletion

- Silicon-only vertex detector?

- 4. Summary

|      |      | • |   | •  |   |   |   |   |      |  |

|------|------|---|---|----|---|---|---|---|------|--|

| =    |      | • | - | •  | - | • | - | 1 |      |  |

|      |      |   | + | х. |   |   |   |   |      |  |

|      |      |   |   |    |   |   |   |   |      |  |

|      |      |   |   |    |   |   |   |   |      |  |

|      |      |   |   |    |   |   |   |   |      |  |

|      |      |   |   |    |   |   |   |   |      |  |

| <br> | <br> |   |   |    |   |   |   |   | <br> |  |

30mm

#### 19/12/2016

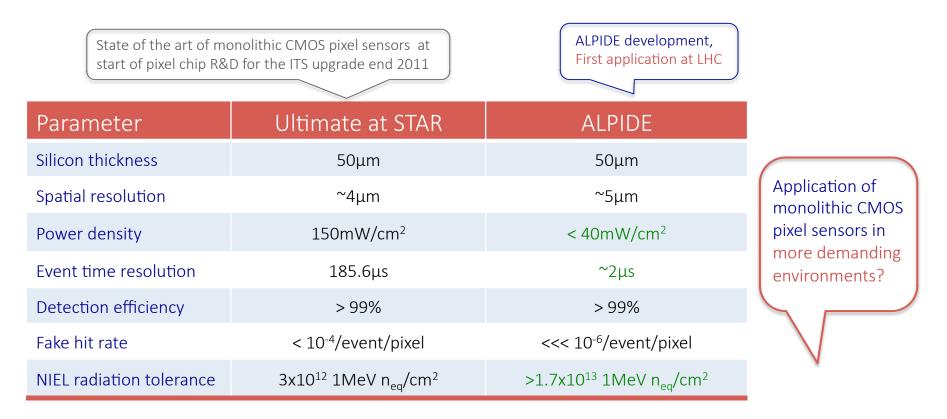

State of the art of monolithic CMOS pixel sensors at start of pixel chip R&D for the ITS upgrade end 2011

| Parameter             | Inner Barrel                                                   | Outer Barrel                                           | Ultimate at STAR                                         |  |  |

|-----------------------|----------------------------------------------------------------|--------------------------------------------------------|----------------------------------------------------------|--|--|

| Silicon thickness     | 50μ                                                            | 50µm                                                   |                                                          |  |  |

| Spatial resolution    | 5µm                                                            | 10µm                                                   | ~4µm                                                     |  |  |

| Chip dimension        | 15mm x                                                         | 22.71mm x 20.24mm                                      |                                                          |  |  |

| Power density         | < 300mW/cm <sup>2</sup>                                        | < 100mW/cm <sup>2</sup>                                | 150mW/cm <sup>2</sup>                                    |  |  |

| Event time resolution | < 30                                                           | 185.6µs                                                |                                                          |  |  |

| Detection efficiency  | > 99                                                           | > 99%                                                  |                                                          |  |  |

| Fake hit rate         | < 10 <sup>-5</sup> /eve                                        | < 10 <sup>-4</sup> /event/pixel                        |                                                          |  |  |

| NIEL tolerance        | $1.7 \mathrm{x} 10^{12} \mathrm{ 1 MeV} \mathrm{ n_{eq}/cm^2}$ | 10 <sup>11</sup> 1MeV n <sub>eq</sub> /cm <sup>2</sup> | 3x10 <sup>12</sup> 1MeV n <sub>eq</sub> /cm <sup>2</sup> |  |  |

| TID tolerance         | 270krad                                                        | 10krad                                                 | 150krad                                                  |  |  |

- First large MAPS-based vertex detector: STAR PXL detector at RHIC with Ultimate chip

- Ultimate chip does not fulfill requirement of ITS upgrade -> new development required -> ALPIDE

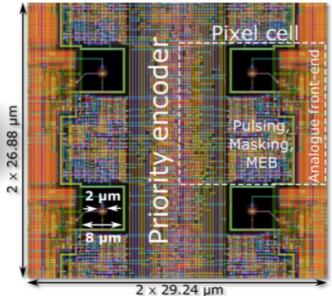

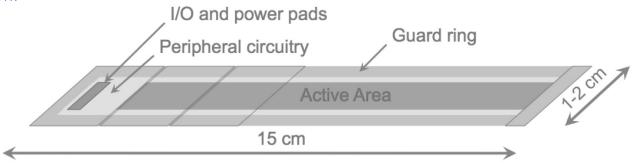

# ALPIDE: floor plan 2. ALPIDE

# 1024 pixels / 3cm interface pads used for wire over matrix bonding 512 pixels / 1.38 cm 290µm pixel matrix 0.12cm analogue biasing and digital interface circuitry

# Key features:

- Dimension: 30mm x 15mm (1024 x 512 pixels)

- Pixel pitch: 29µm x 27µm

- Ultra low power:~40mW/cm<sup>2</sup> (average over entire chip)

- Global shutter: triggered acquisition (up to 200 kHz Pb-Pb, 1MHz pp) or continuous (progr. integration time: 1µs - ∞)

## Key concepts:

- In-pixel amplification

- In-pixel hit discrimination

- In-pixel 3-level event memory

- In-matrix zero-suppression

### 19/12/2016

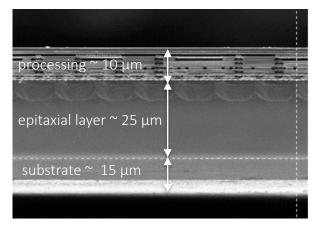

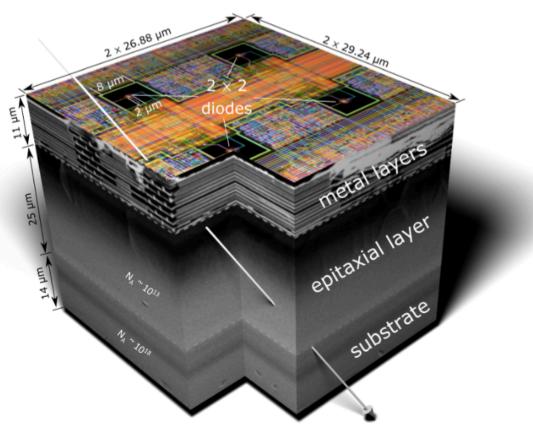

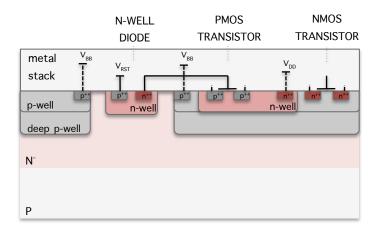

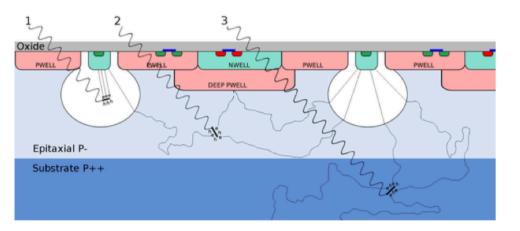

# ALPIDE: process technology 2. ALPIDE

TowerJazz 180nm CMOS imaging sensor process:

- High-resistivity (>1kΩcm) p-type epitaxial layer (18µm-40µm) on p-type substrate (~10Ωcm)

- Deep p-well for full CMOS circuitry within the matrix

- Feature size 180nm and 6 metal layers  $\rightarrow$  dense circuitry

Sensor only partially depleted  $\rightarrow$  application of moderate reverse bias V<sub>BB</sub> (<6V) possible via the substrate

SEM picture of prototype chip cross-section

Signal from collection diode:  $\Delta V \simeq Q/C$

- Increase Q:

- increase epitaxial layer thickness

- limit charge sharing and losses

- > Decrease C:

- optimizing collection diode

- increase reverse bias

## Charge collection time: ~1-50ns

depending on size of depletion zone

#### 19/12/2016

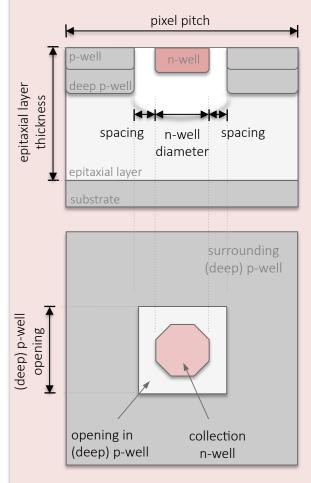

# Q/C ratio and sensor design parameters 2. ALPIDE

## Sensor performance mainly determined by:

- Pixel pitch

- Collection n-well size

- Spacing between the collection n-well and surrounding( deep) p-well

- Epitaxial layer thickness and resistivity

- Reverse bias voltage V<sub>BB</sub> on the collection diode

- Sensor optimization studies mainly by small-scale prototypes with analog readout

- During design of ALPIDE, particular focus put on low pixel-input capacitance C

- → values as low as 2fF achieved (signal of 80mV for 1000e<sup>-</sup>)

## Parameters selected for ALPIDE (29µm x 27µm pixel size):

- 25µm epitaxial layer

- 2μm n-well diameter, 3μm spacing

- > 88% of pixel surface can be used for circuitry

# Pixel and collection electrode geometry (not to scale):

#### 19/12/2016

# 3D and 2D view of 2x2 pixels 2. ALPIDE

full CMOS circuitry within pixel matrix

### ALPIDE in-pixel circuitry

- Front-end: continuously active, power consumption 40nW (9 transistors, full custom)

- Multi-event memory: 3 stages (62 transistors, full-custom)

- Configuration: masking and pulsing registers (31 transistors, full-custom)

- Testing: analog and digital test pulse circuitry (17 transistors, full-custom)

- Matrix read-out: priority encoder, asynchronous, hit-driven

#### 19/12/2016

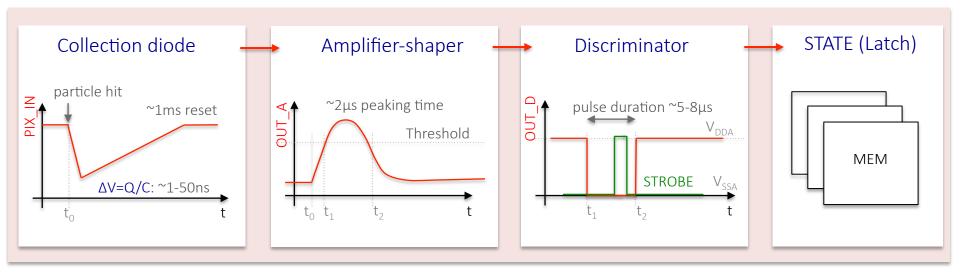

# ALPIDE: front-end circuit

2. ALPIDE

## Front-end acts as delay line

Ultra low-power front-end circuit 40nW/pixel

- Sensor and front-end continuously active

- Upon particle hit front-end forms a pulse with peaking time of 2-4μs (<-> time walk)

- charge collection time < 50ns! -> long pulse duration a choice made for ALICE ITS: functioning as delay line and reduce power consumption (40nW/pixel) <-> material budget

- Threshold is applied to form a binary pulse

- globally set by front-end bias DACs

- Hit is latched into memory if STROBE is applied during binary pulse

- Global shutter: triggered (up to 200 kHz Pb-Pb, 1MHz pp) or continuous (progr. integration time:  $1\mu s \infty$ )

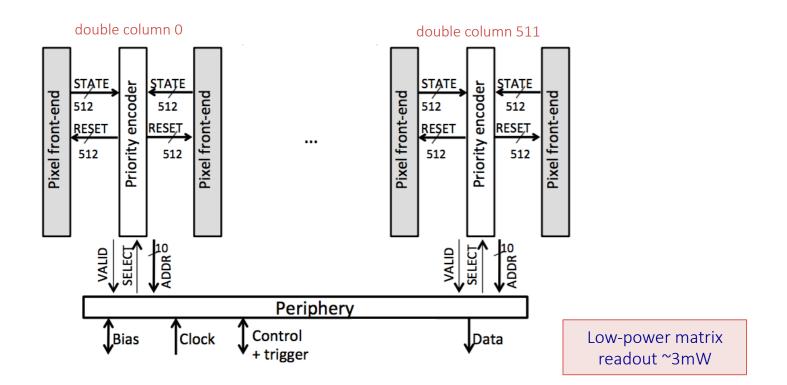

# ALPIDE: readout architecture 2. ALPIDE

Matrix readout by hit-driven asynchronous circuit (priority encoder) in double-columns:

- sequentially provides addresses only of hit pixels  $\rightarrow$  in-matrix zero suppression, fast

- no activity if not hit (no free running clock) → low-power matrix readout (~2mW)

# Outline

- 1. Introduction

- Present ALICE detector and upgrade plans

- Upgrade of the ALICE Inner Tracking System (ITS)

# 2. ALPIDE

- Concept

- Key results

- 3. Future developments

- Process modifications for enhanced depletion

- Silicon-only vertex detector?

- 4. Summary

30mm

#### 19/12/2016

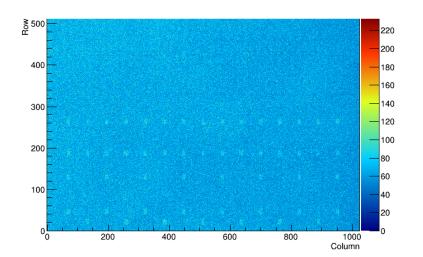

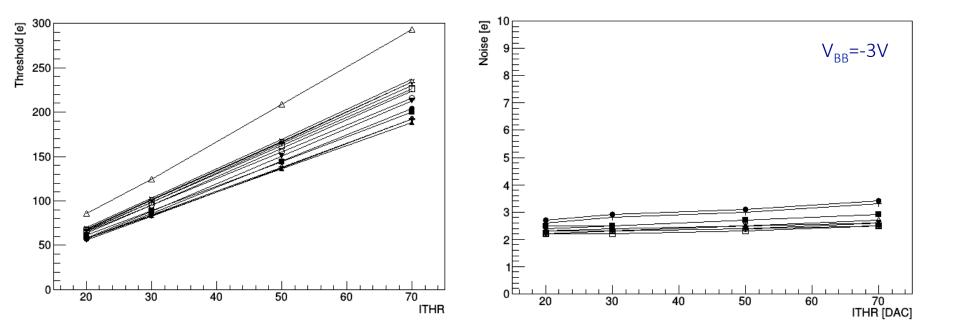

# ALPIDE: Threshold and noise

## 2. ALPIDE

- Threshold globally adjustable via on-chip DACs

- Good threshold uniformity

- Threshold RMS 10-15% of average threshold

- Very low noise values

- 5-6e<sup>-</sup> without reverse substrate bias, 2-3e<sup>-</sup> with

- Large threshold-to-noise ratio

- Fake-hits due to Gaussian noise extremely rare

- Large operational margin

- MIPs release in order of 1400e- (MPV) in sensitive layer (Landau fluctuations, charge sharing also to be considered..)

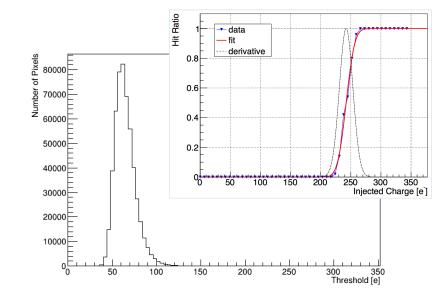

# ALPIDE: Test beam 2. ALPIDE

- - Test beam performed using ALPIDE telescopes, central chip is treated as device under test (DUT)

- Calculated resolution at DUT around 2-3 μm

- Studied performance in terms of: detection efficiency, position resolution, cluster sizes and shapes

- plus corresponding lab measurements of fake-hit rate, threshold (s-curve scan)

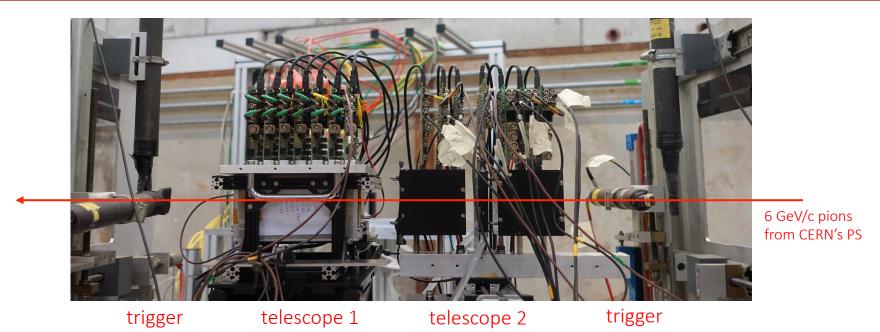

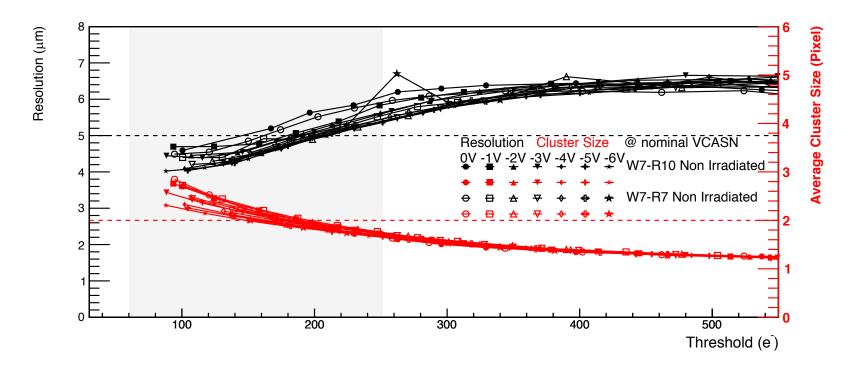

# Reverse substrate bias dependence 2. ALPIDE

## Detection efficiency and fake-hit rate

- Detection efficiency stays at 100% ε over wide range of thresholds

- Chip-to-chip fluctuations negligible

- Clear ordering: increasing performance with larger reverse substrate bias

- Most significant improvement from 0V to -1V

- Extremely low fake-hit rate

- Below measurement limit of 10<sup>-11</sup>/pixel/event after masking 10 pixels (1/50 000), only increased for -6V

# Reverse substrate bias dependence 2. ALPIDE

## Position resolution and cluster size

- Average cluster sizes vary between 1 and 3 pixels (for MIPs)

- Position resolution around desired 5µm in threshold range with detection efficiency > 99%

- Biggest improvement from 0V to -1V

- Little dependence on reverse substrate bias from -2V to -6V

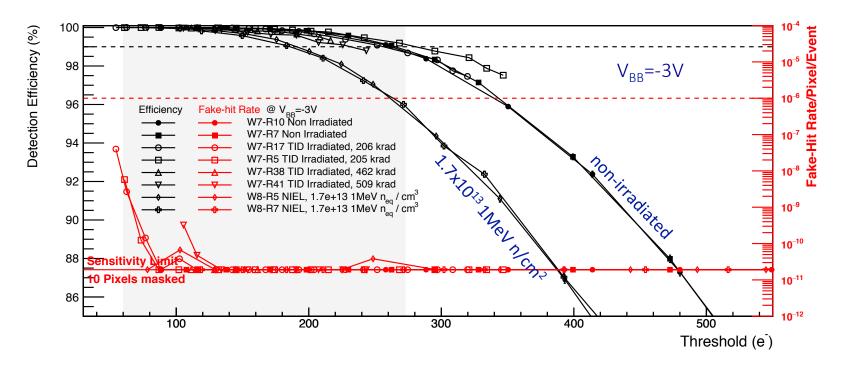

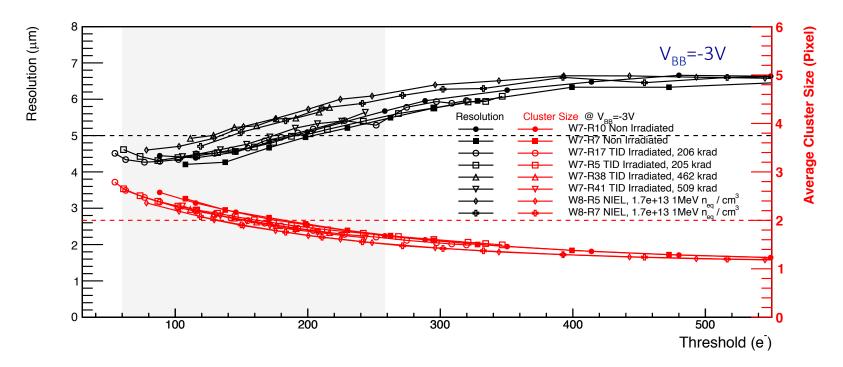

# NIEL irradiation 2. ALPIDE

## Detection efficiency and fake-hit rate

Sufficient operational margin after 1.7x10<sup>13</sup> 1MeV n/cm<sup>2</sup> (10 times life time dose of upgraded ITS)

# NIEL irradiation 2. ALPIDE

## Position resolution and cluster size

- Cluster sizes and position resolution slightly reduced after 1.7x10<sup>13</sup> 1MeV n/cm<sup>2</sup> (10 times life time dose of upgraded ITS)

- Resolution remains around desired 5µm in threshold range with detection efficiency > 99%

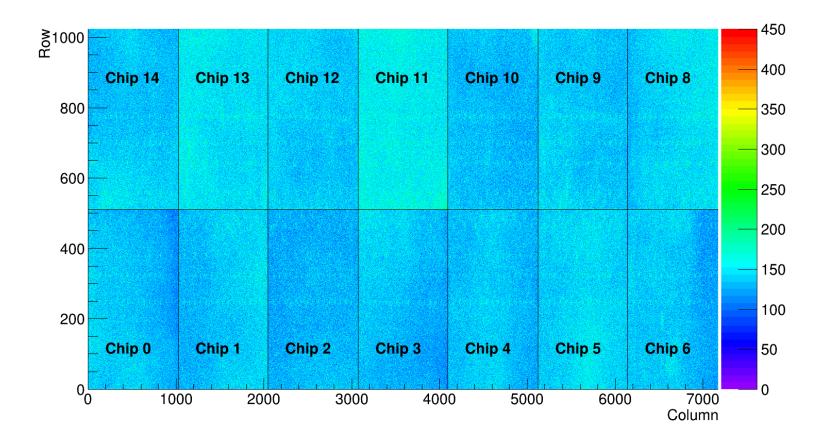

# ALPIDE in module assemblies 2. ALPIDE

Example: threshold scan at nominal setting on OB module (HIC – hybrid integrated circuit)

14 ALPIDE chips connected to flexible PCB

19/12/2016

.

# ALPIDE in module assemblies

# 2. ALPIDE

## Example: threshold vs ITHR DAC setting for all 14 chips on OB module

## Behavior comparable to single chips

- Threshold RMS 10% 15% of average threshold

- Noise 2-3e<sup>-</sup>

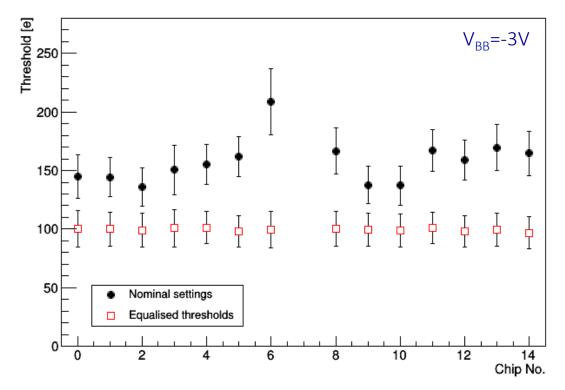

# ALPIDE in module assemblies 2. ALPIDE

## Threshold equalization

- Tuned thresholds

- Use ITHR DAC to equalize thresholds between chips

- Here: OB module at nominal settings and tuned to 100 e<sup>-</sup>

ITHR settings determined from linear fit to threshold-vs-ITHR curves

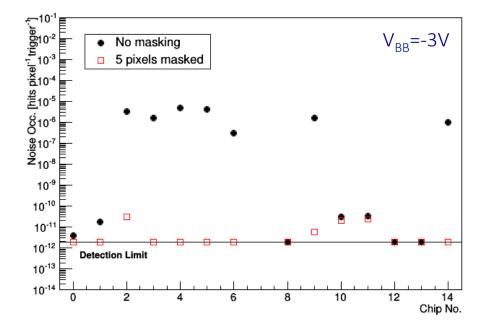

# ALPIDE in module assemblies 2. ALPIDE

## Fake-hit rate from data taking with random triggers (OB module)

- Fake-hit rate in OB HIC for all 14 chips without masking and with masking 5 pixels per chip (1 / 100000)

- -3V reverse substrate bias, low threshold (ITHR = 20, threshold  $50 70 e^{-1}$ )

### Behavior comparable to single chips

• Fake-hit rate <  $10^{-10}$  with 5 masked pixels (1/100 000)

# Outline

- 1. Introduction

- Present ALICE detector and upgrade plans

- Upgrade of the ALICE Inner Tracking System (ITS)

- 2. ALPIDE

- Concept

- Key results

- 3. Future developments

- Process modifications for enhanced depletion

- Silicon-only vertex detector?

- 4. Summary

# Development monolithic CMOS pixel sensors

### 3. Future developments

- ALPIDE fulfills or surpasses pixel-chip requirements of the ALICE ITS upgrade

- ALPIDE development represents significant advancement regarding power density, fake-hit rate, readout speed, and radiation hardness

- Application of monolithic CMOS pixel sensors in more demanding environments requires increased radiation tolerance and better timing resolution required

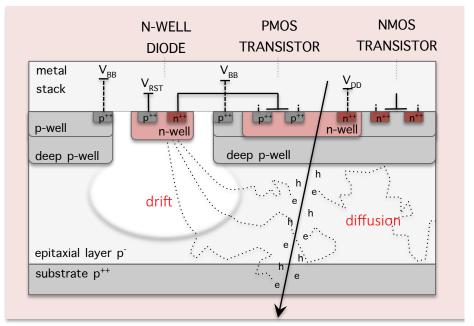

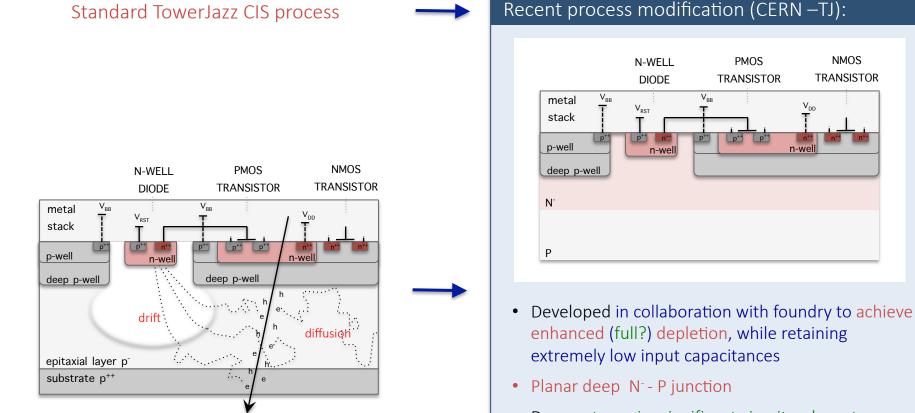

# Process modification for enhanced depletion

### 3. Future developments

- Does not require significant circuit or layout changes  $\rightarrow$  same design can be fabricated in both std and mod process

- Prototypes processed using pALPIDE-2 mask set ٠

- Note: not used for ALICE ITS upgrade

NMOS

TRANSISTOR

n-wel

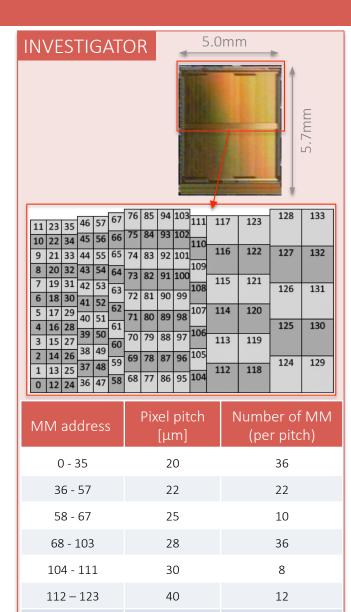

# Test chip: INVESTIGATOR

## 3. Future developments

- INVESTIGATOR: dedicated test chip developed within ALPIDE R&D phase, designed for systematic studies on influence of design parameters on sensor characteristics

- Consists of 134 matrices of 8x8 pixels ("mini-matrices", MM)

- Various pixel sizes (20x20µm<sup>2</sup> to 50x50µm<sup>2</sup>) and collection electrode designs (n-well size, spacing)

- Each of the mini-matrices can be selected and connected to a set of 64 output buffers (~10ns rise time)

- All 64 pixels of a mini-matrix can be read out in parallel, allowing for continuous parallel signal sampling

- Possibility of measuring evolution of a cluster, i.e. charge collection time in each pixel

- Dedicated 64-channel readout system developed, sampling at 65MHz

- ✓ Chips produced on different wafers with epi-layer thickness between 18µm and 30µm, and in different process variants (std, mod)

- ✓ Samples tested up to  $10^{15}$  1MeV n<sub>eq</sub>/cm<sup>2</sup> and 1Mrad

50

123 - 134

10

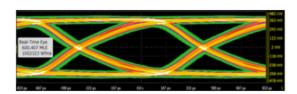

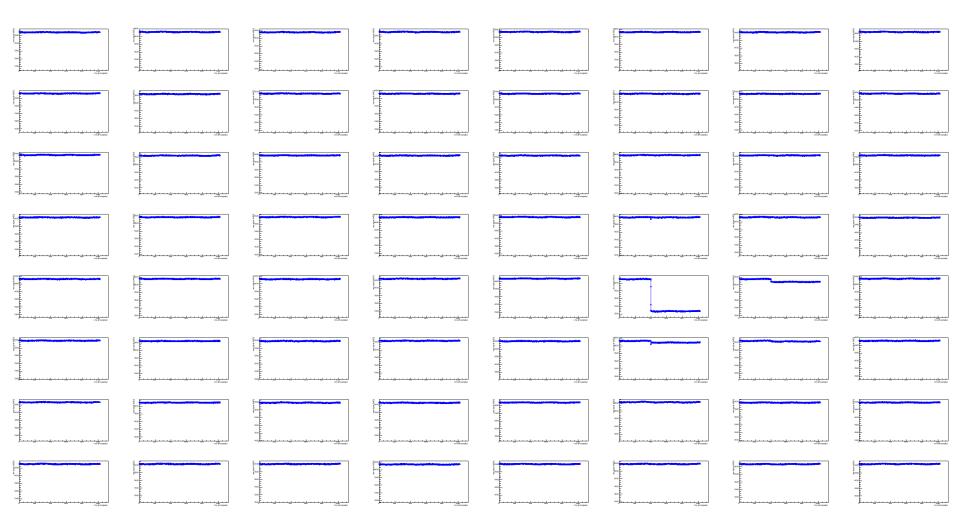

# INVESTIGATOR – waveform-event display for all 64 pixels

3. Future developments

# INVESTIGATOR – waveform-event display for all 64 pixels

3. Future developments

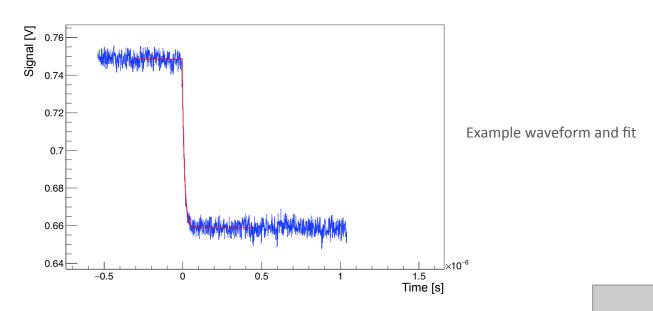

# Charge-collection time

3. Future developments

• Precise charge-collection time measurements performed using differential probe and fast scope on single pixel

$t > t_0$

• Fit of waveforms with function:  $t \le t_0$

$f = a + m \cdot (t - t_0)$  $f = a + m \cdot (t - t_0) - b \cdot (e^{-\frac{t - t_0}{\tau}} - 1)$

- ALPIDE-like pixel studied: 28μm pitch, 2um n-well diameter, 3μm spacing, 25μm epi

- Measurements performed with <sup>55</sup>Fe

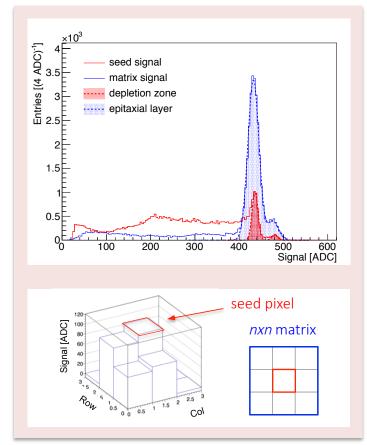

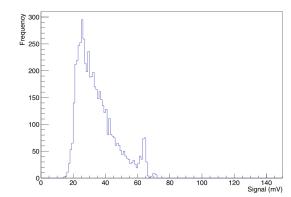

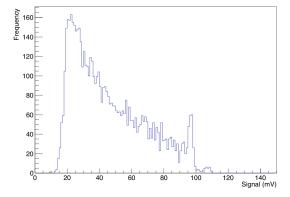

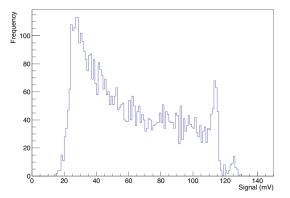

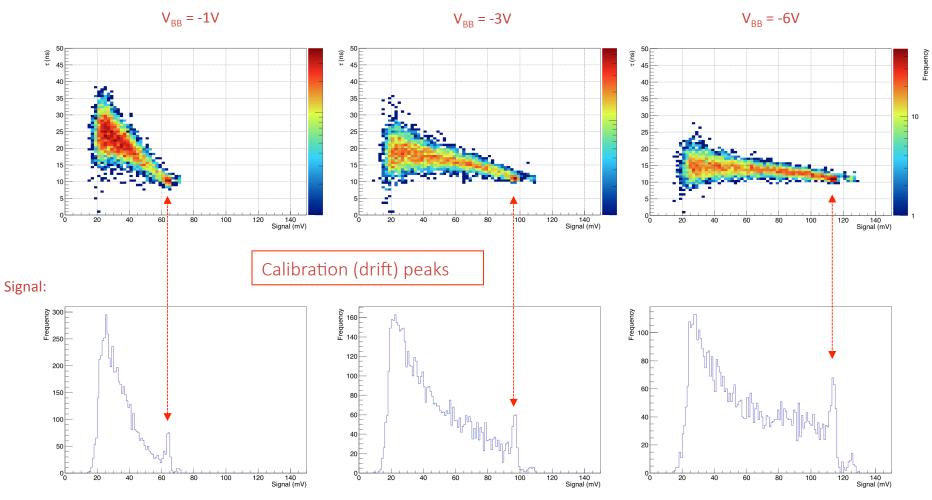

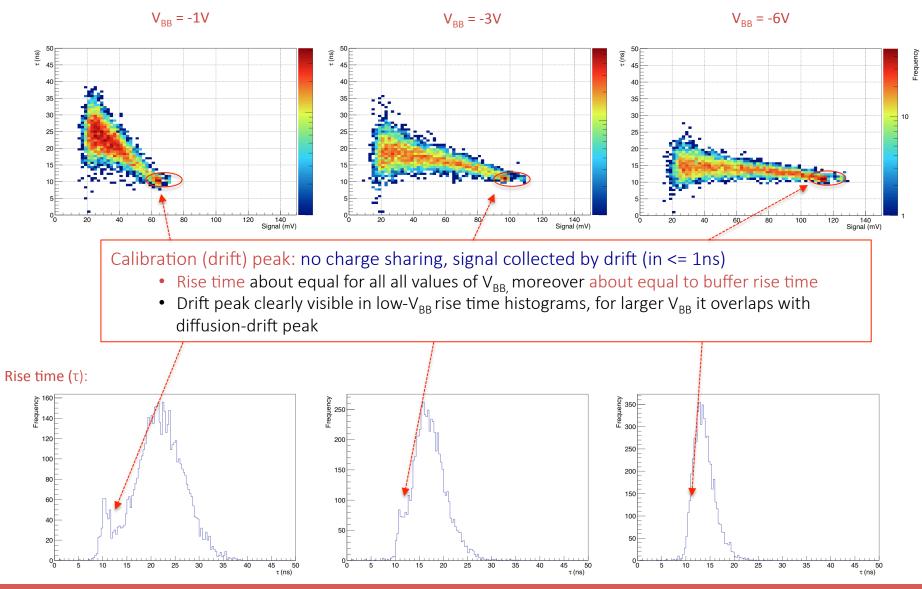

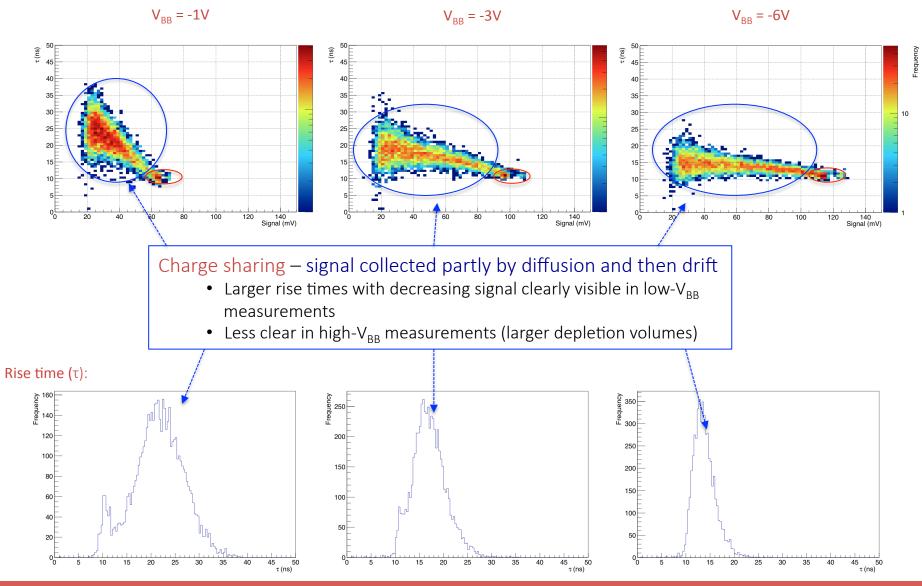

# Charge-collection time measurements with X-Rays

### 3. Future developments

<sup>55</sup>Fe: two X-Ray emission modes:

- 1. K- $\alpha$ : 5.9keV (1640e/h in Si), relative frequency: 89.5% attenuation length in Si: 29 $\mu$ m

- 2. K- $\beta$ : 6.5keV (1800e/h in Si), relative frequency: 10.5% attenuation length in Si: 37 $\mu$ m

For X-Ray absorption in sensor fabricated with the std process three cases can be defined:

- 1. Absorption in depletion volume: charge collected by drift, no charge sharing, single pixel clusters

- Events of this case populate the calibration (K- $\alpha$ ) peak in signal histogram

- Charge collection time expected to be ≈ 1ns

- 2. Absorption in epitaxial layer: charge partially collected by diffusion and then drift, charge sharing between pixels depending on position of X-Ray absorption

- Charge collection time expected to be dependent on distance of the X-Ray absorption from a depletion volume, and longer than for events of case 1

- 3. Absorption in substrate:

- contribution depending on depth of X-Ray absorption position within substrate, and charge carrier lifetime within substrate

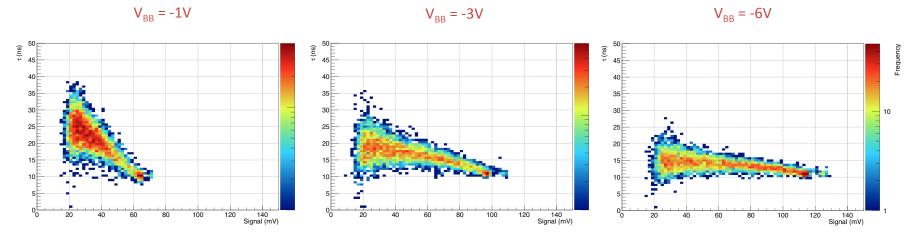

## 3. Future developments

## 3. Future developments

## MM75: 28µm pitch, 2um n-well diameter, 3µm spacing, 25µm epi

Signal:

## 3. Future developments

## 3. Future developments

### MM75: 28µm pitch, 2um n-well diameter, 3µm spacing, 25µm epi

**Rise time (**τ):

19/12/2016

J.W. van Hoorne, CERN

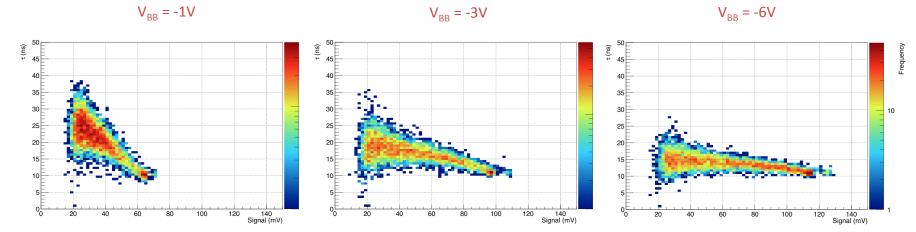

## 3. Future developments

## 3. Future developments

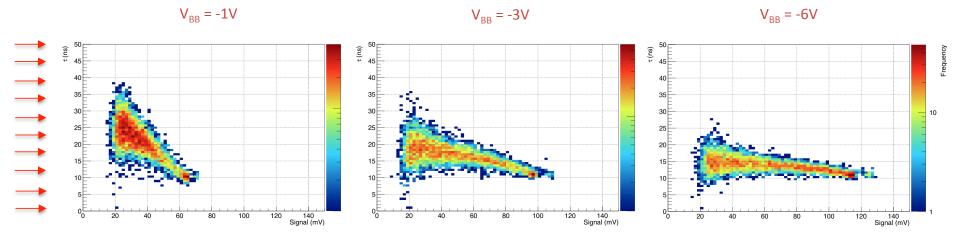

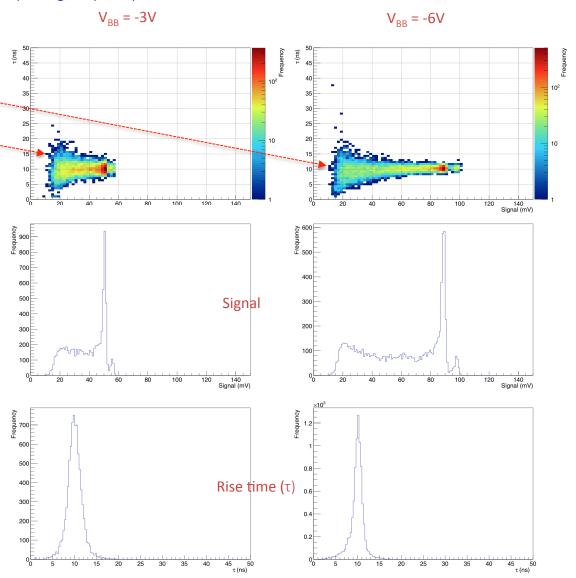

# Charge-collection time - Modified process

3. Future developments

- For modified process, otherwise same pixel (geometry) no change in rise time between events with or without charge sharing

- → charge collected purely by drift

- No change in signal rise times between -3V and -6V V<sub>BB</sub>, only in signal (capacitance C)

- Signal rise time about equal to the one for drift peak in the std process

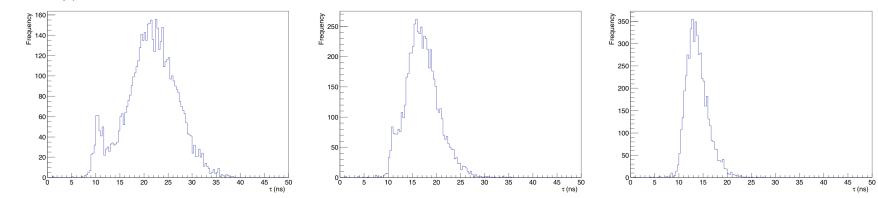

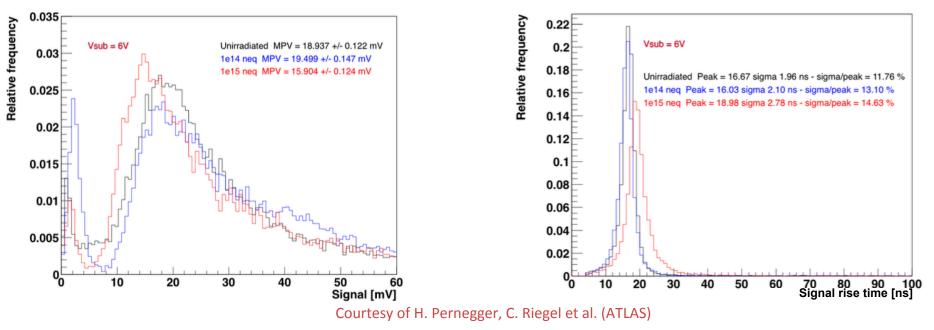

# Charge-collection and signal rise time at up to $1 \times 10^{15}$ 1MeV n<sub>eq</sub>/cm<sup>2</sup>

## 3. Future developments

<sup>90</sup>Sr measurements on modified-process samples (different setup, different pixel w.r.t. before)

- Non-irradiated

- $1x10^{14}$  1MeV n<sub>eq</sub>/cm<sup>2</sup> (NIEL) and 100krad (TID)

- $1x10^{15}$  1MeV n<sub>eq</sub>/cm<sup>2</sup> (NIEL) and 1Mrad (TID)

MM129: 50µm pitch, 3um n-well diameter, 18.5µm spacing, 25µm epi

- Little change to signal after irradiation, signal well separated from noise

- Note: standard process no longer working after 1x10<sup>15</sup> 1MeV n<sub>eq</sub>/cm<sup>2</sup>

- Recent test beam measurements show no change of efficiency after 1x10<sup>15</sup> 1MeV n<sub>ed</sub>/cm<sup>2</sup>

## Outline

- 1. Introduction

- Present ALICE detector and upgrade plans

- Upgrade of the ALICE Inner Tracking System (ITS)

- 2. ALPIDE

- Concept

- Key results

## 3. Future developments

- Process modifications for enhanced depletion

- Silicon-only vertex detector?

- 4. Summary

# What's up next? Ultra-light "silicon-only" vertex detector

### 3. Future developments

## How to further reduce material thickness?

- eliminate active cooling: for a 30cm long stave possible for power densities below 20mW/cm<sup>2</sup>

- eliminate electrical substrate (flexible FPCs): possible if power density is sufficiently low (voltage drops on supply and biasing) and the (monolithic) sensor covers the full stave length

ALPIDE Chip: pixel matrix power density ~7mW/cm<sup>2</sup>, the rest is dissipated in the periphery!

$\rightarrow$  Can the circuit periphery be put at the periphery of the detector?

#### 19/12/2016

#### J.W. van Hoorne, CERN

# Silicon-only vertex detector study for ALICE

3. Future developments

One layer built out of 4 pixel chips, with periphery at outside edge:

• chip dimensions: 140 x 56 (94) mm<sup>2</sup> -> fits on 200mm wafer!

Layer 0, 1, 2  $r \approx 18$ mm (circumf. = 113mm) L0: L1:  $r \approx 24$ mm (circumf. = 151mm) L2:  $r \approx 30 \text{ mm}$  (circumf. = 188mm) ~140mm First studies for ALICE indicate further improvement of factor ~2 when replacing proposed IB with such a Beam pipe r = 16mm detector

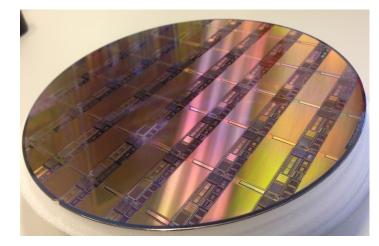

# Limits of dimensions of a CMOS chip?

## 3. Future developments

## Limit: reticle mask

- typically of the order of 2 x 2 cm<sup>2</sup>

- IC industry demands small-size reticles for fabrication yield and to facilitate system integration

- for chips larger than reticle size -> stitching

### Stitching: allows building circuits as large as the entire wafers

- Stitching is combining part of the reticle to obtain a chip with an area larger than the reticle (e.g. done for large professional CCDs)

- Example in one dimension:

- All connections to the exterior on one side

- All routing using on-chip metal layers, all functions integrated

## Outline

- 1. Introduction

- Present ALICE detector and upgrade plans

- Upgrade of the ALICE Inner Tracking System (ITS)

- 2. ALPIDE

- Concept

- Key results

- 3. Future developments

- Process modifications for enhanced depletion

- Silicon-only vertex detector?

## 4. Summary

- New ALICE ITS with 7 layers of Monolithic Active Pixel Sensor (MAPS) will be installed during LS2 of the LHC in 2019/2020

- A dedicated monolithic pixel chip the ALPIDE has been developed

- Represents significant advancement of the technology of MAPS regarding power consumption, readout speed, charge collection time and radiation hardness

- Results from ALPIDEs in module assemblies comparable to results from single chips

- ✓ Production Readiness Review (PRR) in November 2016 -> got go ahead for production

- With the modified process, a dependency of the signal rise time on the relative signal is no longer observed, while retaining the very low pixel-input capacitances already achieved

- Charge collected purely via drift

- Very low pixel-input capacitances already achieved are retained

- Good results sparked interest of several other groups (ATLAS, CLIC)

- Recent test beam measurements show no change of efficiency after 1x10<sup>15</sup> 1MeV n<sub>ed</sub>/cm<sup>2</sup>

- Next step "Silicon-only" vertex detector?

- Technology to produce large CMOS sensors already existing

- Yet to be verified: minimum bending radii for very thin CMOS wafers

# BACKUP

19/12/2016

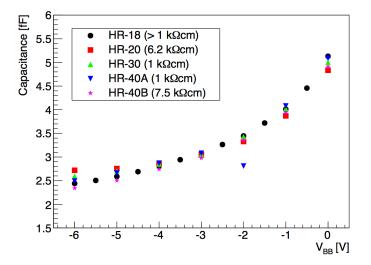

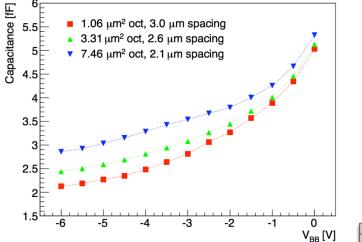

# Sensor optimization – Pixel-input capacitance

### 2. ALPIDE

#### Epitaxial layer resistivity

#### Collection diode geometries:

Pixel input capacitance significantly decreased with increasing  $|V_{BB}|$

~5fF for V<sub>BB</sub>=0V  $\rightarrow$  ~2.5fF for V<sub>BB</sub>=-6V

## Epitaxial layer resistivity

• No influence in range between  $1k\Omega cm$  and  $7.5k\Omega cm$  with current pixel layout

## Collection diode geometry

smaller collection n-well, larger spacing → smaller pixel input capacitance at large V<sub>BB</sub>

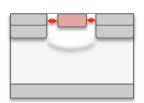

# Sensor optimization – Epitaxial layer thickness

2. ALPIDE

## Prototypes produced on wafer with different epitaxial layer thickness and resistivity

- increasing epitaxial layer thickness:

- generated charge (matrix signal) increases linearly

- cluster size increases non-linearly

Optimum epitaxial layer thickness depending on achievable depletion volume

$\rightarrow$  depending on V<sub>BB</sub> and geometry

Parameters selected for ALPIDE: 25µm epitaxial layer, 2µm n-well diameter, 3µm spacing

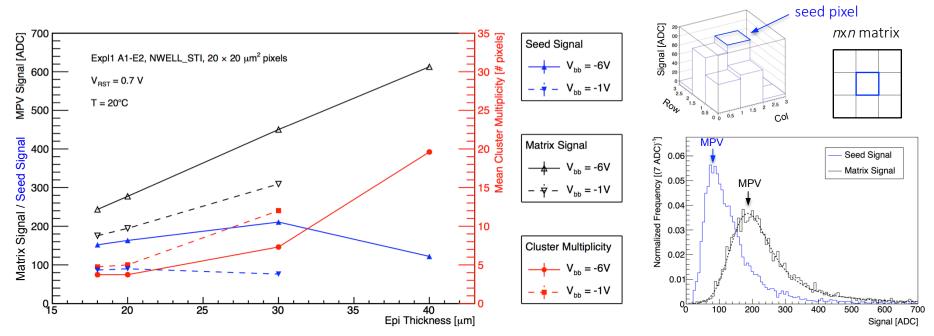

## ALPIDE: Power consumption

Inner Barrel: 41 mW/cm<sup>2</sup> Outer Barrel: 27 mW/cm<sup>2</sup> Data: combination of available measurements and simulations Values scaled for readout at 100 kHz rates and max occupancies

Clock gating enabled

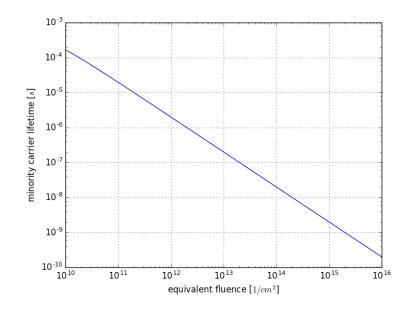

## Carrier lifetime after irradiation

• Carrier lifetime after irradiation:

$1/\tau = 1/\tau_0 + \Phi/K$

where  $\tau$  is the lifetime after irradiation,  $\tau_0$  is the initial lifetime (~1ms in case of our epitaxial layers),  $\Phi$  the equivalent neutron fluence, and K the silicon damage constant (~2e6 s/cm<sup>2</sup>)

- Considering charge collection time of ~1ns, charge collection efficiency should be high up to fluence of about 1e15 n/cm<sup>2</sup> for modified process

- Preliminary results pointing in this direction obtained by Heinz Pernegger, Christian Riegler et al. (ATLAS)

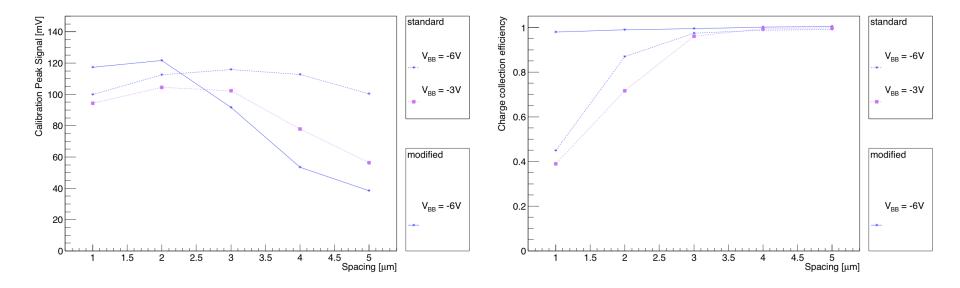

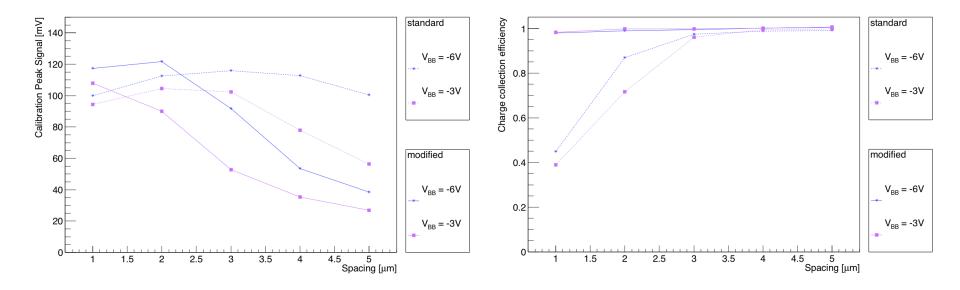

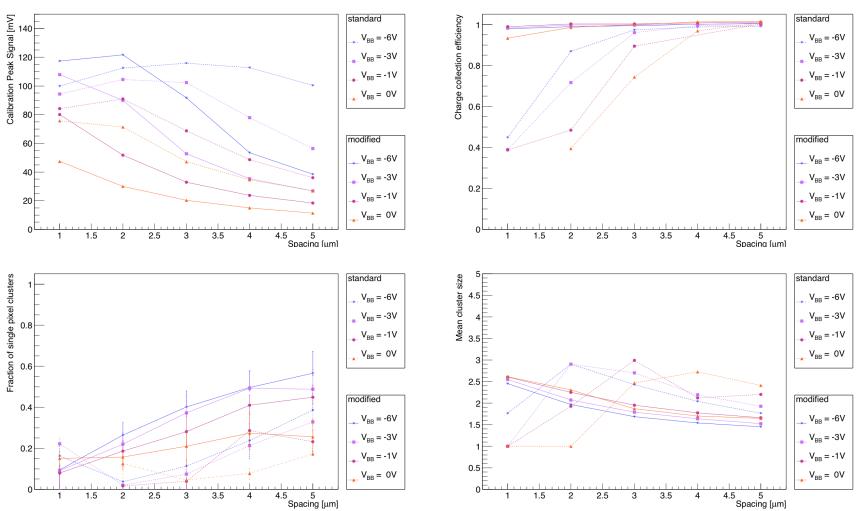

- Example from scan of parameter-space: influence of spacing, at fixed n-well size (2μm), pixel pitch (28μm), and epi-layer thickness (25μm)

- Plots only representing 5 out of 134 mini-matrices!

Optimum spacing different for different process variants, and depending on V<sub>BB</sub> applied

- Example from scan of parameter-space: influence of spacing, at fixed n-well size (2μm), pixel pitch (28μm), and epi-layer thickness (25μm)

- Plots only representing 5 out of 134 mini-matrices!

- Optimum spacing different for different process variants, and depending on V<sub>BB</sub> applied

- Optimum pixel design different for different process variants

- INVESTIGATOR provides efficient tool for scanning parameter space

J.W. van Hoorne, CERN

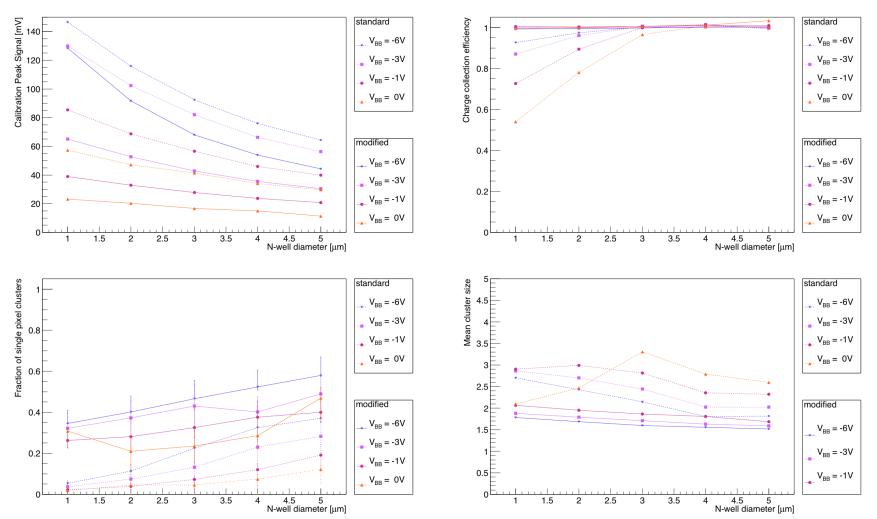

Example from scan of parameter-space: influence of n-well diameter, at fixed spacing (3μm), pixel pitch (28μm), and epi-layer thickness (25μm)

Plots again only representing 5 out of 134 mini-matrices!

19/12/2016

J.W. van Hoorne, CERN

Example from scan of parameter-space: influence of spacing, at fixed n-well size (2μm), pixel pitch (28μm), and epi-layer thickness (25μm)

Plots only representing 5 out of 134 mini-matrices!

19/12/2016

J.W. van Hoorne, CERN

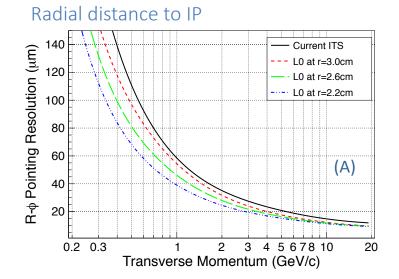

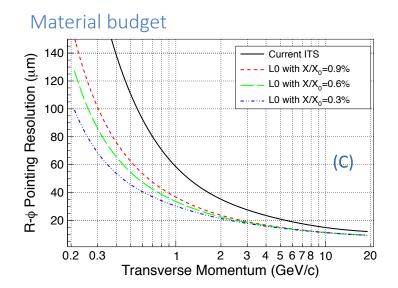

## Performance of new ITS: impact parameter studies

#### 140 Current ITS R- $\phi$ Pointing Resolution ( $\mu m$ ) L0 with $\sigma_{r_{\phi,z}}=12\mu m$ 120 L0 with $\sigma_{r_{\phi,z}} = 8\mu m$ ....... L0 with $\sigma_{r_{\phi,z}} = 4\mu m$ 100 80 **(B)** 60 40 20 0.2 0.3 2 3 4 5 6 7 8 10 1 20 Transverse Momentum (GeV/c)

Spatial resolution

- Current ALICE ITS

- radial position of first layer: 39mm

- $\circ$  x/X<sub>0</sub>: 1.14% per layer

- o spatial resolution (r-phi): 12 mm

- A) current ITS + L0: x/X0 = 0.3%, res.=4mm;

- B) current ITS + L0: r = 22mm, x/X<sub>0</sub> = 0.3%;

- C) current ITS + L0: r = 22mm, x/X<sub>0</sub> = 0.3%;

ALICE ITS Upgrade CDR, CERN-LHCC-2012-12

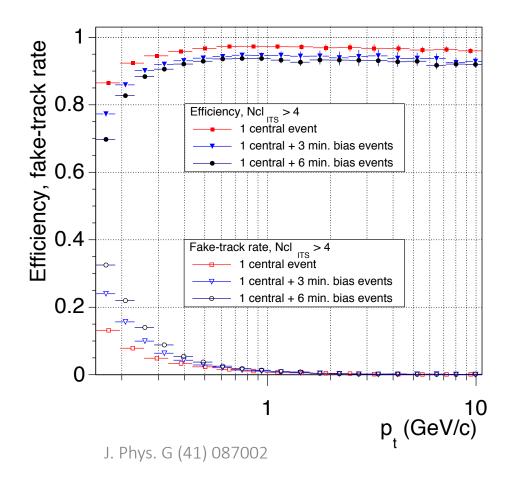

## Performance of new ITS: Matching efficiency

Matching efficiency between the tracks reconstructed in the upgraded ITS and TPC for different values of event pile-up

The average event pile-up depends on the interaction rate and detector integration time

interaction rate 50 kHz integration time: 4 – 30 ms

For 30 ms integration time (worst case design):

<pile-up> = 1 central + 1.5 min. bias

J. Phys. G (41) 087002

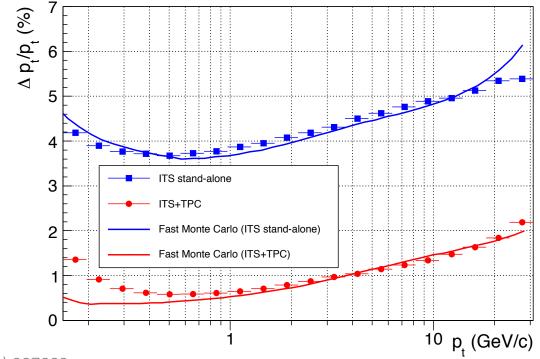

Transverse momentum resolution as function of  $p_T$  for primary charged pions for the upgraded ITS and current ITS. The results are shown for ITS standalone and ITS-TPC combined tracking.

# Performance of new ITS (MC):

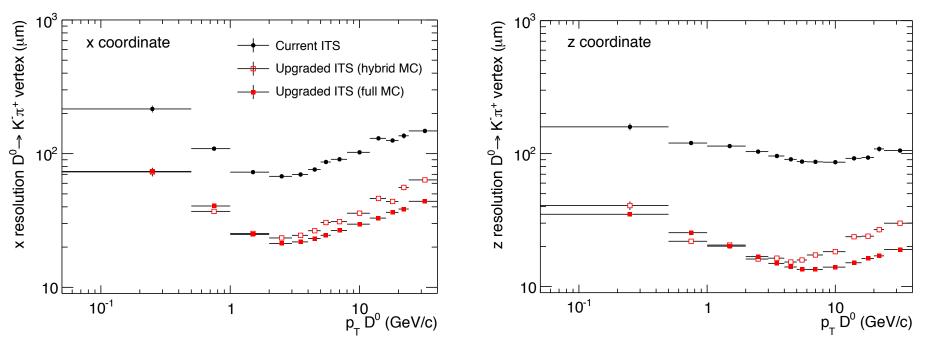

$D^0 \rightarrow K^-p^+$  secondary vertex position resolution

J. Phys. G (41) 087002