GAMMA MEDICA-IDEAS

shift\_out\_d shift\_in\_u vob regout dltb

**V0R7**

**Gamma Medica-Ideas** (Norway) AS

Postal address: PO Box 1 N-1330 Fornebu

Office address: Martin Linges vei 25 N-1367 Snarøya

Internet: www.gm-ideas.com

Phone: +47 6782 7171 Fax: +47 6782 7172

Gamma Medica-Ideas (USA) Inc.

Address: 19355 Business Center Dr. Suite # 8 Northridge, CA 91324

Internet: www.gm-ideas.com

# **Table of Contents**

| 1 ( | General                                          | 3  |

|-----|--------------------------------------------------|----|

| 1.1 | 1 Changes from VATAGP3                           | 3  |

| 2   | General functionality                            | 4  |

| 2.1 | 1 General                                        | 4  |

| 2.2 | 2 Analog Specifications                          | 4  |

| 2.3 | 3 Mechanical and Process                         | 7  |

| 3   | Power supplies                                   | 7  |

| 4   | Pad Description                                  | 8  |

| 5   | Layout                                           | 11 |

| 6   | Functional description:                          | 13 |

| 6.1 |                                                  |    |

| 6.2 | 2 Biasing                                        | 13 |

| 6.3 | 3 Control register                               | 14 |

| 6.4 | 4 Threshold High level                           | 16 |

| 6.5 | 5 ASIC test and calibration                      | 16 |

| (   | 6.5.1 Internal test circuitry                    | 16 |

| (   | 6.5.2 Test channel                               | 17 |

| 6.6 | 5 Threshold Norm/High                            | 17 |

| 6.7 | 7 Dlt (Disable Late Trigger)                     | 17 |

| 6.8 | 8 Channel threshold DACs                         | 18 |

| 6.9 | 9 Global threshold DAC                           | 19 |

| 7   | Readout modes                                    | 19 |

| 7.1 | 1 Mode 1: Serial readout                         | 20 |

| 7.2 | 2 Mode 2: Sparse readout                         | 21 |

| 7.3 | 3 Mode 3: Sparse readout with neighbour channels | 22 |

# 1 General

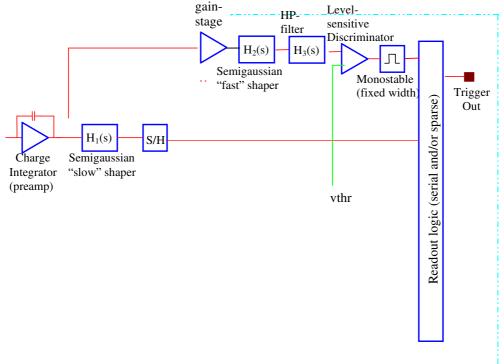

The VATAGP7 is a 128-channel "general purpose" charge sensitive amplifier, based on the VATAGP3. It is pad compatible with VATAGP3. Each channel features low-noise/low-power buffered preamplifiers, a shaper with sample/hold, multiplexed analogue readout and calibration facilities. In addition, each channel has a fast shaper that gives a trigger signal. The analogue value and the address of the triggering channels are read out with a flexible serial or sparse read-out system. The VATAGP7 also offers input leakage current compensation automatically adjusted in each preamplifier channel.

The ASIC is equipped with a test channel for probing the fast shaper output.

The TA-part includes a 4-bit threshold trim DAC for each channel and a 5 bit global threshold trim DAC.

The VATAGP7 is designed for use in systems employing many chips in parallel, sharing some control lines and all output lines with the other modules.

#### 1.1 Changes from VATAGP3

The main changes from the VATAGP3 are as follows:

- 1. New fabrication process. OBS: Please be aware that biases may have changed.

- 2. Gain and peaking times for the slow and fast shapers.

- a. There is no gain-stage.

- b. Fast shaper peaks at 50ns (nominal)

- c. Slow shaper peaks at 500ns (nominal).

- d. Both positive and negative polarity.

- 3. 4 bit "sink-source" threshold trim DACs per channel

- 4. New calibration circuitry accepting a digital input signal. The amplitude of the internally generated cal pulse is set by a DAC.

- 5. DLT/DLTb pads available on the top and bottom side of the ASIC for daisy chaining.

- 6. Possibility to turn on/off the fast shaper slew rate compensation with the slow control.

## 2 General functionality

#### 2.1 General

| Parameter          | Conditions | Value | Units | Comment |

|--------------------|------------|-------|-------|---------|

| Number of channels |            | 128   |       |         |

#### 2.2 Analog Specifications

The values given in this section are typical figures based on simulations. All parameters are simulated at room temperature, with default biases and voltage supply levels.

| Parameter                            | Conditions                                      | Value           | Units                       | Comment                                                                                                                |

|--------------------------------------|-------------------------------------------------|-----------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------|

| Gain                                 | From input to output of output buffer           | 16.5            | μA /fC<br>(typ)             | The differential output currents are summed                                                                            |

| Input potential of preamplifiers     | Referenced to AGND                              | -1.0 to<br>-1.2 | V (typ)                     |                                                                                                                        |

| Electronic (thermal)<br>noise        | Zero input capacitance,<br>zero leakage current | 70              | e <sup>-</sup> (typ)        | Default biases                                                                                                         |

| Electronic (thermal)<br>noise, slope |                                                 | 12              | e <sup>-</sup> /pF (typ)    |                                                                                                                        |

| Leakage current noise, slope         |                                                 |                 | e <sup>-</sup> /nA<br>(typ) | Note: noise<br>contributions add in<br>quadrate                                                                        |

| Dynamic range                        |                                                 | +/-30           | fC (typ)                    | The nominal range is<br>up to 30fC but the asic<br>will not saturate until<br>50 fC. Good linearity<br>up to +/-15 fC. |

| Lowest threshold                     | No input capacitance                            | 0.12            | fC (typ)                    | No load, 5 sigma from noise floor.                                                                                     |

| Lowest threshold                     | 6pF load                                        | 0.3             | fC                          | 6pF load at preamp<br>input., 5 sigma from<br>noise floor.                                                             |

| Peaking time<br>(Slow shaper)        |                                                 | 400             | ns (min)                    | Adjustable by overriding of biases.                                                                                    |

|                                      |                                                 | 500<br>900      | ns (typ)<br>ns (max)        | Default<br>Adjustable by                                                                                               |

| Peaking time<br>(Fast shaper)        |                                                 |                 | ns (min)                    | overriding of biasesAdjustable byoverriding of biases                                                                  |

|                                      |                                                 | 50              | ns (typ)<br>ns (max)        | Default<br>Adjustable by<br>overriding of biases                                                                       |

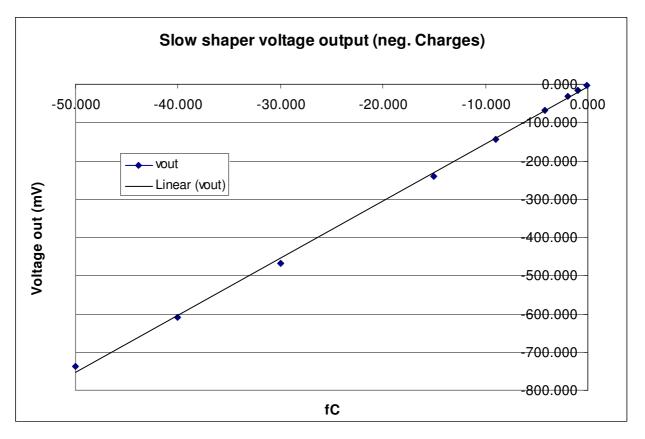

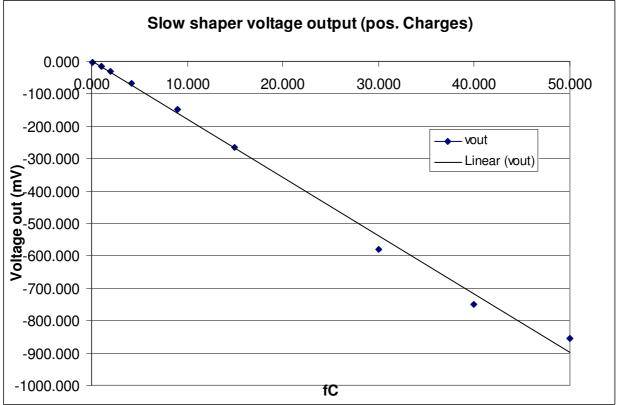

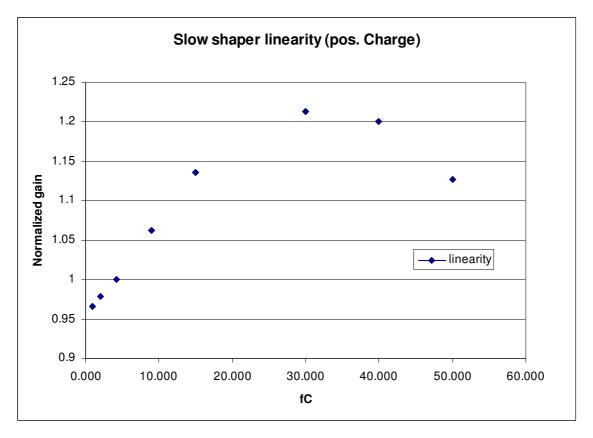

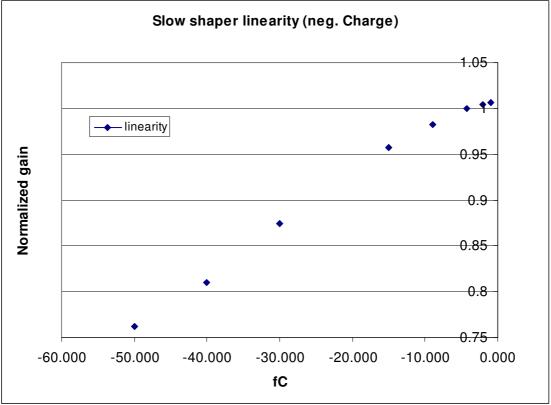

Simulated linearity for positive and negative charges for the slow-shaper. The shaper is optimized for charges up to +/- 15 fC.

Nonlinearity for the slow shaper, for positive and negative charges.

### 2.3 Mechanical and Process

The figures given for the Human Body Model are typical values, but have not necessarily been measured for all pins.

| Parameter             | Conditions            | Value   | Units    | Comment                  |

|-----------------------|-----------------------|---------|----------|--------------------------|

| Manufacturing process |                       | 0.35    | μm       | CMOS, NOT epitaxial      |

|                       |                       |         |          | layer wafers             |

| Die size, length      | Not including scribe. | ~8100   | μm       | From preamplifier        |

|                       |                       |         |          | inputs to parallel       |

|                       |                       |         |          | outputs                  |

| Die size, width       | Not including scribe. | ~6120   | μm       |                          |

| Thickness             |                       | 725     | μm (typ) |                          |

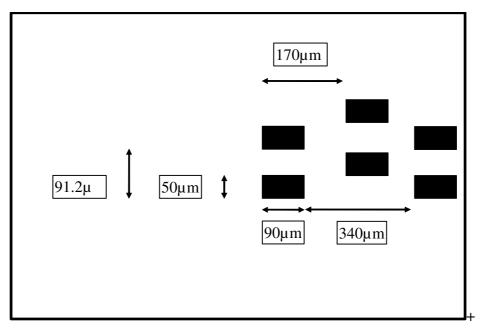

| Bonding pad pitch     | Double row            | 91.2    | μm       | Preamplifier input pads  |

|                       | Single row            | 140     | μm       | Control, output, bias,   |

|                       |                       |         |          | and power pads           |

| Bonding pad size      | Double row            | 90 x 50 | μm       | Preamplifier input pads  |

|                       |                       |         |          | (and preamp output)      |

|                       |                       | 90 x 90 | μm       | Control, output, bias,   |

|                       |                       |         |          | and power pads           |

| Bonding pad series    |                       | 0       | Ω        | Preamplifier input pads  |

| resistance            |                       |         |          | and parallel output      |

|                       |                       | 0/300   | Ω        | Control, output, bias,   |

|                       |                       |         |          | and power pads           |

| Bonding pad ESD       | Measured by the       | 2000    | V (typ)  | Preamplifier input       |

| protection            | Human Body Model.     |         |          | pads, protection diodes. |

|                       | Measured by the       | >2000   | V (typ)  | Control, output, bias,   |

|                       | Human Body Model.     |         |          | and power pads           |

# **3** Power supplies

| Parameter                  | Value      | Description, comment                                       |

|----------------------------|------------|------------------------------------------------------------|

| Power supply: AVDD         | +1.5V ref. | Positive power supply for the preamplifier and shaper.     |

|                            | AGND       |                                                            |

| Power supply: AVSS         | -2.0V ref. | Negative power supply for the preamplifier and shaper.     |

|                            | AGND       | Connect to ASIC back plane.                                |

| Power supply: AGND         | 0V         | Ground for the preamplifier. Note: the detector bias       |

|                            |            | must be decoupled to this ground close to the ASIC.        |

| Power supply: DVDD         | +1.5V      | Power for the digital back-end                             |

| Power supply: DVSS         | -2.0V      | Ground for the digital back-end                            |

| Back contact               | -2.0V      | Connect to AVSS                                            |

| Current consumption, +1.5V | 40mA       | Current consumption from AVDD+DVDD. Current is             |

| supply, 128 channels       |            | into ASIC.                                                 |

| Current consumption, 0V    | 40mA       | Current consumption from AGND. Current is into             |

| supply, 128 channels       |            | ASIC.                                                      |

| Current consumption,       | 80mA       | Sum of the two currents above. Current is <u>out</u> ASIC. |

| -2V supply, 128 channels   |            |                                                            |

| Parameter             | Value   | Description, comment |

|-----------------------|---------|----------------------|

| Power dissipation per | ~2.2 mW | Approx.              |

| channel               |         |                      |

### 4 Pad Description

Bias pads which do not require bonding (internally generated or pull-up/pull-down) can be bonded for external decoupling, adjustment or forcing. Pads described clock-wise from upper left to lower left (excluding input pads). Positive current direction is into the chip.

| Pad name    | Туре  | Description                       | Nominal value       |

|-------------|-------|-----------------------------------|---------------------|

| shift_in_d  | di    | Shift register input (downwards)  | logical             |

| shift_out_u | do    | Shift register output (upwards)   | logical             |

| vi          | ldi   | Veto input (pos. phase)           | low v. logical (pd) |

| vib         | ldi   | Veto input (neg. phase)           | low v. logical (pu) |

| regin       | di    | Data input for control register   | logical (pd)        |

| dlt         | di/do | Disable late trigger (pos. phase) | current             |

| dltb        | di/do | Disable late trigger (neg. phase) | current             |

Pad-row on the ASIC top side:

Pad-row on the ASIC right side:

| Pad name  | Туре | Description                         | Nominal value       |

|-----------|------|-------------------------------------|---------------------|

| AGND      | р    | Signal ground for the analogue part | 0 V                 |

| DGND      | р    | Connect to AGND                     | 0 V                 |

| DVDD      | р    | Digital vdd                         | 1.5 V               |

| DVSS      | р    | Digital vss                         | -2 V                |

| clkin     | di   | Clock for control register          | logical             |

| sh        | ldi  | Sample and hold (pos. phase)        | low v. logical      |

| shb       | ldi  | Sample and hold (neg. phase)        | low v. logical      |

| res       | ldi  | Reset of the readout logic (pos.    | low v. logical (pd) |

|           |      | phase)                              |                     |

| resb      | ldi  | Reset of the readout logic (neg.    | low v. logical (pu) |

|           |      | phase)                              |                     |

| shiftreg  | ldi  | Readout mode (pos. phase)           | low v. logical (pu) |

| shiftregb | ldi  | Readout mode (neg. phase)           | low v. logical (pd) |

| gck       | ldi  | Clock for readout (pos. phase)      | low v. logical      |

| gckb      | ldi  | Clock for readout (neg. phase)      | low v. logical      |

| addr0-6   | do   | Digital output of hit channel       | current             |

|           |      | address                             |                     |

| Pad name | Туре | Description                                                             | Nominal value                                        |

|----------|------|-------------------------------------------------------------------------|------------------------------------------------------|

| :        | :    | :                                                                       | :                                                    |

| addr7-10 | do   | Digital output of chip address                                          | current                                              |

| ioref    | ai   | Current sink for the address output buffer                              | Connect to ~0V                                       |

| mgo      | ao   | Multi-hit trigger output                                                | current                                              |

| to       | ldo  | Trigger out (positive phase). 0/-125<br>uA                              | current                                              |

| tob      | ldo  | Trigger out (negative phase) ).0/<br>125 uA                             | current                                              |

| vthrh    | ai   | High threshold for the discriminator                                    | 2V /-2V?<br>(depending on<br>signal polarity)        |

| vfsf     | ai   | Control voltage for the feedback resistor (NMOS) in the fast shaper     | -125 mV pos. sig.<br>-300 mV neg sig.<br>(int. gen.) |

| vfss     | ai   | Control voltage for the feedback<br>resistor (NMOS) in the slow shaper  | -150 mV pos. sig.<br>-350 mV neg sig.<br>(int. gen.) |

| vfp      | ai   | Control voltage for the feedback<br>resistor (NMOS) in the preamplifier | -610 mV pos. sig.<br>-550 mV neg sig.<br>(int. gen.) |

| outm_u   | ao   | Diff. analog output, neg. phase (upwards shiftregister)                 | 0-200 uA                                             |

| outp_u   | ao   | Diff. analog output, pos. phase<br>(upwards shiftregister)              | 0-200 uA                                             |

| outm_d   | ao   | Diff. analog output, neg. phase<br>(downwards shiftregister)            | 0-200 uA                                             |

| outp_d   | ao   | Diff. analog output, pos. phase<br>(downwards shiftregister)            | 0-200 uA                                             |

| vthr     | ai   | Normal threshold for the discriminator                                  | > 50 mV?                                             |

| cali     | ai   | Test pulse with internal or external capacitor                          | voltage step /<br>charge                             |

| Cal_trig | ai   | Trigger input for the internal cal generation.                          | Logic                                                |

| mbias    | ai   | Bias reference for all the internally generated biases                  | 500 uA                                               |

| AVSS_CC  | ai   | Reference for current compensation                                      | -2 V                                                 |

| AVDD     | р    | Analog vdd                                                              | 1.5 V                                                |

| AVSS     | р    | Analog vss                                                              | -2 V                                                 |

Pad-row on the ASIC bottom side:

| Pad name | Туре  | Description                       | Nominal value |

|----------|-------|-----------------------------------|---------------|

| dlt      | di/do | Disable late trigger (pos. phase) | current       |

| dltb     | di/do | Disable late trigger (neg. phase) | current       |

| Pad name    | Туре | Description                         | Nominal value  |

|-------------|------|-------------------------------------|----------------|

| regout      | do   | Data output of the control register | logical        |

| vob         | ldo  | Veto output (neg. phase)            | low v. logical |

| vo          | ldo  | Veto output (pos. phase)            | low v. logical |

| shift_in_u  | di   | Shiftregister input (upwards)       | logical        |

| shift_out_d | do   | Shiftregister output (downwards)    | logical        |

p = power, di = digital in, do = digital out, ldi = low voltage differential digital in,ldo = low voltage differential digital out, ai=analogue in, ao = analogue out,pu = pull-up, pd = pull-downLow voltage logical = 0V("1") / -0.2V("0")Logical = +1.5V("1") / -2V("0")

Pads on the second pad-row, listed from upper to lower. These pads are for over-riding of internally generated biases.

| Pad name  | Туре  | Description                       | Nominal value      |

|-----------|-------|-----------------------------------|--------------------|

| vrcp      | ai    | Control voltage for HP -filter    | -560 mV neg.       |

|           |       | resistor (PMOS) in front of       | sig.               |

|           |       | discriminator                     | (int. gen.)        |

| vpz       | ai    | Control voltage to feedback       |                    |

|           |       | resistance in gain stage.         |                    |

| Obi_indrv | ai    | Bias for the input receivers      | 90 uA (int. gen.)  |

| Mo_bi     | ai    | Bias for the address and mgo      | -140 uA(int.gen.)  |

|           |       | current sources.                  |                    |

| vref      | ao/ai | Reference for the output buffer,  | ~500 mV            |

|           |       | internally generated by a dummy   |                    |

|           |       | slow shaper                       |                    |

| twb       | ai    | Trigger width bias                | -10 uA (int. gen.) |

| sbif      | ai    | Bias for the fast shaper          | 22 uA (int. gen.)  |

| vrcn      | ai    | Control voltage for HP -filter    | 790 mV pos. sig.   |

|           |       | resistor (NMOS) in front of       | -2V neg. sig.      |

|           |       | discriminator                     | (int. gen.)        |

| prebias   | ai    | Bias for the preamplifiers        | 500 uA (int.       |

|           |       |                                   | gen.)              |

| sbis      | ai    | Bias for the slow shaper          | 22 uA (int. gen.)  |

| ibuf      | ai    | Bias for the analog output buffer | 225 uA (int.       |

|           |       |                                   | gen.)              |

| ref_bi    | ai    | Bias for threshold DACs           | 10 uA (int. gen.)  |

| obi       | ai    | Bias for the discriminators       | 90 uA (int. gen.)  |

### 5 Layout

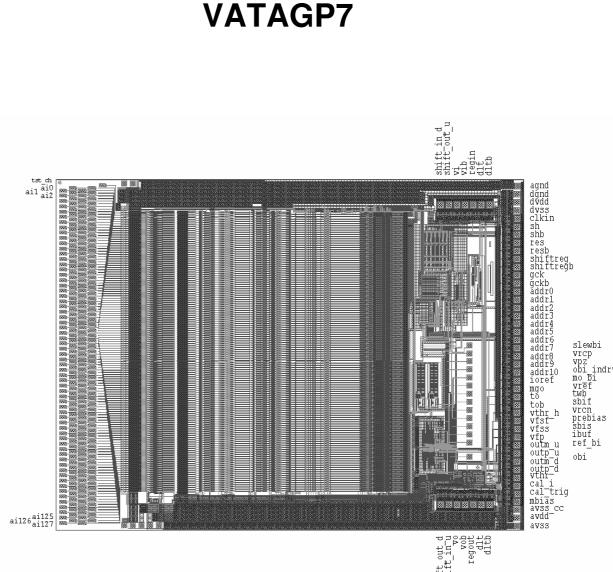

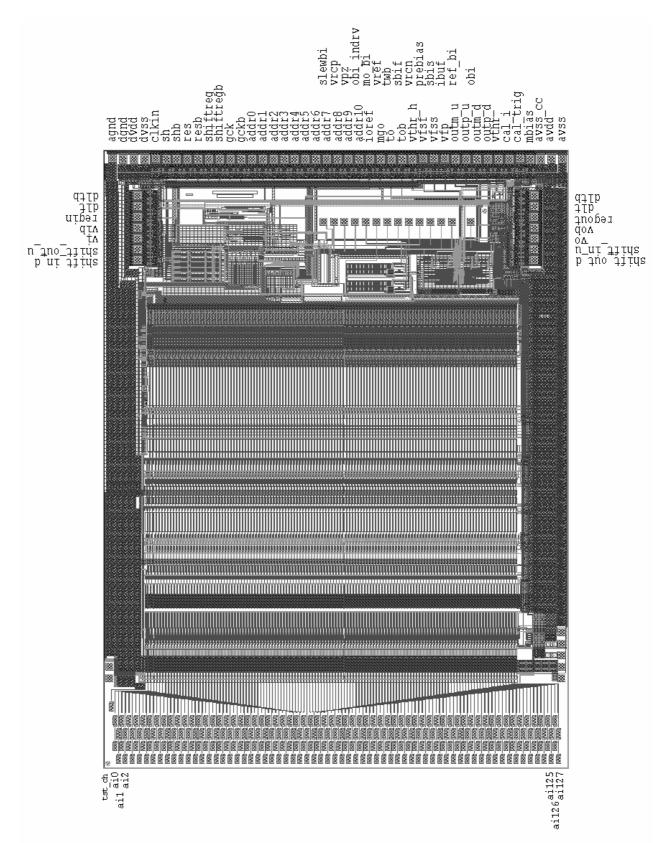

Figure 1: Preliminary chip plot of the VATAGP7.

Figure 2: Definition of input pad size and pitch.

# 6 Functional description:

(See the following text for more detailed information)

#### 6.1 Using VATAGP7 in parallel:

The VATAGP7 is designed to be used in parallel for reading out a large number of channels. There are 4 bits for the chip address, giving a maximum of 16 chips on the same bus, with a total of 2048 channels. The pads are placed such that signals going from one chip to the next are on the opposite side. This makes the PCB routing easy. The signals should be connected as shown below: (chip number in parenthesis)

```

vo(1) to vi(2)

vob(1) to vib(2)

shift_out_u(1) to shift_in_u(0)

shift_out_d(1) to shift_in_d(2)

regout(1) to regin(2)

inp_drain(1) to inp_drain(2)

```

All other control signals should be in parallel.

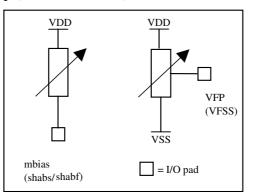

#### 6.2 Biasing

The VATAGP7 is designed to have only one external bias: *mbias*. All other biases are internally generated, where all biases are a fraction of *mbias*. However, sometimes it is necessary to adjust

or force the biases to other values than the nominal. Pads are available for all biases making external adjustment is possible.

### Generation of bias currents/voltages

Figure 3 shows a possible approach for generating the necessary bias currents and voltages. *mbias* is a current **into** the chip (resistor to VDD).

Figure 3: Bias current and voltage generation

### Decoupling of power and bias lines

It is recommended to decouple the power and bias lines to GND.

Use 100 nF ceramic capacitors on the power lines as close as possible to each chip and  $1 - 100 \mu$ F tantalum capacitors common for all chips on a PCB. Use 100 nF on the *mbias* (and eventually other biases that are externally generated) close to the chip.

#### 6.3 Control register

The VATAGP7 has 926 bit long control register, set by *regin* and *clkin*. Typical contents of the register is shown below.Bit <sup>1)</sup>NameFunctionComment

| <b>Bit</b> <sup>1)</sup> | Name        | Function                   | Comment                                             |

|--------------------------|-------------|----------------------------|-----------------------------------------------------|

| 1                        | Vrc select  | Select which internal Vrc  | $0 \rightarrow 0.7 \text{ V} \text{ (pos. sig.)}$   |

|                          |             | value to use               | $1 \rightarrow 0.9 \text{ V} (\text{neg. sig.})$    |

| 2                        | Vfsf select | Select which internal Vfsf | $0 \rightarrow$ -125 mV (pos. sig.)                 |

|                          |             | value to use               | $1 \rightarrow -255 \text{ mV} \text{ (neg. sig.)}$ |

| 3                        | Vfss select | Select which internal Vfss | $0 \rightarrow$ -75 mV (pos. sig.)                  |

|                          |             | value to use               | $1 \rightarrow -135 \text{ mV} \text{ (neg. sig.)}$ |

| 4                        | Vfp select  | Select which internal Vfp  | $0 \rightarrow -610 \text{ mV} \text{ (pos. sig.)}$ |

|                          |             | value to use               | $1 \rightarrow -550 \text{ mV} \text{ (neg. sig.)}$ |

| 5                        | cc_enable   | Enable current             | $0 \rightarrow CC \text{ off}$                      |

|                          |             | compensation (CC)          | $1 \rightarrow CC$ on                               |

| 6                        | n_side      | Readout of n-side of the   | $0 \rightarrow p$                                   |

|                          |             | detector (integrating      | $1 \rightarrow n$                                   |

| <b>Bit</b> <sup>1)</sup> | Name                 | Function                    | Comment                                     |  |  |  |  |  |  |

|--------------------------|----------------------|-----------------------------|---------------------------------------------|--|--|--|--|--|--|

|                          |                      | electrons).                 |                                             |  |  |  |  |  |  |

| 7                        | test_on              | Test mode on                | $0 \rightarrow \text{test off}$             |  |  |  |  |  |  |

|                          |                      |                             | $1 \rightarrow \text{test on}$              |  |  |  |  |  |  |

| 8                        | select               | Select signal polarity      | $0 \rightarrow \text{positive}$             |  |  |  |  |  |  |

|                          |                      |                             | $1 \rightarrow negative$                    |  |  |  |  |  |  |

| 9:12                     | addr[10:7]           | chip address                |                                             |  |  |  |  |  |  |

| 13                       | Cal_gen              | Enable internal calibration | High means that the                         |  |  |  |  |  |  |

|                          |                      | circuit                     | internal circuit is                         |  |  |  |  |  |  |

|                          |                      |                             | connected to the cal-line.                  |  |  |  |  |  |  |

| 14                       | calc                 | Calibration ctrl            | $0 \rightarrow \text{internal}$ cal. Step   |  |  |  |  |  |  |

|                          |                      |                             | $1 \rightarrow \text{external}$ generation. |  |  |  |  |  |  |

| 15                       | Vrc_neg select       |                             | $0 \rightarrow \text{positive}$             |  |  |  |  |  |  |

|                          |                      |                             | $1 \rightarrow negative$                    |  |  |  |  |  |  |

| 16                       | Reserved.            |                             | Set to 0.                                   |  |  |  |  |  |  |

| 17                       | Slew_on              | Bit for turning on the fast | $0 \rightarrow \text{off}$                  |  |  |  |  |  |  |

|                          |                      | shaper slew rate            | $1 \rightarrow \text{on}$                   |  |  |  |  |  |  |

| 18                       | Dac_range            | Select 2x dac range         | Increases the threshold                     |  |  |  |  |  |  |

|                          |                      |                             | trim dac range by 2x when                   |  |  |  |  |  |  |

|                          |                      |                             | selected.                                   |  |  |  |  |  |  |

| 19                       | dltc                 | Disable late trigger (DLT)  | $0 \rightarrow DLT$ active                  |  |  |  |  |  |  |

|                          |                      |                             | $1 \rightarrow DLT$ inactive                |  |  |  |  |  |  |

| 20:147                   | Threshold            | Disable channel             | $0 \rightarrow$ enable (norm)               |  |  |  |  |  |  |

|                          | Norm/High            | (vthrh = +1.5V/-2V)         | $1 \rightarrow \text{disable (high/vthrh)}$ |  |  |  |  |  |  |

| 148:659                  | DAC[3:0] for         | Threshold DACs              |                                             |  |  |  |  |  |  |

|                          | ch[0:127]            |                             |                                             |  |  |  |  |  |  |

| 660                      | test_enable for test | Enable injection of cal-    | $0 \rightarrow \text{disable}$              |  |  |  |  |  |  |

|                          | channel              | pulse into test channel     | $1 \rightarrow \text{enable}$               |  |  |  |  |  |  |

| 661:788                  | test_enable for      | Enable injection of cal-    | $0 \rightarrow \text{disable}$              |  |  |  |  |  |  |

|                          | ch[0:127]            | pulse into channel          | $1 \rightarrow \text{enable}$               |  |  |  |  |  |  |

| 789                      | Reserved for         |                             | Leave at 0 for normal use.                  |  |  |  |  |  |  |

|                          | calibration test     |                             |                                             |  |  |  |  |  |  |

|                          | purposes for test    |                             |                                             |  |  |  |  |  |  |

| <b>7</b> 00.01-          | channel              |                             |                                             |  |  |  |  |  |  |

| 790:917                  | Reserved for         |                             | Leave at 0 for normal use.                  |  |  |  |  |  |  |

|                          | calibration test     |                             |                                             |  |  |  |  |  |  |

| 010.000                  | purposes.            |                             |                                             |  |  |  |  |  |  |

| 918:922                  | Global threshold     | 5 bit global threshold trim |                                             |  |  |  |  |  |  |

| 000 000                  | dac                  | dac                         |                                             |  |  |  |  |  |  |

| 923:926                  | CAL dac step         | 4 bit dac to select the     |                                             |  |  |  |  |  |  |

|                          |                      | internal cal step.          |                                             |  |  |  |  |  |  |

1) Bit number in the control register. Bit 1 is the first bit after *regin*, bit 926 is the last bit before *regout*. Reverse the order when downloading the bit stream (download bit 926 first and bit 1 last).

#### 6.4 Threshold High level

The vthrh pad is used to set the discriminator high level. When a channel is disabled, this voltage is feed to the discriminator instead of the vthr voltage.

#### 6.5 ASIC test and calibration

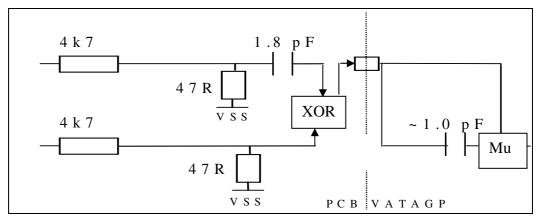

Each channel can be individually tested. This function is enabled by setting bit *test\_on* in the control register to "1". The *test\_enable* mask must have one of its bits set to "1" which will select the corresponding channel (selecting more than one channel is possible due to AC coupling on the inputs but is not expected to be very useful). The channel(s) that has been selected will be sensitive to test-signals injected at the *cal* inputs.

When choosing externally AC coupled input signal, place the 1.8 pF capacitor very close to the chip to prevent pickup. Otherwise, there is a  $\sim$ 1.0 pF internal capacitor on the chip.

A voltage step of 10 mV on the 1.8 pF capacitor gives an input signal charge of 18 fC (~5 MIP).

#### 6.5.1 Internal test circuitry

The asic supports external cal capacitor, internal cal capacitor with external cal-step, or internally generated cal-step and internal capacitor triggered by an external trigger pulse. The following table show the different calibration modes selectable with the two control bits cal\_gen and calc:

| Cal_gen | Calc | Cal_mode                       |  |  |  |

|---------|------|--------------------------------|--|--|--|

| 0       | 0    | Internal cap, external step    |  |  |  |

| 1       | 0    | Internal cap, internal step    |  |  |  |

| 0       | 1    | External cap, external step    |  |  |  |

| 1       | 1    | Not for normal use. Will send  |  |  |  |

|         |      | the internal cal charge out to |  |  |  |

|         |      | the cal pad.                   |  |  |  |

The cal-dac will have 4 bits. Each setting corresponds to the following table:

| Bit1 | Bit2 | Bit3 Bit4 |   | Cal pulse [fC] |

|------|------|-----------|---|----------------|

| 0    | 0    | 0         | 0 | 18             |

| 0    | 0    | 0         | 1 | 15.75          |

| 0    | 0    | 1         | 0 | 13.5           |

| 0 | 0 | 1 | 1 | 11.25 |

|---|---|---|---|-------|

| 0 | 1 | 0 | 0 | 9     |

| 0 | 1 | 0 | 1 | 6.75  |

| 0 | 1 | 1 | 0 | 4.5   |

| 0 | 1 | 1 | 1 | 2.25  |

| 1 | 0 | 0 | 0 | 18    |

| 1 | 0 | 0 | 1 | 20.25 |

| 1 | 0 | 1 | 0 | 22.5  |

| 1 | 0 | 1 | 1 | 24.75 |

| 1 | 1 | 0 | 0 | 27    |

| 1 | 1 | 0 | 1 | 29.25 |

| 1 | 1 | 1 | 0 | 31.5  |

| 1 | 1 | 1 | 1 | 33.75 |

The relationship between the CAL-DAC and the cal-pulse.

#### 6.5.2 Test channel

This ASIC is equipped with a test channel for monitoring the fast shaper output. It has a dedicated probe pin for this purpose. You can either apply a signal directly to the input through an input pad or through the cal. input. The input draining feature can also be tested on this channel.

#### 6.6 Threshold Norm/High

This bit chooses between a normal threshold and a disabling high threshold. However, the high threshold level could be chosen to be a transparent level, e.g. does not discriminate any signal. The threshold high level is set with the vthrh pad.

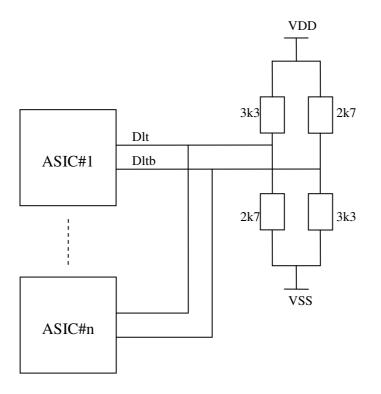

#### 6.7 Dlt (Disable Late Trigger)

The Dlt circuit of the ASIC has both a driver and a sense function. This enables the possibility for disabling late triggers between several interconnected ASICs. The sense circuit is a simple comparator while the driver has an open-drain configuration which requires external termination.

NB! The Dltc-bit in the control register disables the driver, not the sense-comparator.

The figure below shows a typical way of terminating the Dlt:

#### 6.8 Channel threshold DACs

The channel threshold DACs has nominally 1 mV step size. The step size can be changed by forcing a different  $ref_bi$ . The step size in [mV] is **ref\_bias[uA] \* 0.1**. The DAC is sink-source type, and will ideally leave no return current in the threshold line.

| DAC0 | DAC1 | DAC2 | DAC3 | Threshold adjust |

|------|------|------|------|------------------|

|      |      |      |      | (ref_bias=10uA)  |

| 0    | 0    | 0    | 0    | 0 mV             |

| 0    | 0    | 0    | 1    | -1 mV            |

| 0    | 0    | 1    | 0    | -2 mV            |

| 0    | 0    | 1    | 1    | -3 mV            |

| 0    | 1    | 0    | 0    | -4 mV            |

| 0    | 1    | 0    | 1    | -5 mV            |

| 0    | 1    | 1    | 0    | -6 mV            |

| 0    | 1    | 1    | 1    | -7 mV            |

| 1    | 0    | 0    | 0    | 0 mV             |

| 1    | 0    | 0    | 1    | 1 mV             |

| 1    | 0    | 1    | 0    | 2 mV             |

| 1    | 0    | 1    | 1    | 3 mV             |

| 1    | 1    | 0    | 0    | 4 mV             |

| 1    | 1    | 0    | 1    | 5 mV             |

| 1    | 1    | 1    | 0    | 6 mV             |

| 1    | 1    | 1    | 1    | 7 mV             |

### 6.9 Global threshold DAC

This DAC is for trimming the global threshold. This could also be used to even out offset currents that are generated when the channel DACs have been adjusted. Therefore, this DAC has the same current step-size as the channel DACs.

NB! For this DAC to work an external resistor has to be placed on the threshold line. The step in mV will be: Rext \* 2.5  $\mu$ A.

| DAC0 | DAC1 | DAC2 | DAC3 | DAC4 | Threshold adjust |

|------|------|------|------|------|------------------|

|      |      |      |      |      | (ref_bias=10uA)  |

| 0    | 0    | 0    | 0    | 0    | 0 mV             |

| 0    | 0    | 0    | 0    | 1    | -2.5 µA * Rext   |

| 0    | 0    | 0    | 1    | 0    | -5.0 µA * Rext   |

| 0    | 0    | 0    | 1    | 1    | -7.5 µA * Rext   |

| 0    | 0    | 1    | 0    | 0    | -10.0 µA * Rext  |

| 0    | 0    | 1    | 0    | 1    | -12.5 µA * Rext  |

| 0    | 0    | 1    | 1    | 0    | -15.0 µA * Rext  |

| 0    | 0    | 1    | 1    | 1    | -17.5 µA * Rext  |

| 0    | 1    | 0    | 0    | 0    | -20.0 µA * Rext  |

| 0    | 1    | 0    | 0    | 1    | -22.5 µA * Rext  |

| 0    | 1    | 0    | 1    | 0    | -25.0 µA * Rext  |

| 0    | 1    | 0    | 1    | 1    | -27.5 µA * Rext  |

| 0    | 1    | 1    | 0    | 0    | -30.0 µA * Rext  |

| 0    | 1    | 1    | 0    | 1    | -32.5 µA * Rext  |

| 0    | 1    | 1    | 1    | 0    | -35.0 µA * Rext  |

| 0    | 1    | 1    | 1    | 1    | -37.5 µA * Rext  |

| 1    | 0    | 0    | 0    | 0    | 0 mV             |

| 1    | 0    | 0    | 0    | 1    | 2.5 µA * Rext    |

| 1    | 0    | 0    | 1    | 0    | 5.0 µA * Rext    |

| 1    | 0    | 0    | 1    | 1    | 7.5 µA * Rext    |

| 1    | 0    | 1    | 0    | 0    | 10.0 µA * Rext   |

| 1    | 0    | 1    | 0    | 1    | 12.5 µA * Rext   |

| 1    | 0    | 1    | 1    | 0    | 15.0 µA * Rext   |

| 1    | 0    | 1    | 1    | 1    | 17.5 µA * Rext   |

| 1    | 1    | 0    | 0    | 0    | 20.0 µA * Rext   |

| 1    | 1    | 0    | 0    | 1    | 22.5 µA * Rext   |

| 1    | 1    | 0    | 1    | 0    | 25.0 µA * Rext   |

| 1    | 1    | 0    | 1    | 1    | 27.5 µA * Rext   |

| 1    | 1    | 1    | 0    | 0    | 30.0 µA * Rext   |

| 1    | 1    | 1    | 0    | 1    | 32.5 µA * Rext   |

| 1    | 1    | 1    | 1    | 0    | 35.0 µA * Rext   |

| 1    | 1    | 1    | 1    | 1    | 37.5 µA * Rext   |

# 7 Readout modes

The VATAGP7 has three different readout modes. After the physics event, each preamplifier will integrate its eventual signal. The slow shaper will shape the signal with a shaping time of 3us, and the fast shaper with a shaping time of 1us. If the signal of the fast shaper has a value

larger than the external threshold (*vthr* or *vthr\_h*), a trigger on the *to/tob* and *mgo* lines occur. When the slow shaper reaches the signal peak (nominally after 3  $\mu$ s), the external hold signal (*sh/shb*) should be applied to sample the peak value. Immediately after this, the readout can start.

#### 7.1 Mode 1: Serial readout

Readout is similar to the VA+TA type of ASICs from Gamma Medica-Ideas.

A shiftregister will enable readout of one channel at a time. The readout starts with clocking one bit into the first channel of the shiftregister with the *shift\_in\_d* and *gck/gckb* signals. See Figure 5 for an example of the timing in this mode. The logic part of the chip can be reset either by applying the *res/resb*, or by running through the full read-out sequence (more than 128 clocks) so that the last shift bit is clocked out of the register.

On power-up, a reset signal should be applied to reset the internal registers/latches with a pulse (~1  $\mu$ s- 1 ms) on the *res/resb* lines. Eventually, a number of clocks exceeding the number of channels will set the shiftregister to zero.

In this mode, the following input signals are not in use and can be left unconnected:

| shif<br>shif                          | ft_in_u<br>ft_out_u<br>ftreg<br>ftregb | l |  |   | (i<br>(i<br>(i | nto<br>nto | ernal<br>ernal<br>ernal<br>ernal<br>ernal | pull<br>pull<br>pull | up<br>do<br>do | )<br>wn<br>wn | )     |   |   |   |      |             |             |            |         |                       |                                                                                             |                            |             |   |

|---------------------------------------|----------------------------------------|---|--|---|----------------|------------|-------------------------------------------|----------------------|----------------|---------------|-------|---|---|---|------|-------------|-------------|------------|---------|-----------------------|---------------------------------------------------------------------------------------------|----------------------------|-------------|---|

|                                       |                                        |   |  | • | •              |            | t .me                                     |                      | •              |               |       | • | • | • | •    | •           | •           | •          | •       | •                     | •                                                                                           | •                          | •           |   |

| · · · · · · · · · · · · · · · · · · · | , , , , , , , , , , , , , , , , , , ,  |   |  |   |                |            | 3. us.<br>integration                     |                      |                |               |       |   | • |   |      | ·<br>2<br>1 | ·<br>·<br>3 |            |         | ·<br>·<br>·<br>·<br>· | ,<br>,<br>,<br>,<br>,<br>,<br>,<br>,<br>,<br>,<br>,<br>,<br>,<br>,<br>,<br>,<br>,<br>,<br>, | ·<br>·<br>·<br>·<br>·<br>· | ·<br>·<br>· |   |

| 5 TUATIO<br>1 TUATIO<br>1 1 TUA       | mgo ai<br>outp_o<br>shift_             |   |  |   | · ·            |            |                                           |                      |                |               | _t ii |   | • | Ø | <br> | a X I<br>.2 | ) ( 2<br>   | X<br><br>4 | <br> 2€ | 5 X 121               | .128                                                                                        |                            |             | - |

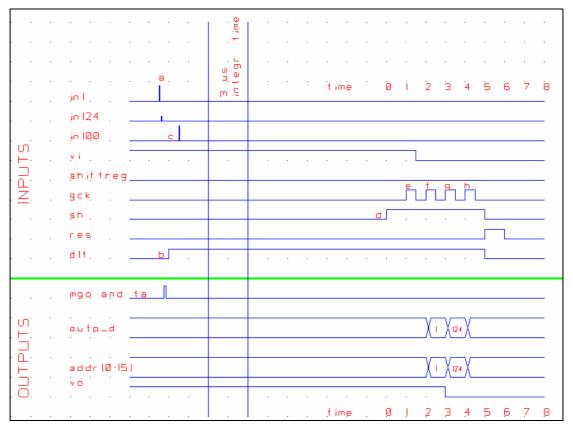

Figure 5: Serial readout

- a) Physics events happen almost simultaneously in channel 1 and 124. Since the signal is larger than the threshold, a trigger (*mgo*, *taltb*) is generated. The fast shaper for the trigger logic has a shaping time of 50 ns, which means that dependent of the signal amplitude and the threshold *vthr*, the trigger can be delayed up to 50 ns.

- b) Another physics event happen some time later in channel 100. This event also generates a trigger.

- c) After 500ns, the sample-and-hold signal *sh/shb* goes high. The signal in channel 1 and 124 has reached the peak, while channel 100 has not fully reached the peak yet.

- d) A shift bit is clocked into the shiftregister by *shift\_in\_d* and *gck/gckb*. The analogue value of channel 0 is enabled at *outp\_d/outm\_d*. For each clock (*gck/gckb*), the shiftbit is clocked to the next channel.

- e) The last channel is enabled. The *shift\_out\_d* goes high to give a *shift\_in* for the next chip in the chain.

- f) A reset is applied to reset the shiftregister. This is not necessary if all channels have been clocked, so that the shift bit has been clocked out of the chip.

#### 7.2 Mode 2: Sparse readout

In this readout mode, only the channels with a trigger (signal above the threshold) will be read out to increase the readout speed. As in serial readout, the hold signal *sh/shb* must be applied 500 ns after the trigger.

If Dlt is deactivated all channels with a trigger will get a read tag. By clocking once with the gck/gckb, the analogue value and the address of the first channel with a tag will be available on the output. After the next clock of gck/gckb, the next channel with a tag will be available. The vo signal goes low when all channels with triggers are read out. If the chip shall be reset before all channels are read out, apply the *res/resb* signal.

In this mode, the following input signals are not in use and can be left unconnected:

| shift_in_u  | (internal pull down) |

|-------------|----------------------|

| shift_out_u |                      |

| shift_in_d  | (internal pull down) |

| shift out d |                      |

These signals have a fixed level:

| vi (chip 0)  | connect to VSS (logic low)  |

|--------------|-----------------------------|

| vib (chip 0) | connect to VDD (logic high) |

| shiftreg     | connect to VSS (logic low)  |

| shiftregb    | connect to VDD (logic high) |

Figure 6: Sparse readout

- a) Physics events happen almost simultaneously in channel 1 and 124. Since the signal is larger than the threshold, a trigger (mgo, ta/tb) is generated. The fast shaper for the trigger logic has a shaping time of 50ns, which means that dependent of the signal amplitude and the threshold, the trigger can be delayed up to 50ns.

- b) The disable\_late\_trigger *dlt* is applied. This will discard all triggers after this moment.

- c) Another physics event happen some time later in channel 100. No trigger is given because *dlt* is high.

- d) After 500ns, the sample-and-hold signal *sh/shb* goes high. The signal in channel 1 and 124 has reached the peak and are held.

- e) The *gck/gckb* clocks once. Since veto in *vi* from the previous chip in the chain is high, no action is taken.

- f) The *gck/gckb* clocks once. Veto in *vi* is low, and the first channel with a hit is enabled at the output together with its address.

- g) The next and last channel with a hit is enabled at the output together with its address. Veto out *vo* goes low to indicate that all channels are read out and enable readout of the next chip in the chain.

- h) *Sh* and *dlt* goes low. A reset is applied to reset the shiftregister by a pulse on *res/resb*. This is not necessary if all hit channels have been clocked, so that the veto out in the last chip has gone low.

#### 7.3 Mode 3: Sparse readout with neighbour channels

This mode is equal to the sparse readout, except that the neighbours of the channel(s) with trigger can also be read out.

As in serial readout, the hold signal *sh/shb* must be applied 500ns after the trigger.

If Dlt is deactivated all channels that trigger will get a read tag. By clocking once with the *gck/gckb* and with *shiftreg* low, the analogue value and the address of the first channel with a tag will be available on the output. By setting *shiftreg* high and clocking more clocks, the neighbours of the trigger channel will be available.

Be setting *shiftreg* low and giving another clock of *gck/gckb*, the next channel with a trigger will be available.

All channels with triggers are read out when the *vo* goes low. If the chip shall be reset before all channels are read out, apply the *res/resb* signal.

These signals have a fixed level:

|                                         | vi (chip 0)<br>vib (chip 0) | connect to VSS (logic low)<br>connect to VDD (logic high) |  |  |  |  |  |  |  |  |  |  |

|-----------------------------------------|-----------------------------|-----------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|

| •                                       |                             |                                                           |  |  |  |  |  |  |  |  |  |  |

|                                         |                             |                                                           |  |  |  |  |  |  |  |  |  |  |

|                                         |                             |                                                           |  |  |  |  |  |  |  |  |  |  |

|                                         |                             |                                                           |  |  |  |  |  |  |  |  |  |  |

|                                         | <mark>9</mark><br>I         | - 5,9<br>m.c. ''''time'' 2012 3456769121                  |  |  |  |  |  |  |  |  |  |  |

| •                                       | nl                          |                                                           |  |  |  |  |  |  |  |  |  |  |

| •                                       | . jn 124                    |                                                           |  |  |  |  |  |  |  |  |  |  |

| ທ                                       | , jn 10,0 <u>ь</u>          |                                                           |  |  |  |  |  |  |  |  |  |  |

|                                         | . yi                        |                                                           |  |  |  |  |  |  |  |  |  |  |

| TUPUI                                   | shiftreg                    |                                                           |  |  |  |  |  |  |  |  |  |  |

| 4                                       | . gck                       |                                                           |  |  |  |  |  |  |  |  |  |  |

| •                                       | . sh                        |                                                           |  |  |  |  |  |  |  |  |  |  |

|                                         | . гез<br>. рН               |                                                           |  |  |  |  |  |  |  |  |  |  |

|                                         | . pm <u> </u>               |                                                           |  |  |  |  |  |  |  |  |  |  |

|                                         | , mgo and <u>ta</u>         |                                                           |  |  |  |  |  |  |  |  |  |  |

| •                                       | <br>outp_u                  | ( 1 ) ( 8 ) ( ) (124 ) (123 ) (122 ) (121 )               |  |  |  |  |  |  |  |  |  |  |

| ഗ`<br>⊢.                                | outp_d                      | (1) (2) (3) (4) (125) (126) (127)                         |  |  |  |  |  |  |  |  |  |  |

| 0 T T T T T T T T T T T T T T T T T T T | addr 10:151                 | X 1 X 124                                                 |  |  |  |  |  |  |  |  |  |  |

| ۵.                                      |                             | <u> </u>                                                  |  |  |  |  |  |  |  |  |  |  |

|                                         | shiilou <u>tiu</u>          |                                                           |  |  |  |  |  |  |  |  |  |  |

|                                         | shifilou <u>tid</u>         |                                                           |  |  |  |  |  |  |  |  |  |  |

|                                         |                             |                                                           |  |  |  |  |  |  |  |  |  |  |

Figure 7: Sparse readout with neighbour channels

- a) Physics events happen almost simultaneously in channel 1 and 124. Since the signal is larger than the threshold, a trigger (mgo, ta/tb) is generated. The fast shaper for the trigger logic has a shaping time of 50ns, which means that dependent of the signal amplitude and the threshold, the trigger can be delayed up to 50ns.

- b) The disable\_late\_trigger *dlt* is applied. This will discard all triggers after this moment.

- c) Another physics event happen some time later in channel 100. No trigger is given because *dlt* is high.

- d) After 500ns, the sample-and-hold signal *sh/shb* goes high. The signal in channel 1 and 124 has reached the peak and are held.

- e) The *gck/gckb* clocks once. Since veto in *vi* from the previous chip in the chain is high, no action is taken.

- f) The gck/gckb clocks once with shiftreg = low. Veto in vi is low, and the first channel with a hit is enabled at the output together with its address.

- g) The gck/gckb clocks once with shiftreg = high. The analogue values of the two next neighbour channels of the hit channel are read out on the outp\_u/outm\_u and outp\_d/outm\_d lines.

- h) Same as g)

- i) Same as g)

- j) The *gck/gckb* clocks with *shiftreg* = low. The next channel with a hit is enabled at the output together with its address.

- k) Same as g)

- l) Same as g)

- m) Same as g)

- n) The chip is reset by setting *sh* and *dlt* low and by giving a short *res/resb* pulse.

The information in this catalogue is subject to change without prior notice.

Information given by Gamma Medica-Ideas is believed to be reliable. However, no responsibility is assumed for possible inaccuracies or omission.