# Status on the Development of FE & Readout Electronics for Large Silicon Trackers

Jean- François Genat LPNHE, Universités Paris 6 et 7/CNRS-IN2P3

Jacques David, Marc Dhellot, Jean François Genat, Frédéric Kapusta, Hervé Lebbolo, Thanh Hung Pham, François Rossel, Aurore Savoy- Navarro (LPNHE- Paris)

Erwin Deumens, Paul Malisse (EUROPRATICE, IMEC Leuwen)

Denis Fougeron, Richard Hermel (LAPP/CNRS-IN2P3, Annecy)

Forthcoming collaboration with CERN (Alessandro Marchioro et al, EUDET)

#### LCWS06, March 9-13th, Bangalore, India

# Outline

- Silicon strips detector context

- On-det ect or Elect ronics

- 180nm CMOS readout chip

- Tests results

- Design in 130 nm

- Next...

# Silicon strips detector context

#### Silicon strips detector numbers

- 4-10 10<sup>6</sup> Silicon strips 10 60 cm long

- Readout Pitch 50-100 μm DC or AC coupled

- Occupancy defined as % channels hit per BC: Outer barrel and end caps layers: <1% Inner barrel and end caps layers: <5%</li>

- ILC timing: 1 ms: bunch: 150-300ns / BC 200ms in between

#### **Detector data**

Pulse height: Cluster centroid to improve position resolution to O(μm)

Detector pulse sampling 5-10 samples 8-10 bit A/D (Wilkinson) stored in an analog buf f er

Time: Two scales:

- Coarse 150-300ns BCO tagging

- Fine nanosecond timing for coordinate along the strip and fine BCO tagging for some regions

Not to replace another detector layer or double sided detector, but give an estimation to a few cm

### **On-detector Electronics**

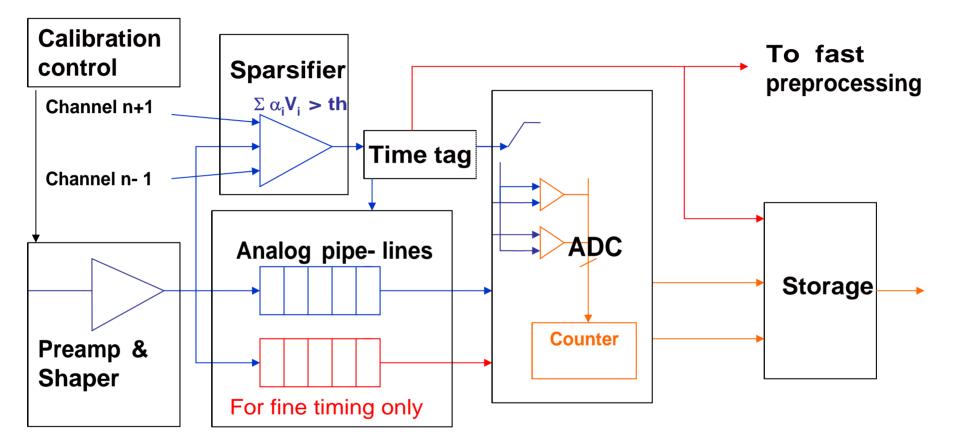

# **On-detector FE chip**

- Pulse sampling: 5-10 samples over 2 shaping times

- Buffering:

- Analog-Digital conversion

- Sparsification/calibration :

- Digital processing:

- o to samples over 2 shaping times

- 8-deep 2D analog buf f er (8\*5-10 samples cells) per channel

- Wilkinson optimum (SVX architecture)

- I nt egr at ed on det ect or FE chip

- Amplit ude and time estimation + charge cluster algorithm

- Power: 1/200 ILC duty cycle: FE Power cycling

#### Front-end architecture

Charge 1- 40 MIP, S/N~ 15- 20, Time resolutions: BC tagging, fine: ~ 2ns

Present technologies - Deep Sub-Micron CMOS Time-stamping fine time reso UMC 0.18  $\mu$ m, 0.13  $\mu$ m on some layers

Time-stamping on all layers fine time resolution on some layers

### Charge measurements Expected

- Preamp + Shaper Gain: 20mV/MIP over 1-30 MIP Noise: CMOS 180 nm: 280e- + 10.5e-/pF @ 3 μs

- Analog buffer 8-deep (cells of 5-10 100 fF caps)

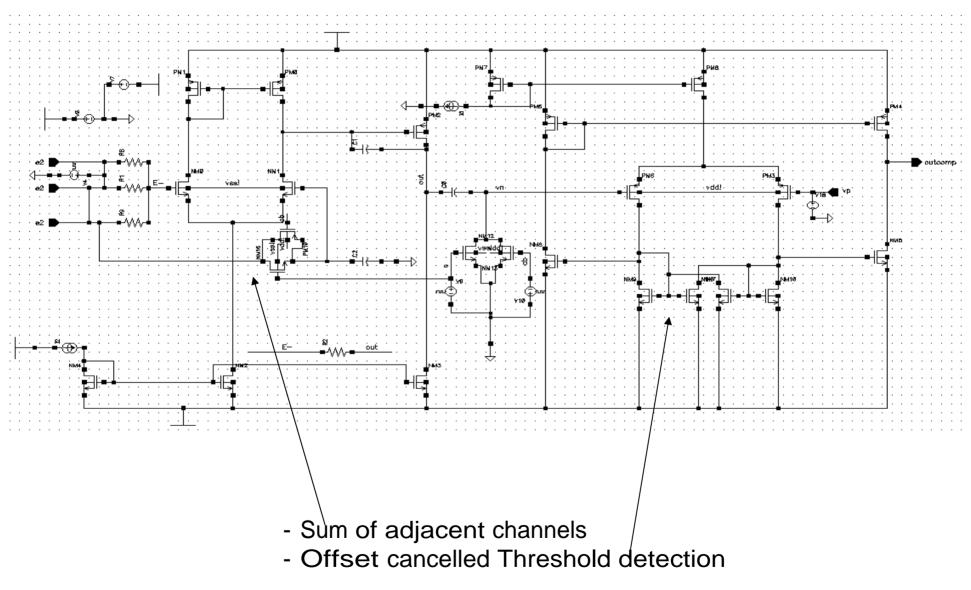

- Sparsifier Threshold an analog sum of 3 adjacent channels after pulse shaping

- ADC 10-12 bits Clocked at 96 MHz

0

0

0

0

0

Signal-Noise ratio The larger, the best 15-20?

### **Time measurements Expected**

Time stamping

Order of 30 to 50 ns Time-stamp the sparsifier out put at 4 \* BCO clock (12 MHz)

#### Fine time measurement

Order of 1 to 3 ns 32 \* BCO on chip interpolated clock sampling (PLL @96 MHz) Use digital processing over 5-10 digitized samples

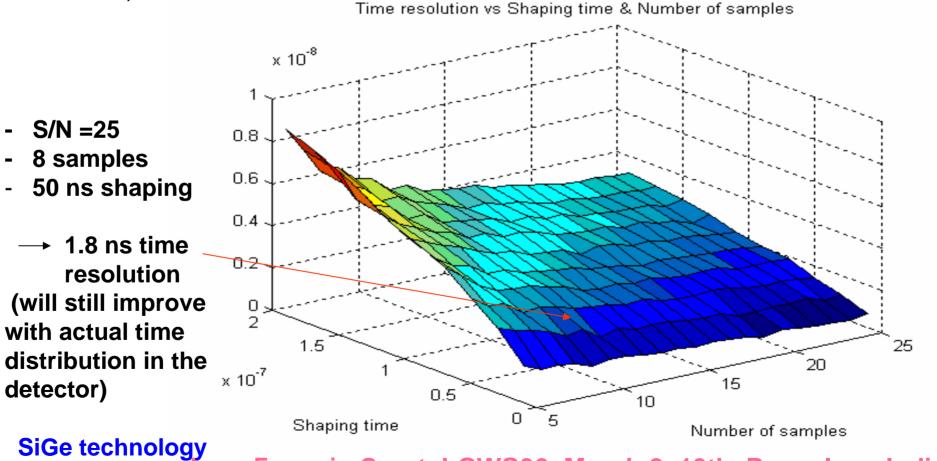

# Expected fine time resolution

Simulated (JFG) time resolution using a model of the whole electronics readout chain from preamplifier to the analog sampler (ideal A/D) using least square fit algorithm (William Cleland)

# **Overall Noise Contributions**

| Source                    | Value                   | Noise<br>180nm CMOS         |

|---------------------------|-------------------------|-----------------------------|

| Input stage<br>(measured) | g <sub>m</sub> =0.7mA/V | 615 e-<br>(measured)        |

| Detector leak             | 10 nA                   | 588 e-<br>(from literature) |

| Biasing resistor          | 10 MΩ                   | 423 e-<br>(thermal noise)   |

| Total                     |                         | 950 e-                      |

For eseen over all ENC contributions at 30 pF detector capacitance and 3  $\mu$ s shaping time:

- CMOS 180 nm: S/N ~ 20

- CMOS 130 under investigations

# CMOS 180nm Chip

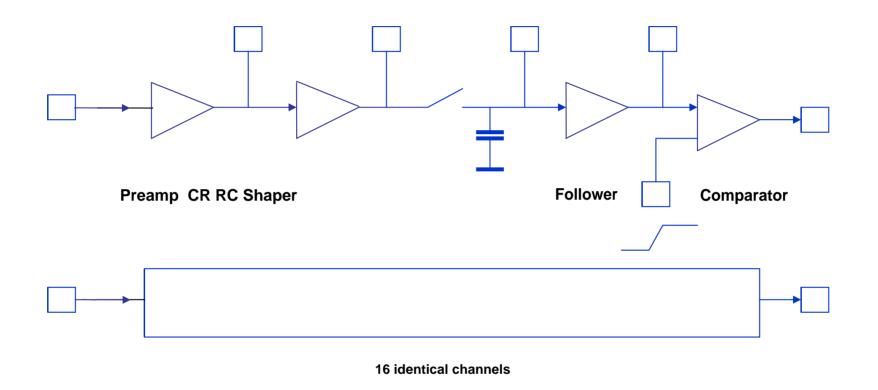

# Front-end test chip in CMOS 180nm

- Low noise amplification + pulse shaping

- Sample & hold

- Comparator

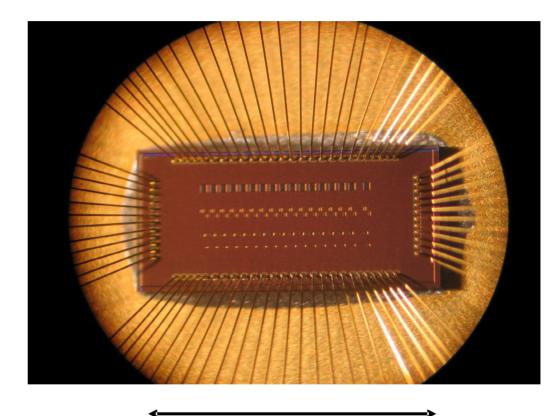

# Silicon

3mm

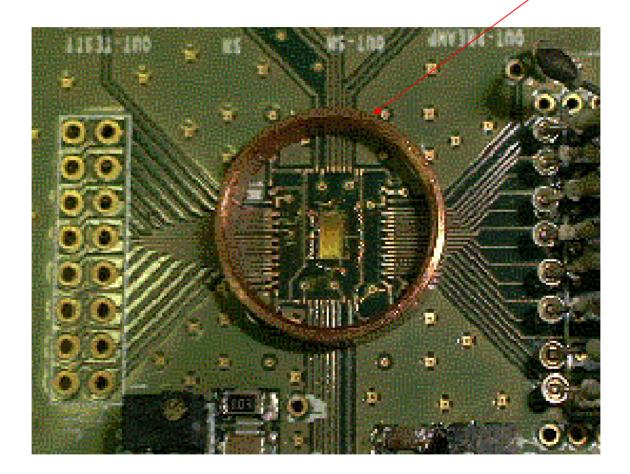

16 + 1 channel UMC 0.18 um chip (layout and pict ur e)

### **Tests Results**

Protection can

Chip wired-bonded on board

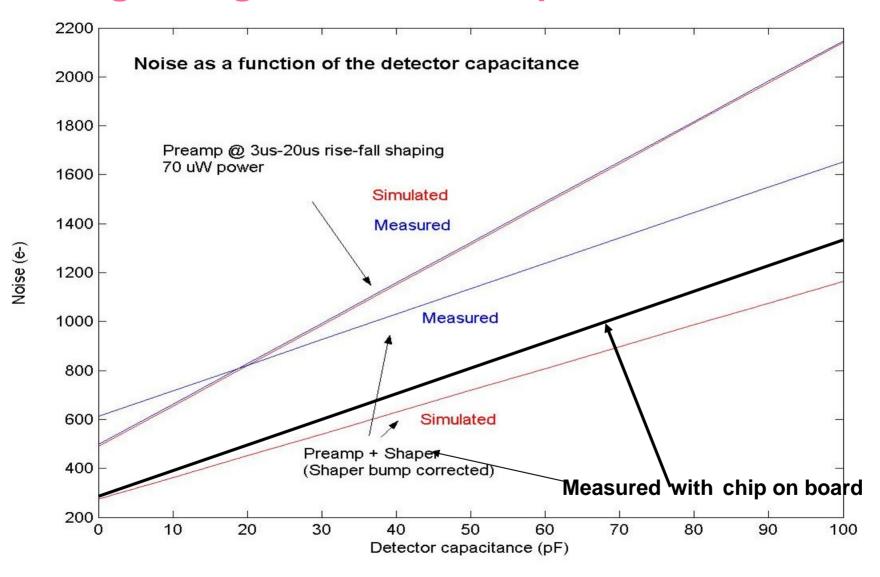

# Preamp tests results

12 chips tested.

One failure: On chip #8, comparator does not work.

Preamp:

- Gain: 8 mV/MIP OK

Linearity: +/-1.5% +/-0.5% expected

Transistor used as a resistor

non linear with voltage

- Dynamic range: 50 MIP 90 expected, but within specs

- Noise @ 70  $\mu$ W power, 3 $\mu$ s-20 $\mu$ s rise-fall times:

498 + 16.5 e-/pF 490 + 16.5 e-/pF expected OK

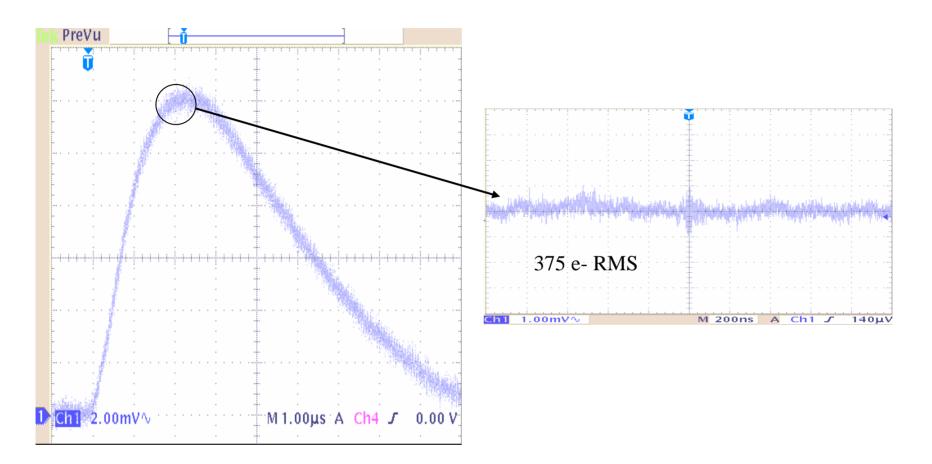

# Shaper Noise (wired-bonded on board)

375 e- input noise with chip-on-board wire-bonding (against 280 simulated)

#### Shaper tests summary

- Shaper: Peaking time:

- 2 6 µs tunable peaking time 1-10 targeted

- 6 MHz bump (~ 650 e- added noise)

- Not in simulations

- Shows up in simulations at 10 pF load (actual is 1 pF)

- Noise @ 3 us shaping time and  $70\mu$ W power:

- 375 + 10.4 e-/pF 274 + 8.9 e-/pF expected

#### Noise summary

#### good agreement with expected values

### Sample & Hold Comparator

Sample and hold:

OK

• Comparator:

Vt spreads of the order of 5 mV due to transistors sized too small

- Increase input transistors size from 10/0.5 to 200/10

- Increase Preamp + Shaper voltage gain from 8 to 25 mV/MIP

#### **Tests Conclusions**

#### 12 chips tested

The UMC CMOS 180nm process looks quite mature and reliable:

- Models OK

- Only one transistor failure

- Process spreads of a few %

Preamplifier: almost according to specs

Shaper: a bit more noise than expected but OK with simulations

Comparator: V<sub>t</sub> spreads understood

First proto delivered functional chips in a relatively new (in our field) DSM technology.

Encouraging results regarding CMOS DSM

# Next designs

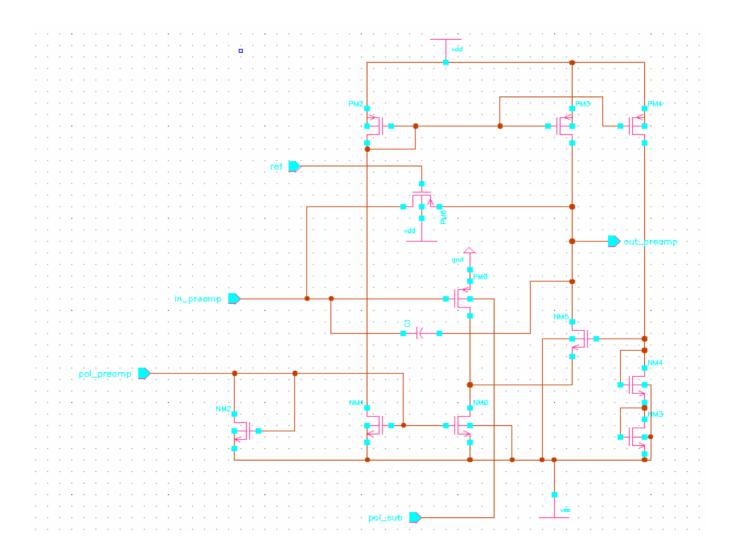

# Front-end in CMOS 130nm

Cooperation between LPNHE and LAPP Annecy and soon with CERN (A. Marchioro et al., EUDET)

Why 130nm ?

- VLSI

- Will be dominant in industry in the next few years

- Fast er

- Lower power

Drawbacks for low noise analog design

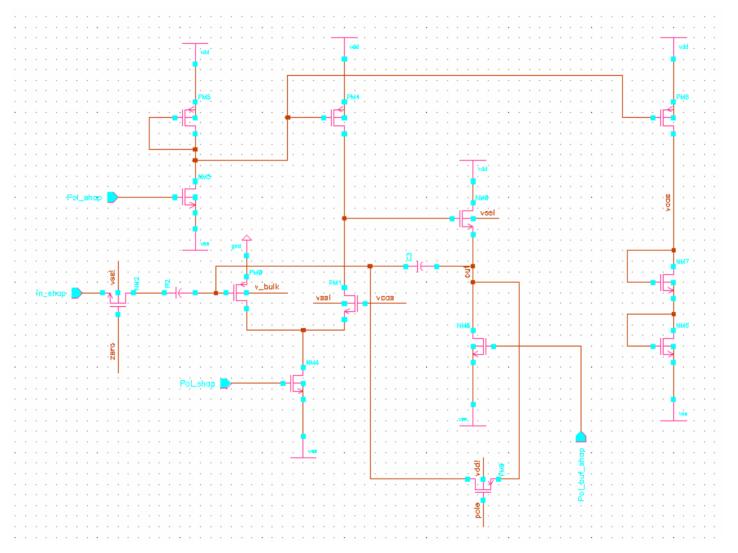

# Preamp in 130nm

# Shaper in 130nm

# 130nm Sparsifier

# 130nm plans

130 nm technology available end 2005 from Europractice

- Submit a 4 channel version end April 2006 including:

- Preamp + Shaper

- Sampling and analog pipe-line

- ADC

- Power cycling

Then, depending on tests

Submit a 128 channel version end 2006 including digital

# Front-End Digital in 130nm

- Chip control

- Buffer memory

- Processing for

- Calibrations

- Amplitude and time least squares estimation, centroids

#### Tools

- Digital libraries in 130nm CMOS available

- Synt hesis f r om VHDL/ Verilog

- SRAM memory

- PLLs

# Conclusions

- CMOS 180nm chip t est ed, ver y encour aging r esult s

- CMOS 130nm under way, include:

Preamps + Shapers Analog pipe-lines Sparsifiers ADC Power cycling

Submission end April 2006

- 180 and 130nm chips beam t est s scheduled (DESY, CERN)

- Plans f or 128 channels

This document was created with Win2PDF available at <a href="http://www.win2pdf.com">http://www.win2pdf.com</a>. The unregistered version of Win2PDF is for evaluation or non-commercial use only.