### **Electronics Ideas from Poland**

#### Marcin Ziembicki, Andrzej Rychter

Warsaw University of Technology

Workshop on Neutrino Near Detectors based on gas TPCs

## Introduction – who are we?

- Small group at the Warsaw University of Technology, specializing in nuclear & medical electronics.

- Currently involved in:

- R&D for Hyper-K and nuPRISM (electronics)

- T2K (SMRD, were involved in MPPC QA)

- COMPASS (various projects, most finished)

T2K

COMPASS

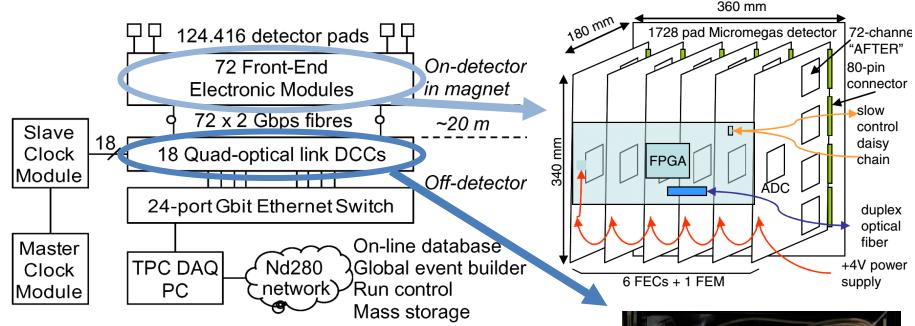

# TPC readout architecture (now)

- 3 TPC chambers × 24 micromegas modules

- 72 modules × 1726 pads = 124 416 channels

- 50 MHz SCA (AFTER) + 20 MHz/12 bits ADC

- Total data bandwidth 144 Gbps (FEM $\rightarrow$ DCC)

Architecture and Implementation of the Front-End Electronics of the Time Projection Chambers in the T2K Experiment P. Baron, et al.

Crate with DCC modules

# Back-end electronics – DCC

- 18 × Xilinx ML507 development boards with extensions

- Virtex 5 FPGA with embedded processor not recommended for use in new designs

- 256 Mbyte DDR2 SODIMM memory

- Gigabit Ethernet

- 6 RocketIO transceivers available

+ 2 in loopback mode

- Mezzanine card

- 3 Fiber Connectors connected to RocketIO transceivers

- Reference clock received via RJ45 cable, then it is fed to a clock conditioner (TI LMK03200) and finally conveyed to the ML507 via Coax.

- Single DDC performs aggregation from four FEMs

- One DCC crate holds 6 ML507 DCCs

- Each crate reads 24 detector modules

- Total number of crates for TPC = 3

Xilinx ML507 with extensions

Custom-made crate populated with six DCCs

# New DCC design for HTPC

- 4 HTPC  $\rightarrow \sim 70$  MicroMegas  $\rightarrow 1.3 \times 10^5$  channels

- 70 new Front-Ends and DCC optical channels needed

WUT proposal:

- Custom made VME DCC boards with Virtex UltraScale FPGA

- 20 nm architecture

- 45% lower power

- 36-120 transceivers per FPGA

- Max. Transceiver Speed 30.5 Gb/s

- VCXO and fractional PLL integration reduces clocking component cost

- 8-16 optical ports per VME card

- One VME crate for 4 TPC modules needed

- Either single board or carrier + mezzanine topology for easier serviceability