## **CMOS** directions in industry

#### Ernesto PEREA

#### ST Microelectronics

12th Workshop on Electronics for LHC and futute Experiments 25-29 September 2006, Valencia, Spain

#### **SUMMARY**

- ☐ Moore's-Law scaling impact on digital and analog circuits

- ☐ Regular reconfigurable structures (Networks on Chip, Multi-core Architectures, and Sampled Analog and RF circuits.

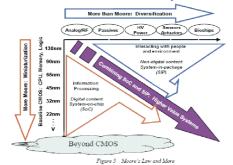

- ☐ More than Moore and 3D System Integration

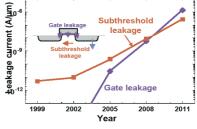

- ☐ Fundamental physical limiting effects (oxide tunneling, finite subthreshold slope, etc)

- ☐ New CMOS structures (new dielectric materials, band-gap engineering

- ☐ Statistical nature of parameter variabilities

- $lue{}$  Device architectures beyond 45nm (new metal-dielectrics gate stacks, stressed-strained channels, etc.

- $\hfill \square$  New tightly-coupled system-architecture-circuit-device design.

- Conclusion: Where is all this going?: The Process, Circuit, Architecture and System Design, and Manufacturing unique synergies and new innovative Cooperation-Competition industrial schemes.

#### **Point Contact Semiconductor Amplifier**

By Bardeen and Brattain, Dec. 16, 1947

#### 1956 Nobel Prize for Transistor **Invention at AT&T Bell Labs**

W. Brattain W. Shockley

#### Texas Instrument, 1st IC in 1958

Jack Kilby (Nov. 8, 1923- June 7, 2005) 2000 Nobel 1Tr (Germanium), 1C, 3R, Oscillator, 0.04 inch X 0.06 inch.

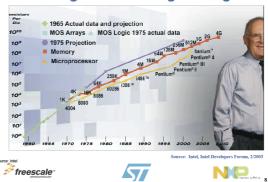

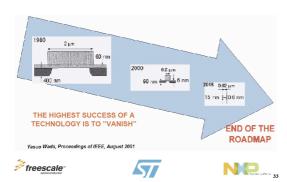

Scaling: Moore's-Law scaling impact on digital and analog circuits

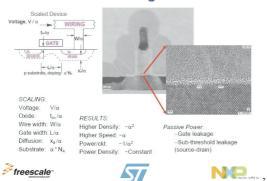

#### **CMOS Scaling Rules**

#### **SOC Integration: Scaling and Digital**

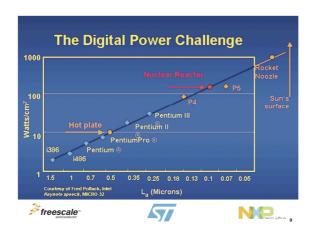

Drain and Gate increase in leakage currents

Reasons:Vdd decrease, Q nodes decrease, higher clock speeds.

- □ Signal Integrity, ElectroMagnetic Coupling and RF (SI/EMC/RF) solutions.

- □ Single and Multiple Event Upsets protections at architectural, circuit and device levels.

- ☐ Single event latch up.

- ☐ Hardened libraries (process and design levels).

- ☐ Fail safe architectures.

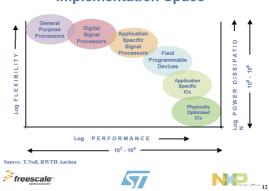

#### **Implementation Space**

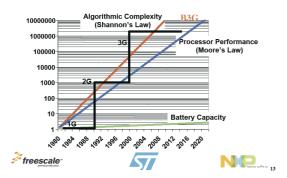

#### The Algorithmic Driving Force

Shannon asks for more than Moore can deliver...

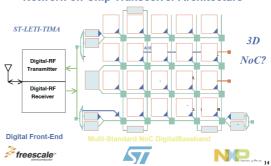

#### Reconfigurable **Globally Asynchronous-Locally Synchronous Network-on-Chip Transceiver Architecture**

#### **Key Processing Elements (PE's)** Required

#### ☐ Multistandard operation will require:

- FIR FiltersFFTs, IFFTs

- Viterbi and Turbo Decoders Rakes

- Synchronizer Blocks

### ☐ These parametrable blocks can be arranged in a

programmable NoC architecture:

- Array of heterogeneous processing elements

Programmable / parameterizable PEs (reconfigurable logic)

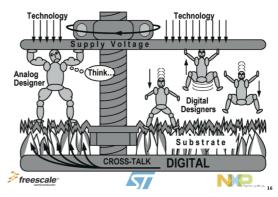

#### **Analog and Digital Scaling Challenges**

#### Panic...

# **Good Digital Neighbors...**

#### □Digital Compensation can be included almost for free:

...But it's nice to have

- -Account for Analog Imperfections through Digital Compensation (Linearity, Offsets, etc)

- -Digital self-calibration and dynamic element matching can be used at small feature size and low voltage.

#### **Analog Systems Considerations/Trends**

- Discrete time techniques will work better in scaled submicron CMOS

- > Switched-capacitor (SC) techniques, Bucket-Brigade, CCD's, etc.

- > Switches usually need complementary devices (V<sub>DD</sub> > V<sub>TN</sub> + V<sub>TP</sub>)

- ➤ For analog: lower V<sub>T</sub> typically offer:

- ✓ Faster switches

✓ Better amplifier input range

- ☐ Dynamically adjust supply and threshold design parameters to center the design in the presence of process variations!

- ☐ Digital Compensation can be included almost for free:

- Account for Analog Imperfections through Digital Compensation (Linearity, Offsets, etc)

- (Linearity, Offsets, etc)

➤ Digital self-calibration and dynamic element matching can be used at small feature size and low voltage.

□ Auto-ranging, Self-Calibration, Self-Test, Active Linearization, Reconfigurability allowing a different performance/cost tradeofs.

➤ These functions will have an impact on the Silicon cost, largely compensated by the Total Cost Reduction induced.

#### **Continuous Time versus Discrete Time and Scaling**

#### □ Discrete time techniques will work better in scaled submicron CMOS

- Switched-capacitor (SC) techniques, Bucket-Brigade, CCD's, etc.

- Switches usually need complementary devices  $(V_{DD} > V_{TN} + V_{TP})$

- For analog: lower V<sub>T</sub> typically offer:

- Faster switches

- Better amplifier input range

#### **Reconfigurable Front-End Radios**

- ☐ The concept of Integrated Reconfigurable Radios (SW Defined Radios = SDR) has been around for many years, but it regains interest for mobile terminals now because advances in silicon technologies make it possible.

- ☐ The reason for this regain of interest is also the expectation that a unique radio architecture, reconfigurable by SW to different standards will add flexibility and strongly reduce costs, by simplifying board development, calibration, and BOM, reducing the total cost seen by the phone manufacturer.

#### A full Mobile System-on-Chip:

- Full HW/SW integration of

Communication + Application + Intelligence

- ☐ Intelligence should include:

- For digital functions:

- Fine-grain integrated power management and control, including all available techniques at all levels (from SW to partitioning, design and process). Also Reconfigurability for standards.

Design for Test, Self-Test, Fault observability, detection and correction.

- For Front-End (RF and ABB) functions:

- о и гольства (кт- апо дор.) пилатотя:

Auto-ranging, Self-Calibration, Self-Test, Active Linearization, Reconfigurability allowing a different performance/cost tradeofs.

#### ☐ <u>HW/SW overhead:</u>

- These functions will have an impact on the Silicon cost, largely compensated by the Total Cost Reduction induced.

- ...But, What about the Reconfigurable Digital Baseband?

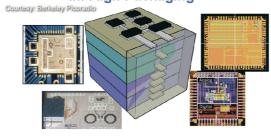

#### More Than Moore's Law (ITRS2005)

freescale

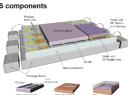

#### **SOC + SIP Integration**

- ☐ Module integration offers the possibility to integrate different technologies together

- SOC Transceiver

- · GaAs or Si (Power Amplifier)

- · Passive components

- RFMEMS components

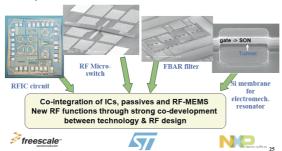

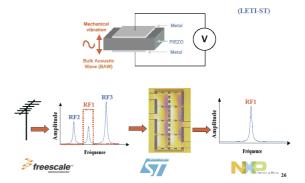

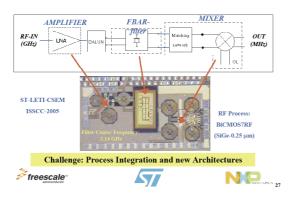

#### **RFMEMS Integration**

- □ Allows System on Chip (SoC) approach

□ Opens the door to Innovative RF Front-End Architectures

#### **BAW Filter Operating principle**

#### **RF Front-End FBAR integration**

#### The Old Super-Regenerative Receiver

- Invented by Armstrong in

- Possible radio operation above device f<sub>T</sub>, allowing:

- -Subthreshold biasing and/or -High carrier frequency, increasing integration

- •Modern devices/MEMS can solve traditional problems with architecture:

- freescale

1940s - Super-regenerative  $f_c$ = 500MHz (above  $f_T$ )

2 active devices high quality passives hand tuning required

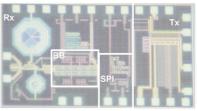

#### Next Generation: (1x1.9)mm<sup>2</sup> Rx/Tx

- Above IC Components (inductors, crystals, capacitors)

- Full Digital control of analog/RF blocks

-Rx Osc Frequency: 3.15MHz x 500kHz

-BB Filter BW/Gain

-Tx Tank Frequency

# Dealing with Mixed-Everything through Packaging

#### **SIP for Optimum Technology Mix**

- □ Close to the antenna, advanced SiGe:C Bipolars will continue to play an important role for very low NF @ Low-Power, as well as for RF Power Amplification @ High Efficiency, for battery life.

- ☐ Medium Voltage / Power functions such as Energy Management and Audio will continue to be handled by adapted MOS/Bip Technologies for reliability and lowest cost. High density/quality capacitors will be key differenciators.

- ☐ This Technology Mix will be possible by SIP techniques also allowing Hi-Q Passives and MEMS Integration.

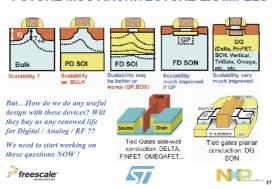

#### **The Ultimate Nanometer MOS**

#### **WAYS BACK TO HEALTHY SCALING**

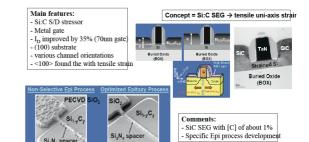

#### **TECHNOLOGY BOOSTERS**

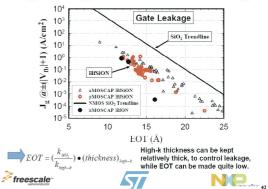

- ☐ H- K DIELECTRICS (Improves MOS behavior)

- ☐ METAL GATES (Improves Ion/Ioff)

- ☐ STRAINED Si, SiGe and Ge (Improves Mobility)

- □ DEVICE STRUCTURE (Reduces loff)

- ☐ SOI / SON (Improves speed, Reduces loff)

- ☐ MULTIPLE GATES (Improves MOS, Reduces loff)

- ☐ BALLISTIC TRANSPORT (Improves Speed)

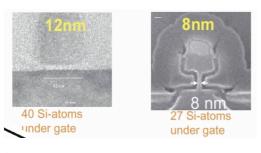

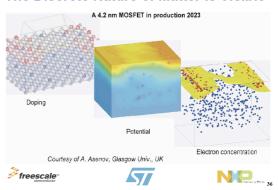

#### **REAL NANO- MOSFETs**

#### The Discrete Nature of Matter is Visible

#### **FUTURE MOS ARCHITECTURE EXAMPLES**

# ITRS Roadmap 2005 Edition Mobility booster -Process induced strain - Crystal orientation - sSOI - Dual channel fourcest systems 30 freescale

#### **CMOS Worlwide Trends**

**Mobility enhancement** Orientation for pMOS

Strain Tensile strain for nMOS Compressive strain for pMOS

Dual MG + Higk-K for reduced gate tunneling

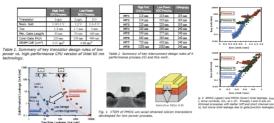

#### IEDM-2005 Trends

#### **□**Standard CMOS platform

- Main 65nm and 45nm general plaform stay in bulk conv.

#### **□** Strained Silicon

- Intensively full strain sources re-use

- NMOS= SMT+high tensile stress

- PMOS= eSiGe+high compressive stress

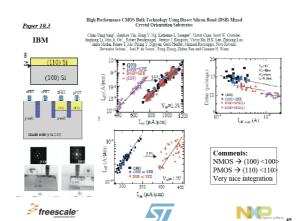

- Very interesting IBM paper using hybrid subtsrate types (bulk)

#### **Strained-Silicon Performance Enhancement**

- 1. Strained Si can produce an increase in Ion

- without a degradation in I<sub>off</sub>.

2. Stress-induced defects can occur in the silicon if the stress is not applied properly.

### Impact of High-k on Gate-Dielectric Leakage

#### A 65nm Ultra Low Power Logic Platform Technology using **Uni-axial Strained Silicon Transistors Intel Corporation**

#### Paper 3.4

#### **Design of High Performance PFETs with** Strained Si Channel and Laser Anneal,

IBM System & Technology Group, 1Chartered Semiconductor Manufacturing, Ltd, 2Infineon Technologies AG, 3Samsung electronics Co., Ltd, 4Toshiba America Electronic Components, Inc.,

#### Paper 20.3

#### Thin Body Silicon-on-Insulator N-MOSFET with Si:C S/D Regions for Performance Enhancement

Singapore University

Four-once by the gas 46

#### Source/Drain Germanium Condensation for P-Channel Strained Ultra-Thin Body Transistors

Rational University of Singapore

This paper reports a novel technique to fabricate unlaxial compressive

strained P-channel transistors with Silicon-Germanium (SiGe) source and

drain (S/D) stressors.

The process involves local Ge condensation of a selectively grown SiGe

region, thus driving Ge into and enriching the Ge concentration in the

source and drain regions adjacent to the transistor channel.

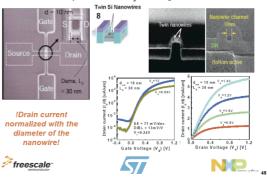

# High Performance 5nm radius Twin Silicon Nanowire MOSFET(TSNWFET): Fabrication on Bulk Si Wafer, Characteristics, and Reliability Samsung Electronics Co.

Paper 36.7

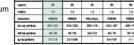

Vth-tunable CMIS Platform with High-k gate Dielectrics and Variability Effect

T. Hayashi, M. Mizutani, M. Inoue, J. Yugami, J. Tsuchimoto, M. Anma, S. Komori, K. Tsukamoto, Y. Tsuka moto, K. Nii, Y. Nishida, H. Sayama, T. Yarnashita, H. Oda, T. Eimori, and Y. Ohji

Renesas

Remeins Technology Corp., Wafer Process Engineering Development Dept.

#### F implant for Vth correction (poly/ HfSiON!)

615/221 μA/μm @ 20pA/μm (V<sub>dd</sub>= 1.2V)

#### 30.1 High Performance Multi-Gate pMOSFETs using Uniaxially-Strained SGOI Channels

MIRAI-ASET+, MIRAI-AIST++, Toshiba Ceramics\*

#### Variability matters!

- ☐ Identify main sources

- □ SRAM test structures

- □ Analog test structures (Diff. Pair matching, Switches, etc ..+ passives...)

- ☐ Digital basic cells (RO's, Adders, Latches, etc)

- ☐ Environment measurements (Vdd noise, couplings, etc)

- ☐ Wiring RC delay characterization

- ☐ Using variability information

- Exhaustive Data Mining approach

- Variability modelingYield models

- ☐ Impact on Circuit / Device / Process design choices

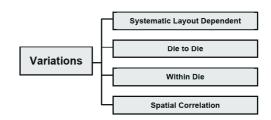

#### **Categorizing Variations**

#### Systematic and Random Device Variations

| Parameter  Channel dopant concentration Nch | Random                                       |  | Systematic                                                                  |

|---------------------------------------------|----------------------------------------------|--|-----------------------------------------------------------------------------|

|                                             | Affects Δvth                                 |  | Non-uniformity in the<br>process dopant<br>implantation dosage<br>diffusion |

| Gate Oxide thickness<br>Tox                 | Gate- dielectric-channel interface roughness |  | Non-uniformity in the process oxide growth                                  |

| Gate length L                               | Line edge roughness                          |  | Lithography<br>Proximity effects<br>Resist development<br>etching, etc      |

#### The Importance of Variability

#### ☐ Absolute amount of variability for a particular design

- Often captured in design corners

- Determines power penalty for guaranteeing performance

- Limits benefits of technology scaling

- Avoid pessimistic Over-Design

#### ■ Nature of variability

- Within-die (WID), Die-to-die (D2D), Wafer-to-wafer (W2W), Fab-2-Fab

- Spatial vs. Temporal (incl. intermittent)

- Systematic vs. random

- Correlated vs. uncorrelated

#### **Digital Systems** Considerations/Trends

- □ Process and design interaction: DFM

▷ Physical design impacts yield

▷ Power management and Analog/RF integration require more extensive modeling

▷ Distributed test and debug functions

- ☐ Fine-grain integrated power management and control necessary, including all available techniques at all levels (from SW to partitioning, design and process). not all transistors need min Lg or Ltv.

- need min Lg or LVt.

| Scaling: Intrinsic chip speed grows faster than I/O bandwith:

| Data will be trapped on-chip.

| Layout/Routing techniques will outperform Low-K approaches.

| Multi-Core Trend: Simpler cores, smaller clock zones, shorter wires, lower latencies: Network-on-Chip, higher IP-reuse, higher parallelism/multi-threading, smaller cores/redundancy: improved yields, self-repair.

| Needed: more design for testability, better yield models, higher.

- □ Needed: more design for testability, better yield models, higher I/O bandwidth, better system-level power reduction.

#### Conclusion

Where is all this going?: Process, Circuit, Architecture and System Design, and Manufacturing unique synergies and new innovative Cooperation-Competition industrial schemes.

#### ...Evolution of Integration...

- > SSI

- > MSI

- > LSI

- > VLSI

- > SoC (System on a Chip)

- > NoC (Network on a Chip)

- > LoC (Laboratory on a Chip)

- > CiH (Chip in a Human)

- > ...HiC ?... maybe not...

#### There is plenty of room at the bottom

(Richard Feynman, 1960)

- ☐ "Can we write the Encyclopedia Brittanica on the head of a pin?"

- ☐ "Can we write all books into the volume of a pin?" (3D)

- ☐ "How do we writ it?"

- ☐ How do we read it?"

- ☐ "Can we see atoms?"

- ☐ "Can we move and manipulate individual atoms?"

- ☐ "Can we build machines at the atomic level?"

- $\hfill \square$  "Can we synthesize substances with physics, not chemistry?"

- ☐ "Can we build an atomic-scale computer?"

#### The Importance of Variability

- ☐ Absolute amount of variability for a particular design

- Often captured in design corners

- Determines power penalty for guaranteeing performance

- Limits benefits of technology scaling

- Avoid pessimistic Over-Design

#### ■ Nature of variability

- Within-die (WID), Die-to-die (D2D), Wafer-to-wafer (W2W), Fab-2-Fab

- Spatial vs. Temporal (incl. intermittent)

- Systematic vs. random

- Correlated vs. uncorrelated

## Considerations/Trends □ Process and design interaction: DFM ▷ Physical design impacts yield ▷ Power management and Analog/RF integration require more extensive modelling ▷ Distributed test and debug functions

**Digital Systems**

- Distributed test and debug functions

Fine-grain integrated power management and control necessary, including all available techniques at all levels (from SW to partitioning, design and process). not all transistors need min Lg or Ltv.

Scaling: Intrinsic chip speed grows faster than I/O bandwith: Data will be trapped on-chip.

Layout/Routing techniques will outperform Low-K approaches.

Multi-Core Trend: Simpler cores, smaller clock zones, shorter wires, lower latencies: Network-on-Chip, higher IP-reuse, higher parallelism/multi-threading, smaller cores/redundancy: improved yields, self-repair.

Needed: more design for testability, better yield models, higher.

- Needed: more design for testability, better yield models, higher I/O bandwidth, better system-level power reduction.

#### Conclusion

Where is all this going?: Process, Circuit, Architecture and System Design, and Manufacturing unique synergies and new innovative Cooperation-Competition industrial schemes.

## ... Evolution of Integration...

- > SSI

- > MSI

- > LSI

- > VLSI

- > SoC (System on a Chip)

- > NoC (Network on a Chip)

- > LoC (Laboratory on a Chip)

- > CiH (Chip in a Human) > ...HiC ?... maybe not...

- freescale

#### There is plenty of room at the bottom

- ☐ "Can we write the Encyclopedia Brittanica on the head of a pin?"

- ☐ "Can we write all books into the volume of a pin?" (3D)

- ☐ "How do we writ it?"

- ☐ How do we read it?'

- ☐ "Can we see atoms?"

- ☐ "Can we move and manipulate individual atoms?"

- ☐ "Can we build machines at the atomic level?"

- ☐ "Can we synthesize substances with physics, not chemistry?" ☐ "Can we build an atomic-scale computer?"