# The ATLAS Barrel Level-1 Muon Trigger Calibration

G.Ciapetti, F.Pastore, E.Petrolo, S.Rosati, F.Spila, R.Vari, S.Veneziano, L.Zanello <sup>a</sup>

<sup>a</sup> INFN Roma, P.le A. Moro 2, 00185 Roma, Italy

### Riccardo. Vari@roma1.infn.it

### Abstract

The ATLAS experiment uses a system of three concentric Resistive Plate Chambers detectors layers for the level-1 muon trigger in the air-core barrel toroid region. The trigger classifies muons within different programmable transverse momentum ranges, and tags the identified tracks with the corresponding bunch crossing number. The algorithm looks for hit coincidences within different detector layers inside the programmed geometrical road which defines the transverse momentum cut. The on-detector electronics providing the trigger and detector readout functionalities collects input signals coming from the RPC front-end. Because of the different time-of-flights and cables and optical fibres lengths, signals have to be adjusted in time in order to be correctly aligned before being processed. Programmable delay logics are provided in the trigger and readout system to allow for time adjustment, for hit signals as well as for LHC Timing, Trigger and Control signals. The trigger calibration provides the set of numbers used during electronics initialization for correctly aligning signals inside the trigger and readout system. The functionality scheme and the algorithm of the calibration are presented.

### I. INTRODUCTION

The ATLAS level-1 muon trigger in the barrel region selects and classifies muon candidates with respect of their transverse momentum, and associates their tracks with the correct bunch-crossing number. The muon spectrometer in the barrel region is equipped with a system of Multi Drift Tube detectors for precise particle track measurement, and the Resistive Plate Chamber detectors for the trigger functionality and for the second coordinate measurement. The trigger system processes the full granularity data of about 350.000 trigger chambers channels, reducing the raw rate of 1 GHz proton-proton interactions and 40 MHz beam-beam bunch crossings to 75 kHz, within a maximum total latency inclusive of cable delays of 2 µs.

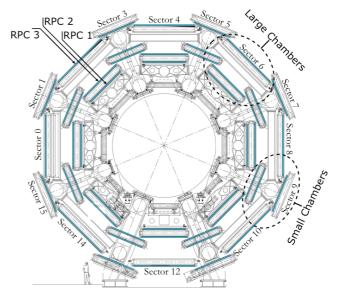

One RPC detector is composed of two gas gaps, each one being read-out by two orthogonal planes of copper strips, so that each detector has two planes of strips in the bending (eta) view, and two in the non-bending (phi) view. The full barrel system is organised in sixteen radial sectors, each one hosting three RPC detectors, two of them mounted in a middle station inside the air-core toroid, and one in an outer station. Thus a three concentric detectors system is formed, providing six read-out layers per each view (four in the middle station and two in the outer station). Figure 1 shows the position of the RPC detectors on a radial section of the experiment.

The full experiment is divided in two half-parts, side A for positive eta values and side C for negative eta values, so that

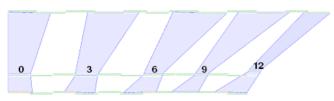

each ATLAS sector is so divided in two parts, belonging either to positive or negative eta values. One sector side is composed by three planes of RPC detectors (inner, middle-pivot and outer), each plane being formed normally by six or seven adjacent RPC detectors. One ATLAS sector is again longitudinally segmented, from a trigger point of view, in two trigger sectors, so that the global trigger system is structured in sixty-four trigger sectors. A trigger tower is composed by three half RPC detectors (inner, pivot and outer) belonging to the same trigger sector, so that there are six or seven trigger towers per each trigger sector.

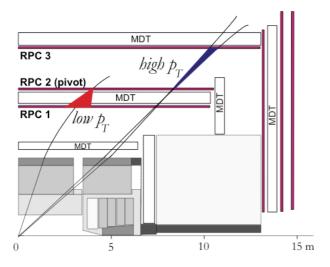

The muon trigger algorithm is performed in the bending and non-bending view separately, and is organised in a low-p<sub>T</sub> trigger (6 GeV/c transverse momentum cut) and a high-p<sub>T</sub> trigger (20 GeV/c). The trigger logic identifies muon candidates coming from the interaction vertex within a p<sub>T</sub> range, basing the algorithm on the expected track curvature, and on the hits coincidence within the geometrical roads. The middle RPC detector is used as the pivot plane, while the inner (low-p<sub>T</sub>) and outer (high-p<sub>T</sub>) RPCs are used as the confirm planes. If a hit is found in the pivot plane, then a confirm hit is searched on the confirm plane, within the desired geometrical road, that is a projection from the pivot layer on to the confirm layers. The road width determines the energy cut. Three different p<sub>T</sub> cut per each low and high-p<sub>T</sub> trigger can be simultaneously applied. In Figure 2 one quadrant axial section of the experiment is shown, with the trigger scheme illustrated. Figure 3 shows an exemplificative view of the trigger roads, for one trigger sector.

Figure 1: the ATLAS barrel region section, showing the three concentric RPC detectors position into the sixteen-sectors trigger chambers system.

Figure 2: the low- $p_T$  and high- $p_T$  trigger scheme, showing the central pivot detector (RPC2), the inner the low- $p_T$  confirm detector (RPC1) and the outer high- $p_T$  confirm detector (RPC3).

Figure 3: schematic view of the trigger roads projection for some trigger towers. The middle horizontal line represents the pivot plane, for one half barrel, equipped with six RPC detectors. The numbering represents the coincidence windows, two per each RPC.

#### II. TRIGGER SYSTEM ELECTRONICS

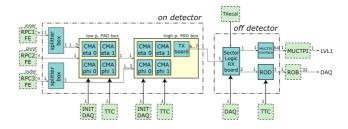

The barrel level-1 muon trigger system is divided in an ondetector and an off-detector part. The RPC detector front-end electronics resides in the detector itself, and is connected to the on-detector trigger electronics via flat cables. Each RPC has got two sets of 8-channels connectors, one per each strip layer, on both the bending eta and the non-bending phi sides. The on-detector electronics is made of splitter boxes and trigger processors boxes (also called PAD). Because of overlapping coincidence windows in the confirm RPC detector planes, signals coming from the inner and outer RPCs need to be sent to more than one trigger processor box. A splitter box, mounted near each PAD box, is used to split detector signals and to fan-out them to more than one trigger processor box. One PAD box is mounted on top of each half-RPC station (each half-RPC belongs to a distinct trigger sector). A trigger tower is composed by one low-p<sub>T</sub> PAD box mounted on top of one middle RPC station, reading-out the inner and the pivot RPC chambers, and one high-p<sub>T</sub> PAD box mounted on top of the outer station, reading-out the low-p<sub>T</sub> trigger result and the outer RPC chamber signals.

Each PAD box hosts four Coincidence Matrix ASICs, two per each view. One CMA contains both trigger and RPC readout logic, it processes signals coming from up to four detector layers, tags hit information to time bins of 3.125 ns (1/8 of a bunch crossing period), and tags events to the corresponding bunch crossing number. The ASIC has got a pipeline based architecture working at a clock speed of 320 MHz. The CMA trigger algorithm looks for hit coincidences

within up to four different RPC detector layers inside the programmed geometrical road. A 1/4, 2/4, 3/4 or 4/4 majority logic can be applied. The trigger logic is replicated three times inside one CMA, so that three different threshold cut can be simultaneously applied. Trigger and readout results coming out from the CMAs are collected together in the local PAD logic (which resides into a FPGA chip), which assembles event data and calculates the RoIs. Low-p<sub>T</sub> trigger and readout results are sent via flat cables to the high-p<sub>T</sub> trigger box, which applies the high-p<sub>T</sub> algorithm and sends results to the off-detector electronics via an optical fibre.

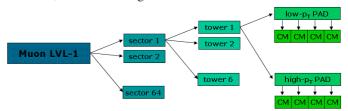

Six or seven optical fibres coming from one trigger sector go to one VME Sector-Logic/RX module, which elaborates the collected trigger and readout data, and sends readout and trigger data respectively to the ROD and to the MUCTPI. A schematic view of the full trigger slice is shown in Figure 4.

Figure 4: level-1 muon trigger slice, schematic view. The trigger algorithm is performed separately on eta and phi views, and then collected together in the PAD logic. Low- $p_T$  results is elaborated with the high- $p_T$  data in the high- $p_T$  trigger processor, and then sent to the off-detector electronics.

### III. TRIGGER ELECTRONICS CONFIGURATION

The on-detector electronics can be remotely initialised and controlled via a CANbus based system. Each PAD box hosts one CAN node to be used for receiving configuration commands and DCS commands (on detector board temperature sensors check, voltage control, etc.). Eight rack-mounted linux-based PCs, located in USA-15, run the initialization and DCS software. Each PC has got two PCI CAN interface cards each one with four CAN channels, each channel controlling one trigger sector. The total number of CAN nodes is 804 (one per each PAD).

One trigger processor box has got around 700 configuration parameters that are written/read during initialisation/control phases. The initialisation procedure can be performed either using one CAN write command per each parameter, operating with the user desired values from the PCs, or using a unique CAN command for the fast initialisation procedure, that uses an on-detector board locally-stored set of parameters. In fact the ELMB flash memory can store different sets of configuration parameters to be directly uploaded to the configurable PAD chips. The CAN fast initialisation command accesses the memory address storing the desired set of parameters, and start the local fast configuration procedure.

Table 1 shows the list of the configurable chips inside the trigger processor box. Since the Coincidence Matrix ASIC performs the trigger and readout algorithm, it store a large number of parameters, the most important being: input hit signal timing adjustment, trigger threshold settings, trigger

majority levels, trigger timing, trigger and readout channel masking, readout window settings, trigger and readout input and output dead-time settings, bunch-crossing and level-1 counters presets, etc. The PAD FPGA performs the PAD logic, and its main configuration parameters are: RoI settings, trigger and readout mode settings, test-pulse settings, bunch crossing and level-1 counters presets, testing settings, etc. The other chips that need to be initialised on the PAD boxes are: PRODE (delay/phase adjustment settings for the TTC signals), TTCrx (main control register need to be initialised) and the Optical Link (only on the high-p<sub>T</sub> PAD). Finally, the PAD and ELMB flash memories contain respectively the PAD firmware for the PAD logic and the ELMB firmware with the initialisation settings, and they can be both read/written via the CAN bus.

The off-detector Sector-Logic/RX board's configuration parameters (main controls, time adjustments, etc.) are initialised via the VME interface.

Table 1: on-detector trigger processor configuration parameters list.

| chip<br>name    | # of chips<br>per PAD | # configuration<br>parameter per<br>chip | parameters function               |

|-----------------|-----------------------|------------------------------------------|-----------------------------------|

| CMA             | 4                     | 159                                      | configuration registers           |

| PAD<br>FPGA     | 1                     | 19                                       | configuration registers           |

| PRODE           | 4                     | 4                                        | channels delay<br>settings        |

| TTCrx           | 1                     | 5                                        | configuration registers           |

| Optical<br>link | 1                     | 1                                        | configuration<br>register         |

| ELMB<br>flash   | 1                     | local memory                             | ELMB firmware configuration files |

| PAD<br>flash    | 1                     | local memory                             | PAD firmware                      |

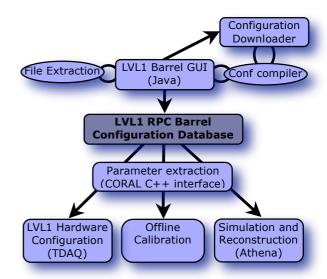

The barrel level-1 configuration system stores all the configuration parameters on a central configuration database, used as the reference point for all the online and offline software applications controlling and monitoring the hardware. The TDAQ software runs and controls data taking, and is in due for the hardware configuration (i.e. it handles the PC CAN interfaces and commands). The offline calibration software runs the calibration algorithm based on the detector data coming from the TDAQ and on the configuration used during data acquisition. The simulation and reconstruction software uses the acquired data and the configuration data for its calculations. The TDAO software, the calibration software, and the simulation and reconstruction software are interfaced with the database using a CORAL C++ based program, which extracts the configuration parameters from the database and passes them in the proper format to the software tools. From the configuration side, a Java based software will interface the database with the configuration procedure, generating a new set of parameters in the database each time a new configuration is created. It also interfaces the database with the program used to create the configuration file to be

downloaded in the PADs. The configuration scheme is shown in Figure 5.

Figure 5: The level-1 barrel muon configuration system.

#### IV. ELECTRONICS CALIBRATION

The barrel level-1 muon trigger calibration procedure is fundamental to assure good trigger efficiency, correct particle track reconstruction and bunch crossing identification. The calibration procedure can be logically separated in the trigger and in the readout part.

### A. Trigger calibration

From the trigger point of view, the request from the calibration systems is to align in time the hit signals within each trigger tower, between adjacent trigger towers belonging to the same trigger sector, and between different trigger sectors. In order to perform the correct trigger calibration procedure, all trigger system structural characteristics have to be taken into account:

- the difference in length of the cables connecting the RPC detectors front-end electronics to the PAD trigger processors, which causes different timing for the hit signals belonging to the same PAD;

- the length of the cables carrying the low-p<sub>T</sub> trigger output pattern signal from the low-p<sub>T</sub> PAD to the high-p<sub>T</sub> PAD, to be taken into account for the right time coincidence between the low-p<sub>T</sub> result and the outer RPC signals;

- the trigger algorithm processing time, which causes a delay for the signals passing through the PADs;

- the time of flight for muons passing from the low-p<sub>T</sub> RPC station to the high-p<sub>T</sub> RPC station in a trigger tower, to be considered for the proper signal time alignment;

- the different length of optical fibres going from ondetector to off-detector electronics, causing time misalignment between different trigger sectors.

In order to cope with all these different factors, a lot of configuration parameters can be used both for the on-detector and for the off-detector electronics. The on-detector trigger calibration parameters are the following:

- front-end signals input delay pipelines: signals can be delayed in groups of 16 RPC adjacent strips from 0 to 16 bunch crossing periods (400ns) in steps of 3ns, so that a time alignment can be possible within one trigger tower (within one RPC station and between inner low-p<sub>T</sub> and outer high-p<sub>T</sub> station);

- all the TTC signals (clock, trigger, resets) inside one PAD can be phase adjusted, in time steps of 1 ns, from 0 to 25 ns.

The off-detector trigger calibration parameters are:

- the sector logic input trigger signals can be shifted and aligned in steps of 1 bunch crossing period. This is used for timing alignment between different trigger towers (same or different trigger sector);

- all 8 inputs to the Sector Logic are aligned in phase with the 40 MHz clock (done on the PAD).

#### B. Readout Calibration

A very similar approach can be used for the calibration readout point of view. The requests for the readout calibration are: a proper trigger calibration, the event of interest selection with respect to the trigger input signal, the bunch crossing identification, event tagging with the correct event and bunch crossing numbers for all trigger towers. To achieve these requests the following it has to be taken into account:

- the level-1 signal latency;

- the length of the cables connecting the low-p<sub>T</sub> PAD readout output pattern to high-p<sub>T</sub> PAD readout inputs;

- the difference in length for the optical fibres going from on-detector to off-detector;

- the readout algorithm processing time.

The readout calibration on-detector parameters are:

- the readout window position: it can be shifted in time from 0 to 256 bunch crossing periods in steps of 25 ns with respect to the level-1 signal;

- the readout window width: it can be adjusted from 1 BC to 8 BCs;

- the bunch crossing and event counters presets: these internal counters can be preset to the desired value to be loaded when a TTC reset signal arrives;

- TTC signals delay: each TTC signal can be adjusted in time and shifted from 0 to 25 ns in steps of 1 ns.

There are no readout calibration off-detector parameters, since the signals going to the Sector Logic are already aligned in time with the 40 Mhz clock phase.

### C. Calibration Studies

Studies on the level-1 muon trigger calibration system have been carried out on the following CERN sites:

- muon test-beam (two trigger towers);

- BB5 cosmic ray RPC test stand (one trigger tower);

- ATLAS SX1 surface RPC test pulse system (one RPC station);

- ATLAS sector 13 during the commissioning phase (three trigger towers, two trigger sectors).

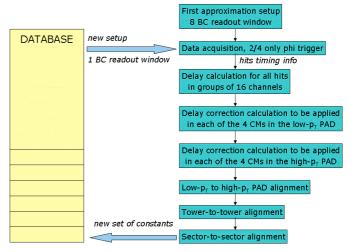

These studies have been fundamental to develop the final calibration procedure. The calibration procedure has been developed using a bottom-up approach, following the trigger structure, as shown in Figure 6.

Figure 6: bottom-up level-1 calibration approach scheme.

## D. Calibration Algorithm

The calibration algorithm first uses data acquired with a known set of parameters values (for example the default one). Timing info is then extracted from the acquired data, calculating the average time distribution for groups of sixteen channels. This calculation gives the information of the time shift between different groups of front-end channels, so that the delay to be applied can be identified. Alignment between CMs is done using the pivot plane as reference distribution, and aligning the others to this reference. The set of delay parameters can so be applied in all the CMAs of one low-p<sub>T</sub> PAD, and then on the corresponding high-p<sub>T</sub> one, so that the alignment between low and high-p<sub>T</sub> PADs can be performed. After the single trigger tower calibration is achieved, the tower-to-tower alignment is calculated, and then the sector-tosector. Alignment is performed on each view (eta and phi) in steps of 1 bunch crossing period.

Finally a new set of calibration parameters is produced, to be used for system configuration and to be stored in the configuration database. Figure 7 shows the schematic view of the calibration algorithm.

More then 25 thousands of calibration constants are to be calculated and used online, using different calibration parameter sets depending on the physics (cosmics or collisions).

Figure 7: schema of the calibration procedure.

### E. Calibration Example

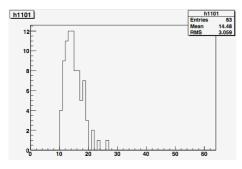

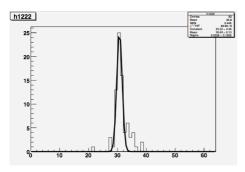

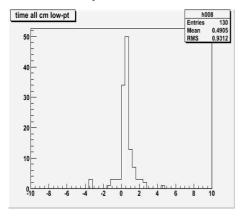

Figure 8 shows the time distribution for cosmics for a group of sixteen channels in one non-pivot plane, before the calibration. Using the latest pivot 16-channels group time as the reference, the time difference between the non-pivot and the pivot group is shown in Figure 9. Repeating this calculation for all groups of channels, we can calculate the delays to be applied to align in time all the groups. Figure 10 shows the misalignment after calibration.

Figure 8: row cosmics time distribution before calibration, time unit in x-axis is 3.125 ns.

Figure 9: time difference peak finder, time unit in x-axis is 3.125 ns.

Figure 10: sixteen-channels timing group misalignment after calibration, time unit in x-axis is 3.125 ns.

#### V. CONCLUSIONS

Calibration procedure has been developed so far for inplane and plane-to-plane alignment, tower-to-tower and sector-to-sector calibration being just started. The ATLAS sector 13 commissioning work allows for extensive studies on detector using standalone RPC or combined RPC-MDT tracking, for studies on chamber efficiency using combined tracking, for the checking of cabling work, for the comparison of the online-offline mapping, and for the studies of eta-phi matching. The level-1 RPC barrel configuration database is being developed (database structure built, now working on the interface with the configuration system and on the GUI). Finally the configuration strategy in case of Single Event Upsets for non-redundant registers (do not affect system functionality) is to be defined.

#### VI. REFERENCES

- [1] V. Bocci, G. Chiodi, S. Di Marco, E. Gennari, E. Petrolo, A. Salamon, R. Vari, S. Veneziano, "Prototype Slice of the Level-1 Muon Trigger in the Barrel Region of the ATLAS Experiment", in Proc. LECC 2001 pp. 236-239.

- [2] E. Petrolo, A. Salamon, R. Vari, S. Veneziano, "Barrel LVL1 Muon Trigger Coincidence Matrix ASIC User Requirement Document", ATL-COM-DAQ-2000-050.

- [3] E. Petrolo, A. Salamon, R. Vari, S. Veneziano "CMA ASIC Hardware Requirement document", ATL-COM-DAQ-2001-005.

- [4] E. Gennari, E. Petrolo, A. Salamon, R. Vari, S. Veneziano, "Radiation Tolerance Evaluation of the ATLAS RPC Coincidence Matrix Submicron Technology", in Proc. LEB 2000, 2000, pp. 236-239.

- [5] V. Bocci, E. Petrolo, A. Salamon, R. Vari, S. Veneziano, "The Design of the Coincidence Matrix ASIC of the ATLAS Barrel Level-1 Muon Trigger", in Proc. LECC 2002, pp. 261-265.

- [6] V. Bocci, E. Petrolo, A. Salamon, R. Vari, S. Veneziano, "The Coincidence Matrix ASIC of the Level-1 Muon Barrel Trigger of the ATLAS Experiment", in IEEE TNS, Aug. 2003, vol. 50, no 4.

- [7] G. Aielli et al., "Slice Test Results of the ATLAS Barrel Muon Level-1 Trigger", in Proc. LECC 2003.

- [8] G. Aielli et al., "Test Beam results and integration of the ATLAS Level-1 Muon Barrel Trigger", in Proc. NSS-MIC2004.

- [9] Fr. Pastore et al., "Performances of the Coincidence Matrix ASIC of the ATLAS Barrel Level-1 Muon Trigger", in Proc. LECC 2005.