# A multi-channel optical plug-in module for gigabit data reception

### S. Reynaud, P. Vichoudis

CERN, 1211 Geneva 23, Switzerland

Paschalis.Vichoudis@cern.ch

### Abstract

A plug-in module has been built for reception of optically transmitted data by gigabit applications. The optical receiving module is based on a 12-channel optical receiver and an FPGA with embedded high-speed deserializers. It is compatible with the serializer ASIC used by many LHC systems. Due to its compact design, several of these modules could be plugged into VME readout systems. This module will be the principle element for both the CMS Preshower data concentrator card and the TOTEM front-end driver.

### I. INTRODUCTION

The CMS Preshower [1] sub-detector comprises 4288 silicon sensors, each containing 32 strips. The data transport from the on-detector system is achieved by 1208 optical links running at 800Mbps. This enormous resulting data flow of ~1Tbps necessitates the reduction of the data volume. Indeed, given the expected maximum average strip occupancy of ~2%, a significant data reduction is feasible.

For the readout of the Preshower, a VME-based system able to acquire on-detector data from a number of optical fibres, perform the appropriate on-line data reduction algorithms and pass the concentrated data to the CMS event builder is required.

Recent studies [2] have shown that the requirements of the Preshower for on-line data reduction cannot be met by existing readout hardware designed for use by other CMS sub-detectors.

Hence, the need for the development of a CMS Preshower data concentrator card coincided with a need for a readout system (but with different requirements) for the TOTEM experiment [3]. This gave birth to the idea of a modular VME-based readout system, common to both systems allowing selection of which constituent modules are to be used, depending on the requirements of each system.

The 12-channel optical plug-in module for gigabit data reception (OptoRx-12) presented in this manuscript is the principle element for both readout systems.

#### **II. IMPLEMENTATION**

The optical receiving module is based on a 12-channel optical receiver and an FPGA with embedded gigabit deserializers. Figure 1 shows a photograph of the module.

The 12-channel digital optical receiver (NGK's POR10M12SFP [4]) used is the one specified for the CMS ECAL optical links and it is qualified for data rates up to 1.25Gbps. The 1310nm optical receiver uses a "Multi-fiber

Push On" (MPO) connector for the interconnection of the 12-fibre ribbon.

Figure 1: Photograph of the OptoRx-12.

The FPGA used belongs to the Altera's Stratix GX family [5] that incorporates embedded hardware deserializers with data rate up to ~3.2Gbps. The FPGA deserializers provide built-in functions compatible with the Gigabit Ethernet (8b/10b encoding) [6] protocol. This feature of the FPGA is very important since this encoding scheme is used by the GOL [7] serializer ASIC that drives the optical links of both the Preshower and TOTEM front-end systems. It is worth mentioning that tests have shown<sup>1</sup> that the deserializers can be configured to be also compatible with the other transmission protocol (G-Link [8]) supported by the GOL ASIC, used by other LHC systems.

The module is compatible with two FPGA devices (1SGX25FF1020 & 1SGX40GF1020) from the Stratix GX family, allowing the selection of the appropriate device depending on the logic resources required for each application. Table 1 summarizes the features of the two compatible FPGA devices. One of the most important features of these FPGA devices is the way the dedicated memory resources are fragmented, allowing the instantiation of a large number of individual memory blocks. This feature plays an essential role for on-line multi-channel data processing applications and it was the decisive factor for selecting this FPGA family [9]. For this decision, important role also played the previous experience with FPGA devices from the same family, where a testbench [10] was based on.

<sup>&</sup>lt;sup>1</sup> Extensive tests have been carried out for the possible use of the module as a part of the Level 0 Pixel Trigger System for the ALICE Silicon Pixel Detector. Although the module has been configured successfully as a 12-channel G-Link receiver, it cannot be used for this project since its deserialization latency is greater than the trigger system can tolerate [11].

|                    | 1            |              |

|--------------------|--------------|--------------|

| FEATURES           | 1SGX25FF1020 | 1SGX40GF1020 |

| Logic Elements     | 25,660       | 41,250       |

| 512bit RAM blocks  | 224          | 384          |

| 4Kbit RAM blocks   | 138          | 183          |

| 512Kbit RAM blocks | 2            | 4            |

| Total RAM bits     | 1,944,576    | 3,423,744    |

| 9x9 multipliers    | 80           | 112          |

Table 1: FPGA comparison

The module incorporates an electrical interface with 280 single-ended lines connected to the FPGA's I/O pins via 5 PMC connectors. The 64 pins are reserved for controlling the module through a local bus. The remaining pins could even cover the possible requirement of providing all the deserialized data in parallel<sup>2</sup>. Although the total number of interconnections is large, its size was kept relatively small<sup>3</sup>, allowing several of these modules to be plugged onto a VME64 board [12]. A JTAG connector for the configuration of the module is also available.

The optical receiving module also provides an optional connector on the bottom side<sup>4</sup>, for attaching an S-Link64 [13] transmitter mezzanine card, if required (i.e. for the TOTEM front-end driver). Figure 2 shows a photograph of the module with an S-Link64 transmitter mezzanine card attached to it. In this case, the stacking height of this combination of mezzanine cards exceeds the specified limits for VME cards. Therefore, the VME systems based on this configuration (i.e. the TOTEM front-end driver) will have to occupy two consecutive slots of the VME rack.

Figure 2: Photograph of the OptoRx-12 with an S-Link64 Transmitther attached to it.

## **III. EVALUATION**

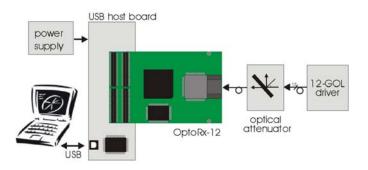

The evaluation of the performance for that kind of equipment is a complicated and time-consuming process, since the most important issue is to examine how frequently an error in the data reception can occur. The required setup for the evaluation of the module incorporates the following: • A pattern generator able to provide 12 optical serial output streams. The device used is a programmable 12-GOL driver [14] developed by TOTEM. The device incorporates an FPGA that drives independently 12 GOL serializer ASICs. For the purpose of these tests, the device was programmed to generate continuously 12 different sequences of pseudo-random numbers based on linear feedback shift registers (LFSRs) [15]. This device is illustrated in Figure 3.

Figure 3: Photograph of the 12-GOH driver used as a pattern generator for the evaluation of the OptoRx-12.

- A variable optical attenuator. The attenuator is introduced in between the 12-GOL driver and the OptoRx-12.

- The plug-in module itself programmed with a special firmware that generates pseudo-random numbers (based on identical algorithms as implemented in the 12-GOL driver) and compares them with the words received from its twelve serial inputs.

- A host board where the module is plugged-in that provides power, clock as well as a USB interface to a personal computer to retrieve the error measurement results from the OptoRx-12. This device is illustrated in Figure 4.

- A PC and associated software.

Figure 4: Photograph of the support board that provides power, clock, JTAG and USB interface to the OptoRx-12, used for evaluation purposes.

Figure 5: The evaluation setup.

<sup>&</sup>lt;sup>2</sup> (16bit data + 2bit control) x 12 = 216bit.

<sup>&</sup>lt;sup>3</sup> Length: 115mm, width: 75mm, height: 14mm (10mm PMC connector stacking height + 2mm PCB thickness + 2mm height of the mechanical components on the bottom side i.e. screws etc).

<sup>&</sup>lt;sup>4</sup> Top side, when the module is plugged.

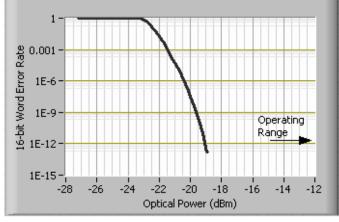

A block diagram of the evaluation setup is shown in Figure 5. Error rate measurements were taken using this setup where the optical signal was attenuated gradually. Figure 6 shows a graph with the word error rate vs the optical power, for one of the channels.

The outcome of the measurements (that have lasted about a month) is that the sensitivity of the overall system coincides with that of the digital optical receiver (-19dBm) [4]. Therefore, the additional (to the digital optical receiver) components do not affect the overall performance of the optical receiving module. It is worth mentioning that during the CMS experiment, the operating optical power in the Preshower data concentrator card is expected to be more than two orders of magnitude higher (>-12dBm). Therefore, no errors are expected in this operating range.

Figure 6: Error Rate vs absolute optical power for one of the input channels of the module. The sensitivity of the overall system coincides with that of the digital optical receiver (-19dBm).

### **IV. SUMMARY & CONCLUSIONS**

A plug-in module built for reception of optically transmitted data by gigabit applications has been developed. The optical receiving module incorporates a 12-channel optical receiver and an FPGA with embedded high-speed deserializers.

The module is fully compatible with the serializer ASIC used for high-speed data transmission by many LHC systems. Its compact size allows its use as a mezzanine card plugged into VME-based readout systems.

The performance of the module was extensively tested and its behavior been deemed satisfactory. The fact that the sensitivity of the overall system coincides with that of the digital optical receiver has proven that the additional components of the optical receiving module do not affect the overall performance.

This module will be the principle element for both the CMS Preshower data concentrator card and the TOTEM front-end driver.

Besides forming the basis of the CMS Preshower data concentrator card and the TOTEM front-end driver, it is envisaged that this compact plug-in module will also be useful for the readout of other detector electronics systems, for LHC and beyond.

#### V. ACKNOWLEDGEMENTS

The authors would like to thank Georgios Sidiropoulos (from the University of Ioannina, Greece) for his idea of building modular (and thus easily upgradable) readout systems, based on plug-in modules like the one presented in this manuscript.

#### **VI. REFERENCES**

[1] P.Wertelaers et al, "ECAL Preshower Engineering Design Review", CMS ECAL EDR-4 https://edms.cern.ch/document/ 115565/1

[2] N. Manthos et al, "Study of algorithms for on-line CMS Preshower data reduction and their possible implementation in FPGAs on-board the CMS ECAL DCC" CMS internal note in preparation.

[3] The TOTEM collaboration "TOTEM: Technical Design Report", CERN-LHCC-2004-002.

[4] NGK Insulators, Ltd. "Specification for parallel optical digital receiver", August 2002

[5] For details concerning the Altera Stratix GX FPGA family http://www.altera.com/products/devices/stratixgx/overview/ sgx-overview.html

[6] IEEE standard 802.3, 1998 edition.

[7] P.Moreira et al, "*G-Link and Gigabit Ethernet Compliant Serializer for LHC Data Transmission*" presented at the IEEE Nuclear Science Symposium and Medical Imaging Conference, 2000.

[8] C. Yen, R. Walker, P. Petruno, C. Stout, B. Lai and W. McFarland, "*G-Link:* "A chipset for Gigabit-Rate Data Communication" Hewlett-Packard Journal, Oct. 92.

[9] G. Sidiropoulos, P. Vichoudis et al, "On-line data reduction algorithms targeted for the Endcap Preshower Data Concentrator Card" CMS NOTE in preparation.

[10] P. Vichoudis et al, "A flexible stand-alone testbench for facilitating system tests of the CMS Preshower" presented at the 10th Workshop on electronics for LHC and other experiments, 2004.

[11] G. A. Rinella et al., "*The Level 0 Pixel Trigger System* for the ALICE Silicon Pixel Detector", presented at the 12th Workshop on electronics for LHC and other experiments, 2006.

[12] IEEE standard 1101.1, 1998 edition.

[13] S-Link64 project site: http://cms-frl.home.cern.ch/

[14] G. Antchev et al "Schematics design files for VFAT Emulator" https://edms.cern.ch/document/672564/1.

[15] P. Alfke "Efficient Shift Registers, LFSR Counters, and Long Pseudo-Random Sequence Generators" Xilinx Application note 052, 1996