## **Introduction to Electronics in HEP Experiments**

Philippe Farthouat CERN

Introduction to Electronics Summer 2009

philippe.farthouat@cern.ch

# Outline

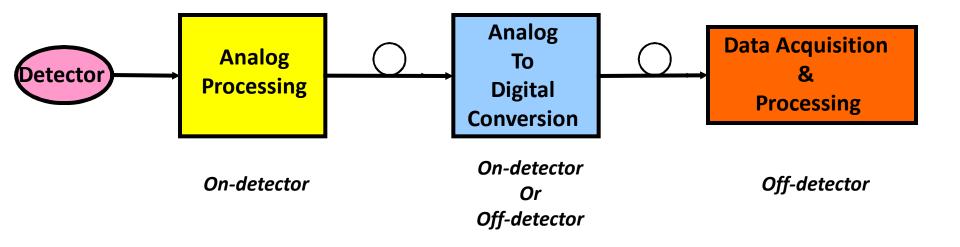

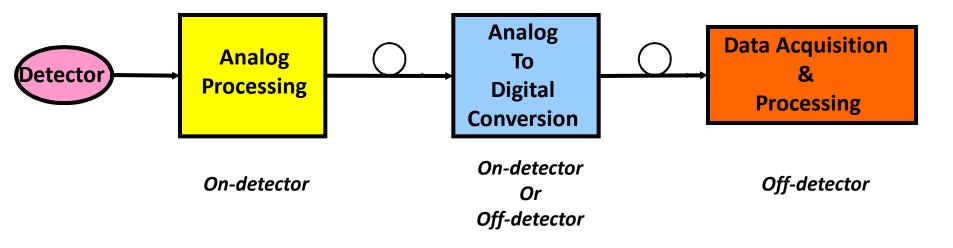

# Analog processing Analog to digital conversion Technology evolution Off-detector digital electronics

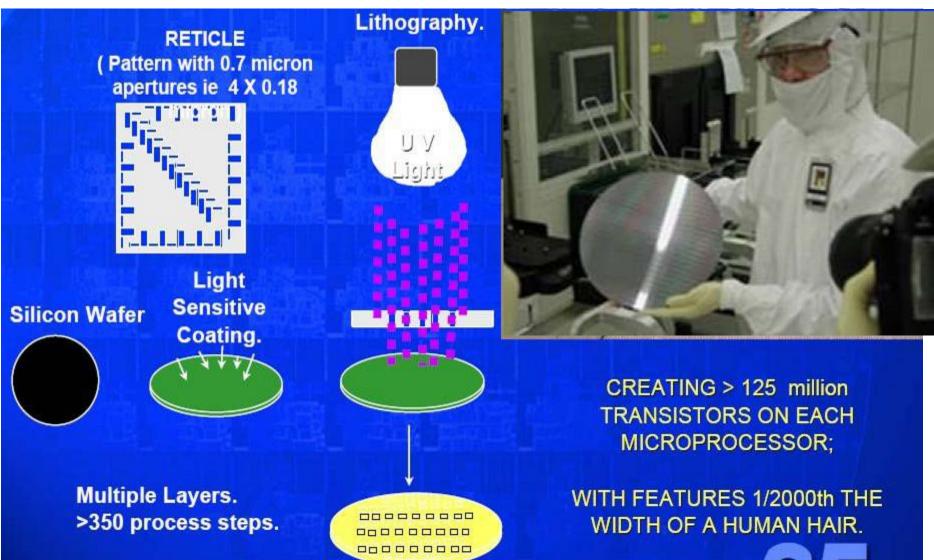

## **Processing of ASICs**

© Intel

#### From Sand to ICs...

Introduction to Electronics Summer 2009

philippe.farthouat@cern.ch

# **Processing of ASICs**

For those interested in integrated circuits processing, please refer to F. Faccio presentation (from which I stole a few slides)

#### Step-by-step manufacturing of ULSI CMOS technologies

http://indico.cern.ch/conferenceDisplay.py?confld=48132

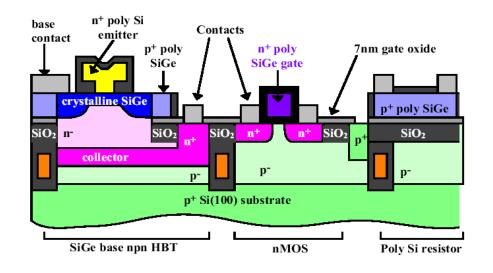

## **Evolution of technologies**

#### SiGe Bipolar in 0.35µm monolithic process

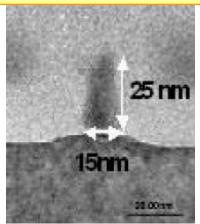

#### 15 nm MOSFET (2005)

#### 5 µm MOSFET (1985)

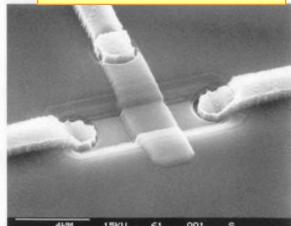

#### First planar IC (1961)

Introduction to Electronics Summer 2009

philippe.farthouat@cern.ch

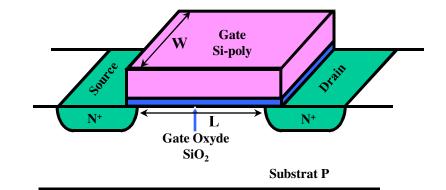

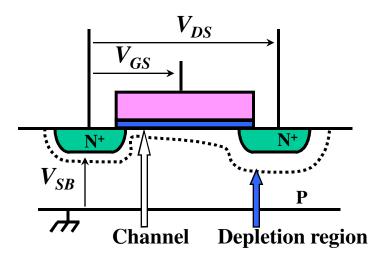

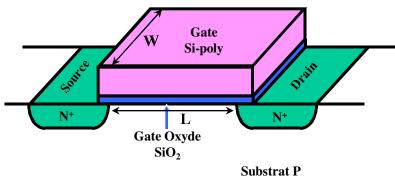

#### « CMOS scaling »

#### Reduction of dimensions

- Gate length : L

- Oxide thickness : t<sub>ox</sub>

- Improvement of speed in 1/L<sup>2</sup>

- Transconductance : g<sub>m</sub> α W/L

- Capacitance : C α WL

- speed :  $F_T = g_m/C \alpha 1/L^2$

- Reduction of power dissipation

- Capacitances decrease

- Power supply level decreases

- 2.5V in 0.25μm; 1.2V in 0.13μm

- Current remains high!

- Reduction of costs (?)

- Increase of integration density

- Non recurrent engineering (NRE) costs increase

Principle of Nchannel MOSFET

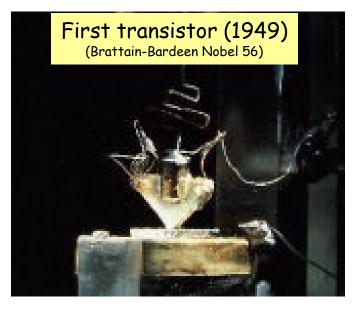

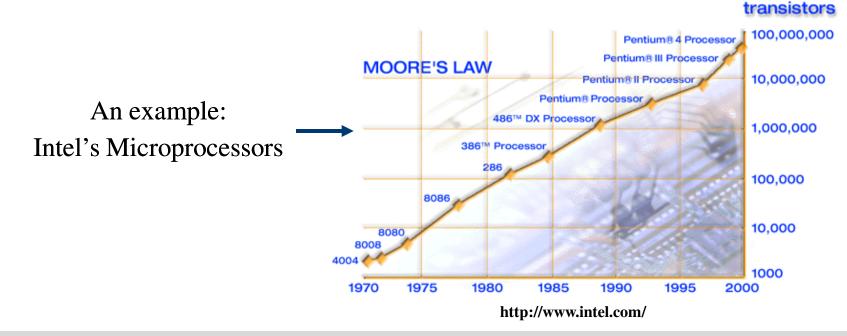

# Moore's law

1965: Number of Integrated Circuit components will double every year G. E. Moore, "Cramming More Components onto Integrated Circuits", *Electronics*, vol. 38, no. 8, 1965. 1975: Number of Integrated Circuit components will double every 18 months

G. E. Moore, "Progress in Digital Integrated Electronics", Technical Digest of the IEEE IEDM 1975.

1996: The definition of "Moore's Law" has come to refer to almost anything related to the semiconductor industry that when plotted on semi-log paper approximates a straight line. I don't want to do anything to restrict this definition. - G. E. Moore, 8/7/1996

P. K. Bondyopadhyay, "Moore's Law Governs the Silicon Revolution", *Proc. of the IEEE*, vol. 86, no. 1, Jan. 1998, pp. 78-81.

## Moore's law fundamentals

For every generation:

- Characteristic Dimensions x 0.7

- 🔷 Area x 0.5

- Chip size x 1.5

- Structural improvement x 1.3

- N of components x 4

- Clock frequency x 1.4

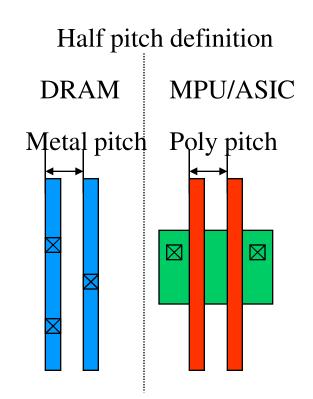

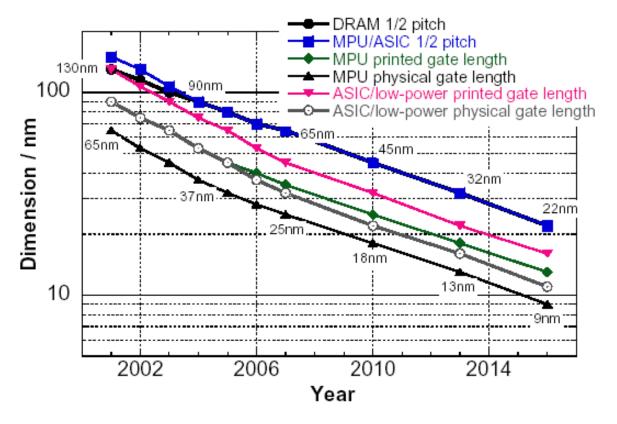

Technology nodes (1/2 pitch):

$$0.7 0.7$$

250 -> 180 -> 130 -> 90 -> 65 -> 45 -> 32 -> 22 -> 16

0.5

# **CMOS technology scaling**

This roadmap is 7 years old: Now 45 nm is in production

## **CMOS technology**

#### Details can be found in the following presentations

#### IEDM summary and outlook (Walter Snoeys)

http://indico.cern.ch/conferenceDisplay.py?confId=49285

#### Summary from ISSCC09 (Alessandro Marchioro)

http://indico.cern.ch/conferenceDisplay.py?confld=48130

# Impact for our applications

#### What do we gain?

- Radiation hardness

- Integration

- Power dissipation

- Speed

#### What do we loose?

Non recurrent engineering (NRE) costs are high

- Order of 0.5MChF for 0.13µm CMOS technology

- Wafer cost is low but our production volume is low

- Limit as much as possible the iterations (prototyping)

- Limit the number of different designs

- Design tools are extremely complex

- Long learning curve

- High investment

Radiation hardness is an issue for a number of our applications

- e.g. LHC experiments tracker electronics can receive as much as 100Mrad (1MGy) during their lifetime

- In CMOS technology most of the problems are coming from charge trapping in the gate oxyde

- When the gate is very thin, there is less or no problems

Those interested in the subject can look at a presentation from F. Faccio

http://indico.cern.ch/materialDisplay.py?contribId=34&materialId=slides&confId=43007

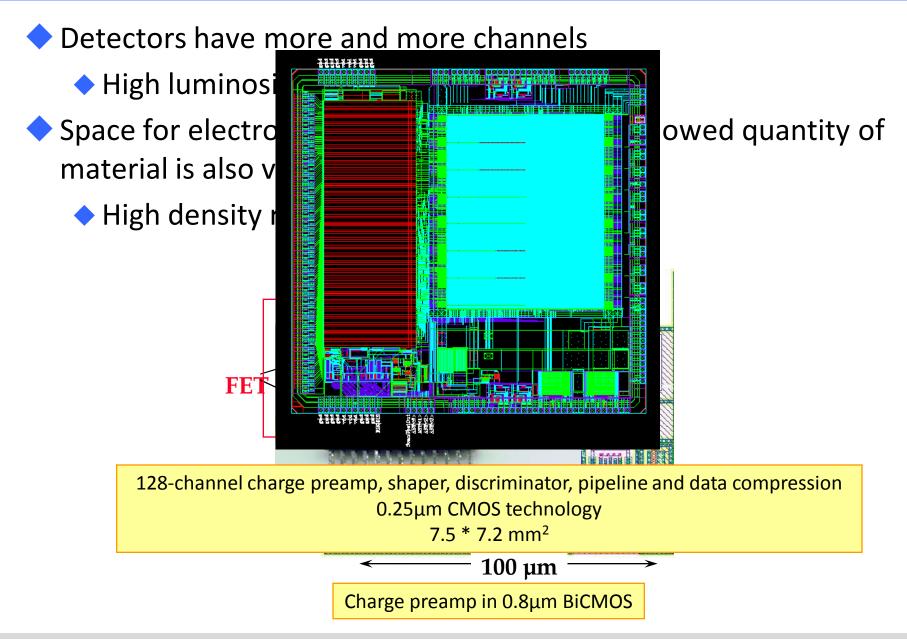

# Gain in integration (1)

# Gain in integration (2)

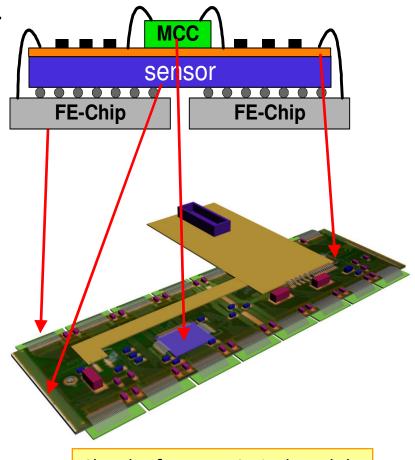

- Pixel detectors require the readout electronics bump bond on the sensor

- Space available for the readout electronics is equal to the size of the pixel

- ATLAS case 400\*50 μm<sup>2</sup> today

- Smaller for upgrade 250\*50 μm<sup>2</sup>

- Smaller feature size technology needed

- Current readout chip in 0.25µm

CMOS technology

- 🔷 Next in 0.13μm

## Gain in power

#### Power is always a problem

(see for instance Power distribution in future experiments (F. Faccio) http://indico.cern.ch/conferenceDisplay.py?confld=39721 )

- Heat dissipation in enclosed volume

- Cables needed to bring the power in

- Even 1mW per channel for a tracker leads to 60kW in an "LHC like" tracker

- The wish of having the ADC as early as possible in the readout chain requires low power ADC

- Standard metric to characterize an ADC is the "Figure of Merit"

$$FOM = \frac{Power}{2^{ENB} \times F_{sampling}}$$

|                                                             | 0.25μm<br>FOM=1pJ/conv | 65nm<br>FOM=50fJ/conv | Saving in Power Supply<br>(8ChF/W) |

|-------------------------------------------------------------|------------------------|-----------------------|------------------------------------|

| ATLAS Calorimeter<br>200k channels<br>15-ENB 40MHz          | 262 KW                 | 13 KW                 | ~2 MChF                            |

| Linear Collider Calorimeter<br>15M channels<br>13-ENB 50MHz | 6.4 MW                 | 340 kW                | A lot                              |

Courtesy A. Marchioro CERN

# Outline

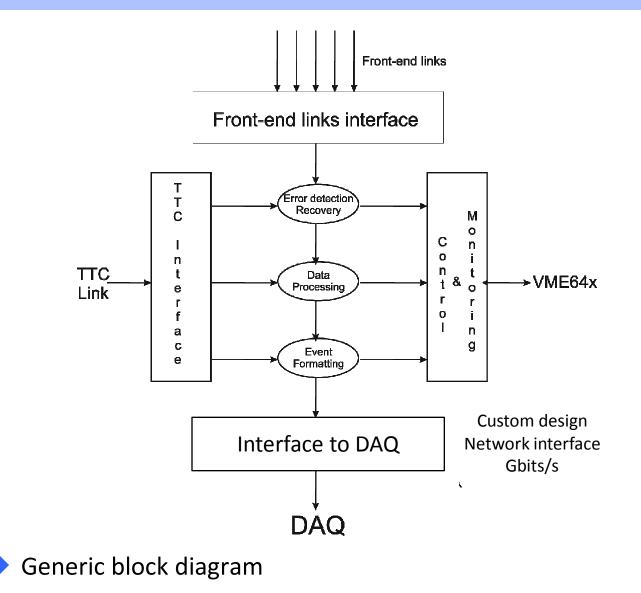

## **Off-detector readout electronics**

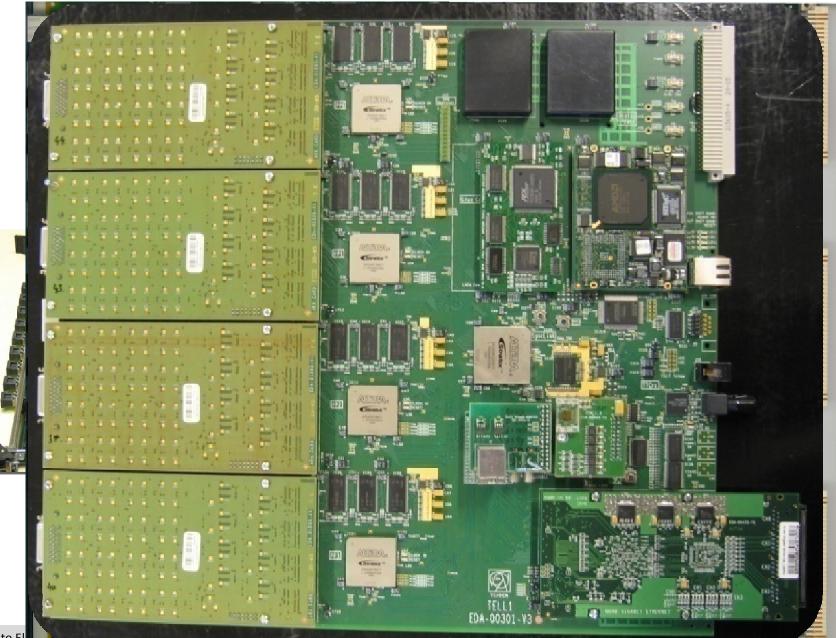

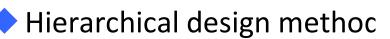

## **Examples of modules**

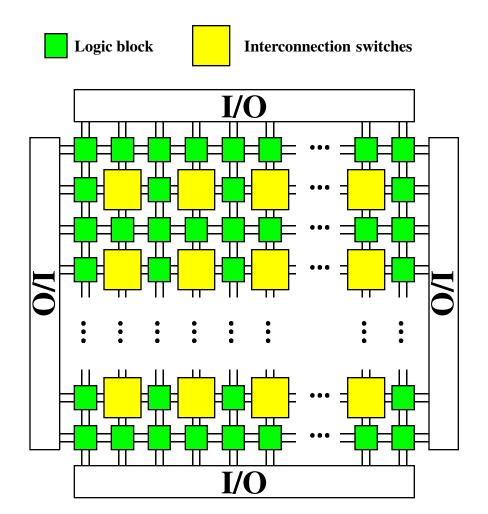

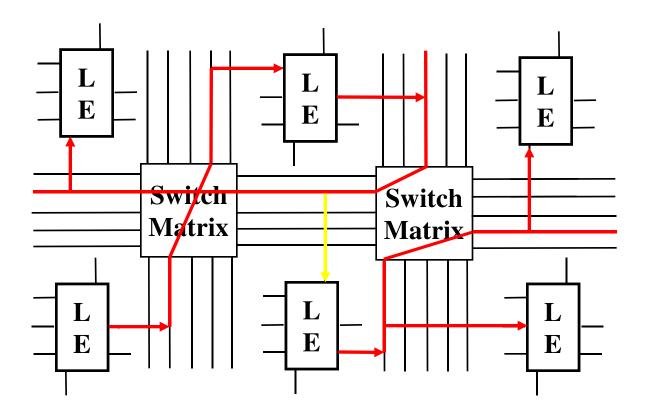

#### FPGA building blocks:

- Programmable logic blocks Implement combinatorial and sequential logic

- Programmable interconnect Wires to connect inputs and outputs to logic blocks

- Programmable I/O blocks

Special logic blocks at the periphery of device for external connections

#### Clock distribution

- Embedded memory blocks

- Special purpose blocks:

- DSP blocks:

- Hardware multipliers, adders and registers

- Embedded microprocessors/microcontrollers

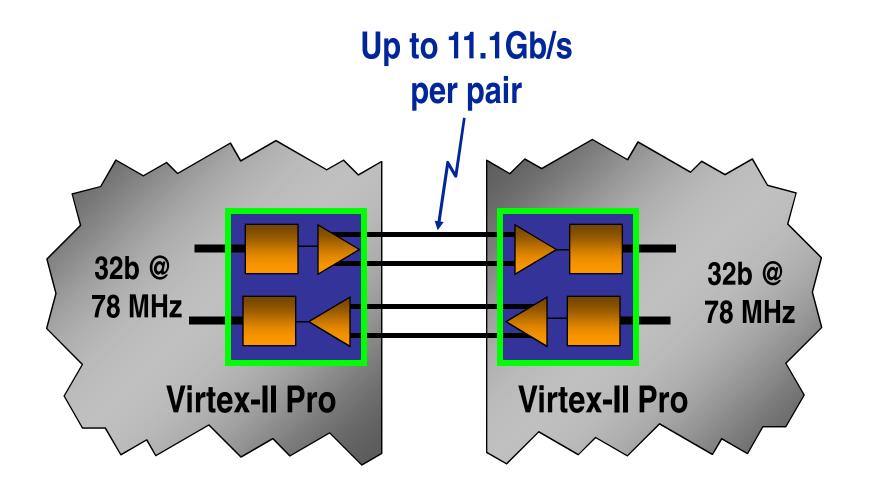

- High-speed serial transceivers

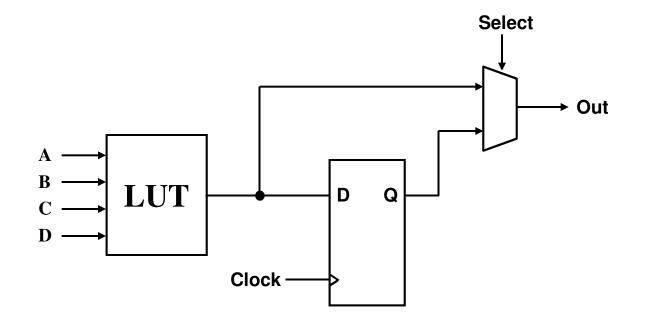

## **FPGA – Basic Logic Element**

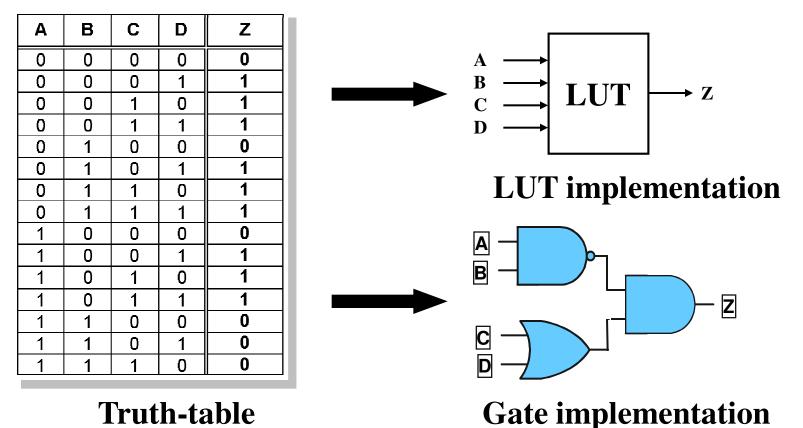

- LUT to implement combinatorial logic

- Register for sequential circuits

- Additional logic (not shown):

- Carry logic for arithmetic functions

- Expansion logic for functions requiring more than 4 inputs

Look-up table with N-inputs can be used to implement any combinatorial function of N inputs

LUT is programmed with the truth-table

#### Interconnect hierarchy (not shown)

- Fast local interconnect

- Horizontal and vertical lines of various lengths

## **Configuration Storage Elements**

#### Static Random Access Memory (SRAM)

- each switch is a pass transistor controlled by the state of an SRAM bit

- FPGA needs to be configured at power-on

- Flash Erasable Programmable ROM (Flash)

- each switch is a floating-gate transistor that can be turned off by injecting charge onto its gate. FPGA itself holds the program

- reprogrammable, even in-circuit

- Fusible Links ("Antifuse")

- Forms a low resistance path when electrically programmed

- one-time programmable in special programming machine

- radiation tolerant

#### Xilinx: Rocket I/O

## **FPGA Vendors & Device Families**

#### 🔶 Xilinx

- Virtex-II/Virtex-4: Featurepacked high-performance SRAM-based FPGA

- Spartan 3: low-cost feature reduced version

- CoolRunner: CPLDs

- 🔷 Altera

- Stratix/Stratix-II

- High-performance SRAMbased FPGAs

- Cyclone/Cyclone-II

- Low-cost feature reduced version for cost-critical applications

- MAX3000/7000 CPLDs

- MAX-II: Flash-based FPGA

#### 🔷 Actel

- Anti-fuse based FPGAs

- Radiation tolerant

- Flash-based FPGAs

- Lattice

- Flash-based FPGAs

- CPLDs (EEPROM)

- QuickLogic

- ViaLink-based FPGAs

#### **Latest Devices: Capacity & Features**

#### **Xilinx Virtex-6**

- 🔶 40nm process

- Up to 1200 I/Os

- Up to 760k logic cells

- Up to 38Mb embedded RAM

- Up to 2000 DSP slices

- Up to 36 high-speed serial transceivers at 11.1GB/s

#### **Altera Stratix-IV**

- 40nm process

- Up to 1104 I/Os

- Up to 680k logic elements

- Up to 22.4Mb embedded RAM

- Up to 1288 18x18 multipliers

- Up to 48 Serial I/O at 11.5Gb/s

#### Plus processors (PowerPC)

## **FPGAs evolution**

- 1988: XC3090

- 2008: XC5VLX330T

- 1000 times the number of LUTs

- 2000 times the number of configuration bits = complexity

- 20 times the speed

- 500 times cheaper per function, not counting inflation

#### Moore's Law has been good to all of us!

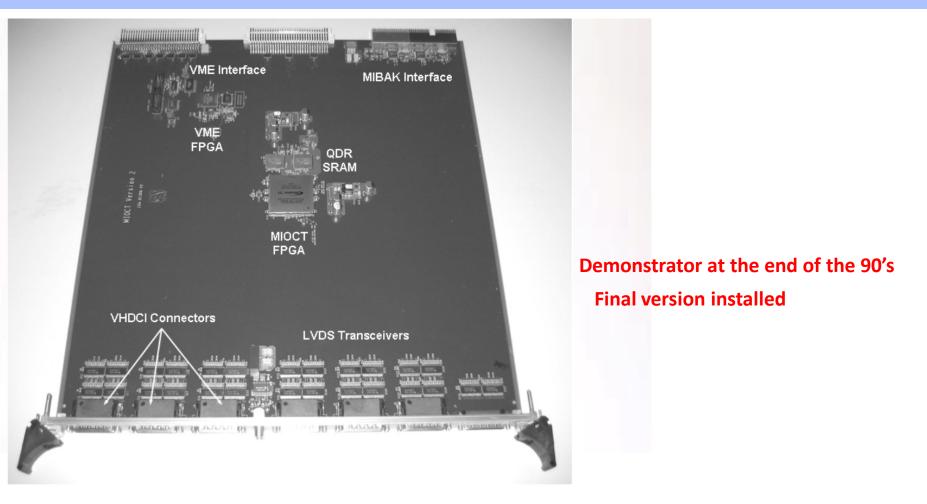

## **Example of evolution**

Muon trigger board for ATLAS

- Handles 13 input links, each of them receiving 32-bit every 25ns

- ~17 Gb/s processed

#### Hardware Description Language (HDL)

High-level language for to model, simulate, and synthesize digital circuits and systems.

## History

- 1980: US Department of Defense Very High Speed Integrated Circuit program (VHSIC)

- 1987: Institute of Electrical and Electronics Engineers ratifies IEEE Standard 1076 (VHDL'87)

- ◆ 1993: VHDL language was revised and updated

- Verilog is the other major HDL

Syntax similar to C language

- At CERN VHDL is mostly used for FPGA design

- Many tools accept both Verilog and VHDL

#### Behavioral modeling

- Describes the functionality of a component/system

- For the purpose of simulation and synthesis

### Structural modeling

- A component is described by the interconnection of lower level components/primitives

- For the purpose of synthesis and simulation

- Synthesis:

- Translating the HDL code into a circuit, which is then optimized

- Register Transfer Level (RTL):

Type of behavioral model used for instance for synthesis

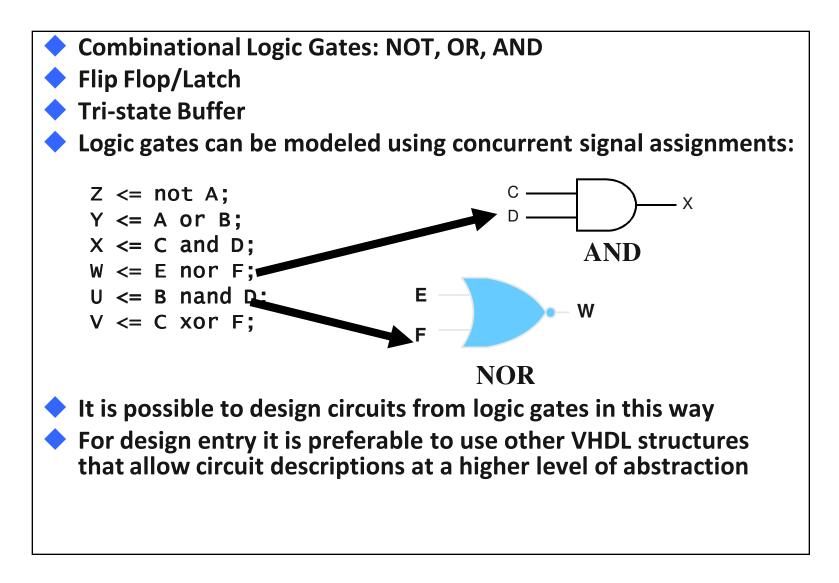

Most digital systems can be described based on a few basic circuit elements:

- Combinational Logic Gates:

- ◆NOT, OR, AND

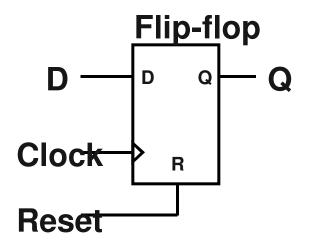

- Flip Flop

- Latch

- Tri-state Buffer

Each circuit primitive can be described in VHDL and used as the basis for describing more complex circuits.

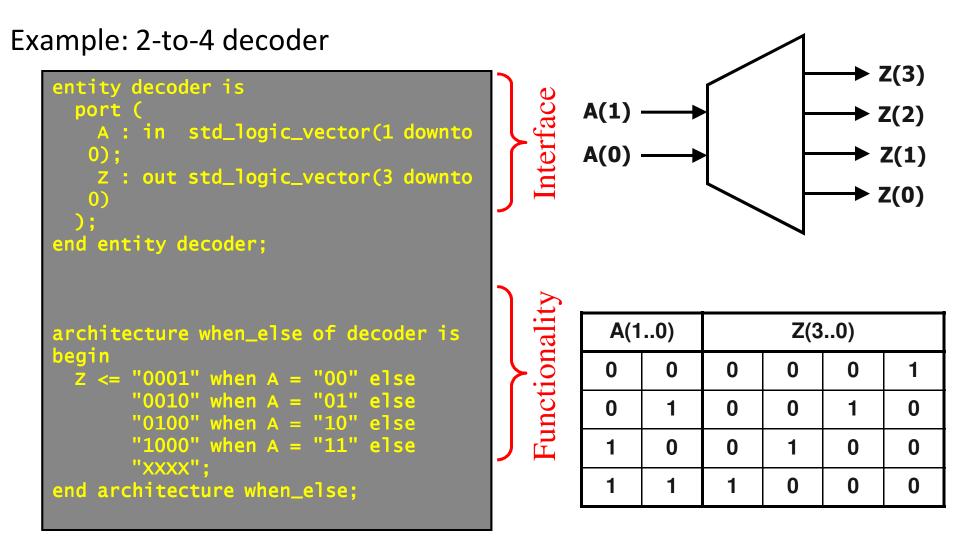

## **Combinatorial Logic: Decoder**

```

architecture rtl of D_FF is

begin

process (Clock, Reset) is

begin

if Reset = '1' then

Q <= '0';

if rising_edge(Clock)

then

Q <= D;

end if;

end process;

end architecture rtl;

```

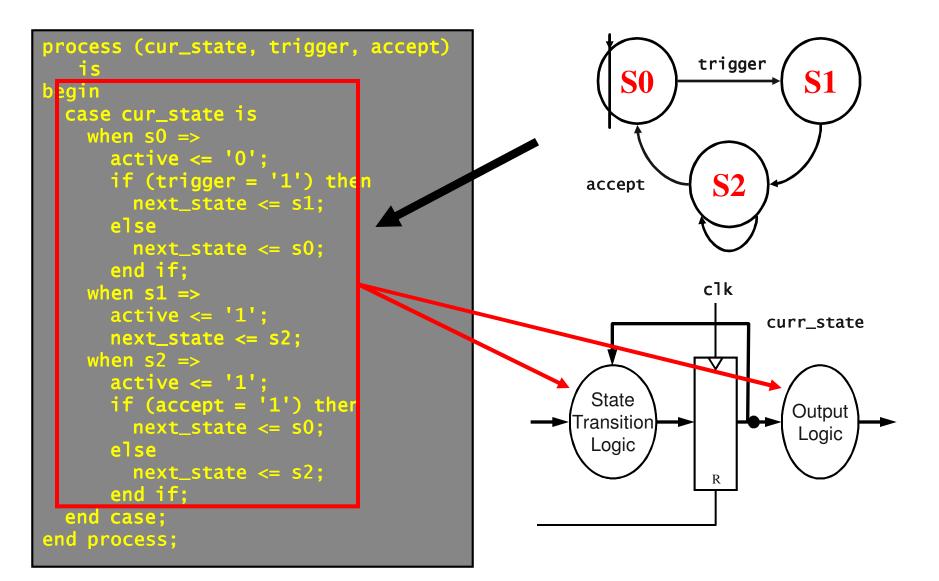

### State Machine (cont.)

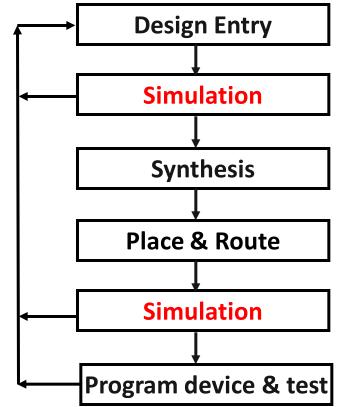

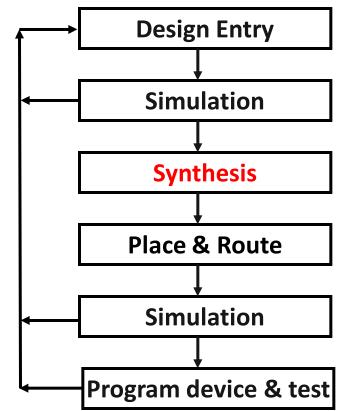

# **FPGA Design Flow**

# **Design Entry/RTL Coding**

Behavioral or Structural Description of Design

## **RTL Simulation**

- Functional Simulation

- Verify Logic Model & Data Flow (No Timing Delays)

- Translate Design into Device Specific Primitives

- Optimization to Meet Required Area & Performance Constraints

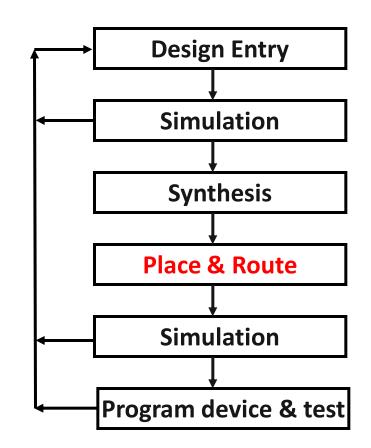

### **Place & Route**

- Map Primitives to Specific Locations inside Target Technology with Reference to Area &

- Performance Constraints

- Specify Routing Resources to Be Used

# **FPGA Design Flow**

# **Timing Analysis**

- Verify Performance Specifications Were Met

- Static Timing Analysis

### **Gate Level Simulation**

- Timing Simulation

- Verify Design Will Work in Target Technology

### Program & Test

- Program & Test Device on Board

# Special mode for editing VHDL source files in emacs

- Features:

- Syntax colouring

- Automatic completions

- Automatic indentation

- Templates for all VHDL constructs

- Launching external VHDL compiler

| 🕈 fsm.vhd - XEmacs                                                |                    |             |  |  |  |  |  |  |  |  |

|-------------------------------------------------------------------|--------------------|-------------|--|--|--|--|--|--|--|--|

| File Edit View Cmds Tools Options B                               | Uffers VHDL        | Help        |  |  |  |  |  |  |  |  |

|                                                                   | Project            | +           |  |  |  |  |  |  |  |  |

| Open Dired Save Print Cut Copy                                    | Paste Compile      | •           |  |  |  |  |  |  |  |  |

| fsm.vhd                                                           | Template >         |             |  |  |  |  |  |  |  |  |

| entity trigger is                                                 | If (Generate)      | C-cC-tig    |  |  |  |  |  |  |  |  |

| port (                                                            | 76 (Thur)          | C-cC-tit    |  |  |  |  |  |  |  |  |

| clk, reset : in st<br>trigger, accept : in st                     | Library            | C-c C-t li  |  |  |  |  |  |  |  |  |

| trigger, accept : in st<br>active : out st                        | Loop               | C-c C-t lo  |  |  |  |  |  |  |  |  |

| end entity trigger;                                               | Мар                | C-cC-tma    |  |  |  |  |  |  |  |  |

|                                                                   | Next               | C-cC-tne    |  |  |  |  |  |  |  |  |

| architecture rtl of trigger                                       | Others (Aggregate) | C-cC-tot    |  |  |  |  |  |  |  |  |

| type state type is (sO,                                           | Package (Decl)     |             |  |  |  |  |  |  |  |  |

| signal cur_state,                                                 | Package (Body)     |             |  |  |  |  |  |  |  |  |

| <pre>next_state : state_type;</pre>                               | Port               | C-cC-tpo    |  |  |  |  |  |  |  |  |

| begin                                                             | Procedure (Body)   | C-cC-tpb    |  |  |  |  |  |  |  |  |

| registers : process (clk,                                         | Procedure (Decl)   | C-cC-tpd    |  |  |  |  |  |  |  |  |

| begin                                                             | Process (Comb)     | C-cC-tpc    |  |  |  |  |  |  |  |  |

| if (reset = '1') then                                             | Process (Seq)      | C-c C-t p s |  |  |  |  |  |  |  |  |

| cur_state <= s0;                                                  | Report             | C-cC-trp    |  |  |  |  |  |  |  |  |

| <pre>elsif rising_edge(clk) t     cur state &lt;= next stat</pre> | Dohuro             | C-cC-trt    |  |  |  |  |  |  |  |  |

| end if:                                                           | Select             | C-c C-t s s |  |  |  |  |  |  |  |  |

| end process;                                                      | Signal             | C-c C-t s i |  |  |  |  |  |  |  |  |

| • ·                                                               | Subtype            | C-c C-t s u |  |  |  |  |  |  |  |  |

| process (cur state, trigge                                        | Туре               | C-cC-tty    |  |  |  |  |  |  |  |  |

| begin                                                             | Use                | C-c C-t u s |  |  |  |  |  |  |  |  |

| case cur_state is                                                 | Variable           | C-cC-tva    |  |  |  |  |  |  |  |  |

| when s0 =>                                                        | Wait               | C-c C-t w a |  |  |  |  |  |  |  |  |

| active <= '0';                                                    | (Clocked Wait)     | C-c C-t w c |  |  |  |  |  |  |  |  |

| if (trigger = '1') t                                              | When               |             |  |  |  |  |  |  |  |  |

| next_state <= s1;                                                 | While (Loop)       | C-c C-t w l |  |  |  |  |  |  |  |  |

| else                                                              | With               | C-c C-t w i |  |  |  |  |  |  |  |  |

| next_state <= s0;                                                 |                    |             |  |  |  |  |  |  |  |  |

# **Block Diagram**

- top-down

- bottom-up

- Contents of a block can be type of design unit

- Top-level block diagram:

- Partitioning of the design

- Connections between the underlying HDL design units

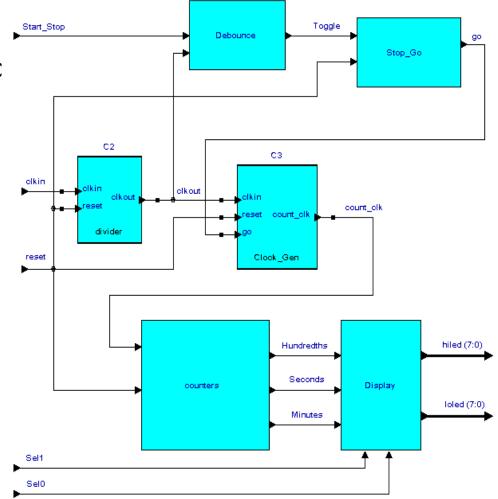

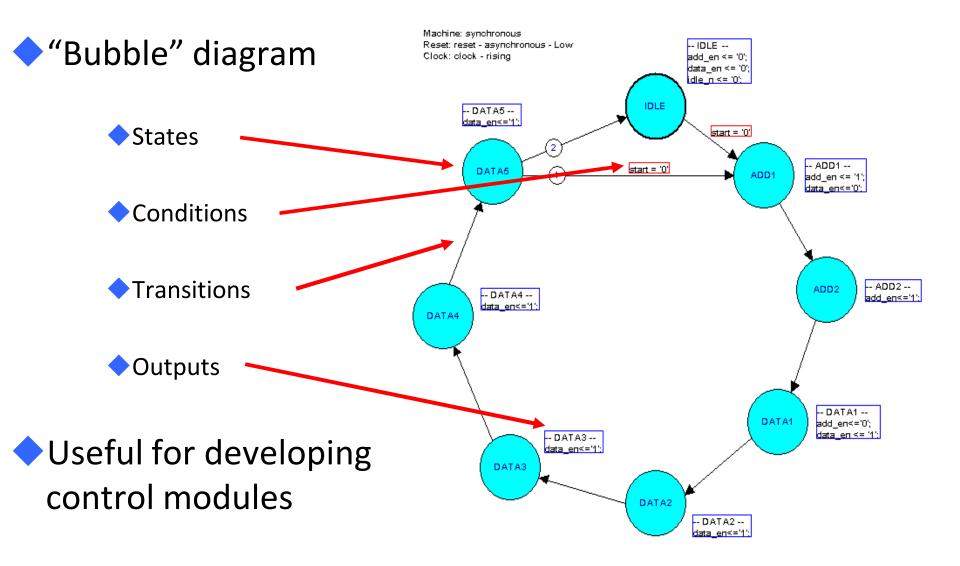

# **State Diagram**

- Normally used to describe combinatorial logic

- Can also be used for sequential circuits (e.g. state machines)

| ■ Truth Table - STUDENT:decoder24<br>→ ① ① ● ① ② ② ② ② ② ② ② ② ◎ ② ◎ ◎ ◎ ◎ ◎ ◎ ◎ ◎ ◎ |     |         |        |           |           |           |           |   |          |  |

|--------------------------------------------------------------------------------------|-----|---------|--------|-----------|-----------|-----------|-----------|---|----------|--|

| In                                                                                   |     | address | 5      |           |           |           |           |   |          |  |

|                                                                                      | All | 1       | 2      | 3         | 4         | 5         | 6         | 7 |          |  |

|                                                                                      | All | address | enable | data(0)   | data(1)   | data(2)   | data(3)   |   |          |  |

|                                                                                      | 1   |         |        | NOT level | NOT level | NOT level | NOT level |   |          |  |

|                                                                                      | 2   |         |        |           |           |           |           |   |          |  |

|                                                                                      | 3   | "00"    | 11     | level     |           |           |           |   |          |  |

|                                                                                      | 4   | "01"    | 41     |           | level     |           |           |   |          |  |

|                                                                                      | 5   | "10"    | 41     |           |           | level     |           |   |          |  |

|                                                                                      | 6   | "11"    | 41     |           |           |           | level     |   |          |  |

|                                                                                      | 7   |         | 'O'    | 'Z'       | 'Z'       | 'Z'       | 'Z'       |   |          |  |

|                                                                                      | 8   |         |        |           |           |           |           |   | <b>•</b> |  |

|                                                                                      |     | •       |        |           |           |           |           | Þ |          |  |

# Functional simulation:

- simulate independent of FPGA type

- may postpone selection

- 🔷 no timing

- Timing simulation:

- simulate after place and routing

- detailed timing

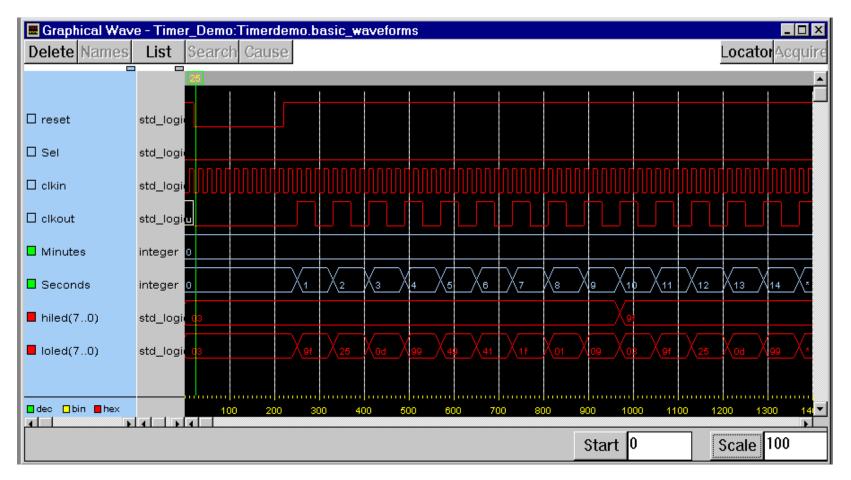

#### Example of simulation waveforms. Test vectors are normally defined in a VHDL unit (testbench)

### Input is RTL code

- Compilation & translation

- Generates technology independent netlist

- RTL schematic (HDL code analysis)

- Technology mapping

- Mapping to technology specific structures:

- Look-up tables (LUT)

- Registers

- RAM/ROM

- DSP blocks

Other device specific components/features

Logic optimization

Implementation analysis (technology view)

### FPGA fitter

- Tools supplied by the FPGA vendor

- Specific for each FPGA device architecture

## Functions

- Place-and-route

- Constraints editor

- Backannotated netlist for timing simulation

- Configuration bitstream

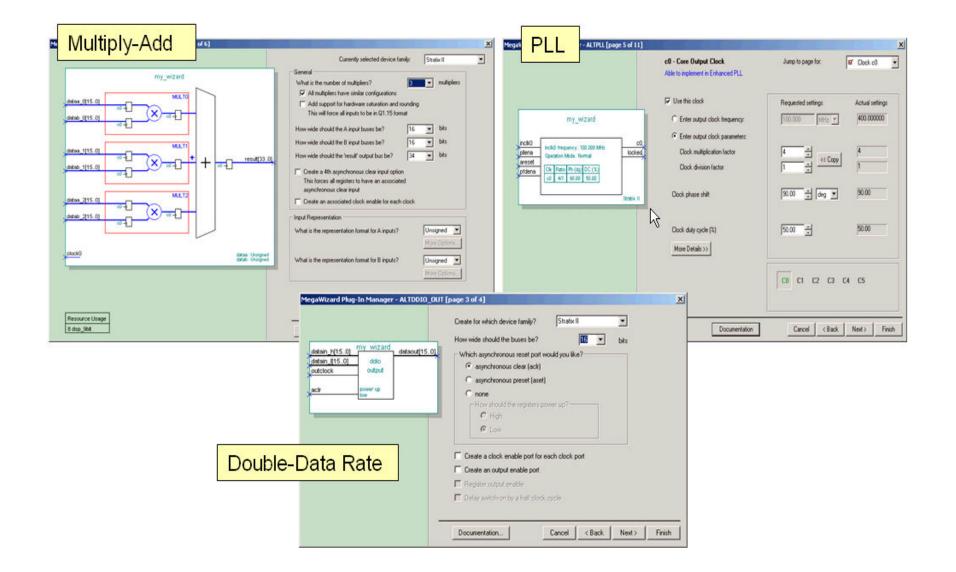

### Macros:

- Generic pre-made design blocks:

- e.g. PLL, FIFOs, DDR I/O, Multiply-accumulate, etc.

- Accelerate design entry and verification

- Pre-optimized for FPGA vendor architecture

- Provided at no cost by the FPGA vendor to optimize performance

- Instantiate block in the design:

- Makes HDL code technology dependent

### IP cores:

- More complex blocks: PCI-X interface, CPU, etc.

- Some are provided by the FPGA vendor

- IP cores from third party suppliers cost money

- Evaluation before buying usually possible

## **Macro Example**

# Many ready-made blocks for free

RAM/FIFO

UART

Can buy ready-made parts, just like IC's: IP Cores

- PCI interface

- Processors (8051-style up to RISC/ARM processors)

- FPGA's with extra dedicated hardware built-in

- Gigabit serialiser

- high-end processor with RAM

Handle different I/O standards

- LVDS, LVPECL, LVCMOS, LVTTL, PCI, PCI-X

- Programmable slew-rate, termination resistors

# **Trend in design tools**

- Trying to design at a higher level of abstraction

- Starting from C/C++ or SystemC code

- Electronics for non-electronicians?

# **Sources of information**

### CERN technical training ELEC 2005: http://indico.cern.ch/conferenceDisplay.py?confld=62928

- Covers a lot of subjects, including optical links, EMC, description of experiments readout systems

- Includes a lot of references to books

- LEB/LECC/TWEPP workshops from last 12 years: http://lhc-electronics

- workshop.web.cern.ch/lhc%2Delectronics%2Dworkshop/

- Detailed presentations and wider plenary talks

- PH-ESE seminars:

- http://indico.cern.ch/categoryDisplay.py?categId=1591

- Previous summer student lectures

- LHC (ATLAS and CMS) upgrades: ACES meeting

http://aces.web.cern.ch/aces/