## Development of a MAPS detector prototype for the BESIII inner tracker upgrade

Mingyi Dong<sup>1,2,3</sup>, Xudong Ju<sup>1,2</sup>, Xiaoxu Lu<sup>1,2</sup>, Xingcheng Tian<sup>1,2</sup>, Xiaoyan Ma<sup>1,2</sup>, Jing Dong<sup>1,2</sup>, Chaoyue Qu<sup>1,2</sup>, Hongyu Zhang<sup>1,2</sup>, Linghui Wu<sup>1,2</sup>, Xiaoshan Jiang<sup>1,2</sup>, Qun Ouyang<sup>1,2,3</sup>, Meng Wang<sup>4</sup>

> 1 Institute of High Energy Physics, Chinese Academy of Sciences, Beijing 100049, China 2 State Key Laboratory of Particle Detection and Electronics, Beijing 100049, China 3 University of Chinese Academy of Sciences, Beijing 100049, China 4 Shandong University, Jinan 250013, China

The Beijing Spectrometer III (BESIII) is a high precision detector for the Beijing electron-positron collider II (BEPCII), a high luminosity, multibunch et et collider running at the tau-charm energy region. The drift chamber (MDC) is the main tracking detector of the BESIII, used for accurate measurements of the position and momentum of charged particles produced in e+ e- collisions, and charged particle identification by measuring dE/dx.

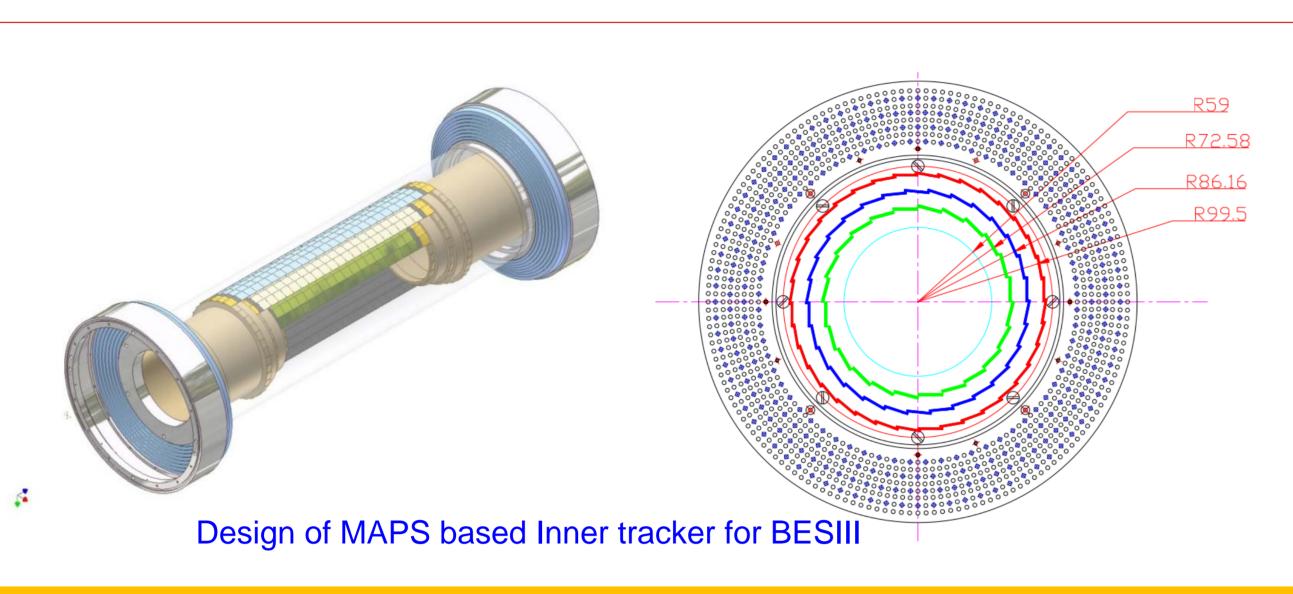

After it has been running 8 years, the MDC is suffering from the aging problems due to huge beam induced background, which caused the cell gains dropped dramatically (39% for the first layer cells), and further more led to decreases of the spatial resolution and the reconstruction efficiency. In order to ensure the inner chamber can be replaced in case of radiation damage, besides building an improved new inner drift chamber, a MAPS (monolithic active pixel sensor) detector prototype, 1/10 coverage of the inner drift chamber, is selected as one of the pre-research schemes, due to its quite attractive features of low material budget, low power consumption and high spatial resolution. The prototype is composed of three layers of MAPS detector modules (ladder), covering 1/10 of the inner chamber in r-φ section, and full length of the inner chamber in z direction. We present the chip test, the design, the assembly and the test of the ladder, as well as the development of the readout electronics.

Prototype layout:

- > 1/10 Coverage of the inner tracker (~ 720cm<sup>2</sup>→180 chips→ about 180M pixels)

- > 3 layers of MAPS prototype

- > 18 ladders r-φ section: 2, 3, 4 ladders in each layer

- > 10 Mimosa28 chips / Ladder (chips were developed by IPHC, Strasbourg)

z direction: 2 sets of ladders in each layer

# Chip probe test Yield and wafer map Chip probe test system Mean 0.2297 Threshold voltage/mv FPN distribution of the wafer **ADC** difference distribution

In order to select good chips and provide a reference for the parameter configuration of the chips when they are working in the detector, a MAPS chip probe testing system was set up for the chip functional check and preliminary performance test. With this probe test system, the JTAG communication, the power consumption and the clamping voltage of the chips were test, as well as the data format of the chip output. We also performed the noise level test of the chips and the threshold scan of the discriminators.

6 wafer chips were tested, and typical chip yield is about 65%.

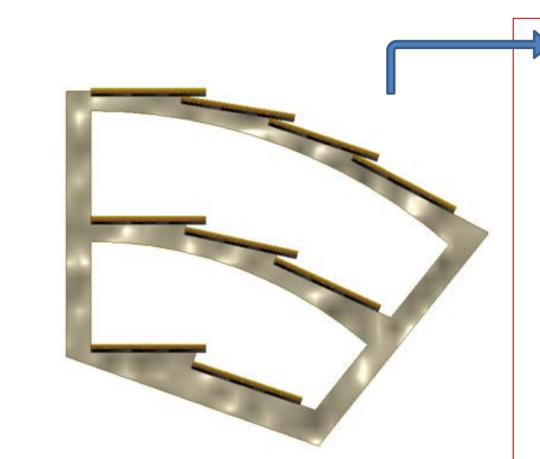

# Ladder assembly Ladder assembly Wire bonding Mimosa28 chips (50µm) 17.8µm Cu(×0. PMI foam (equivalent

Ladder is the basic structural and functional block of the detector, consisting of 10 Mimosa28 chips thinned to 50µm, a flex cable and a carbon fiber supporter. Pixel chips in a row are connected to the flex cable by wire bonding, and then glued to the carbon fiber support frame, which provides stable mechanical support.

Ladder assembly was operated at a special platform to ensure the location accuracy of the chips, and realize the integration of the chip, the flexible cable and the carbon fiber supporter.

Low material (0.37% X<sub>0</sub> / ladder), high precision (chip location precision on the ladder: < 10µm) ladders were achieved.

### Readout electronics and DAQ System Monitor FMC for log files Functional modules of the DAQ Schematic of readout electronics

- A distributed electronics readout system has been developed

- ➤ Ladder → FCB → Readout Board → Switching → PC

- > SiTCP based Gigabit Ethernet (IP core embedded in FPGA) data transmission

- Each electronics module is a network node

- > UPD protocol: transfer run control commands and chip/electronics configuration information

- > TCP/IP protocol: transfer electronics raw data

- Data readout rate: ~700Mb/s

#### Ladder preliminary test by radiation source

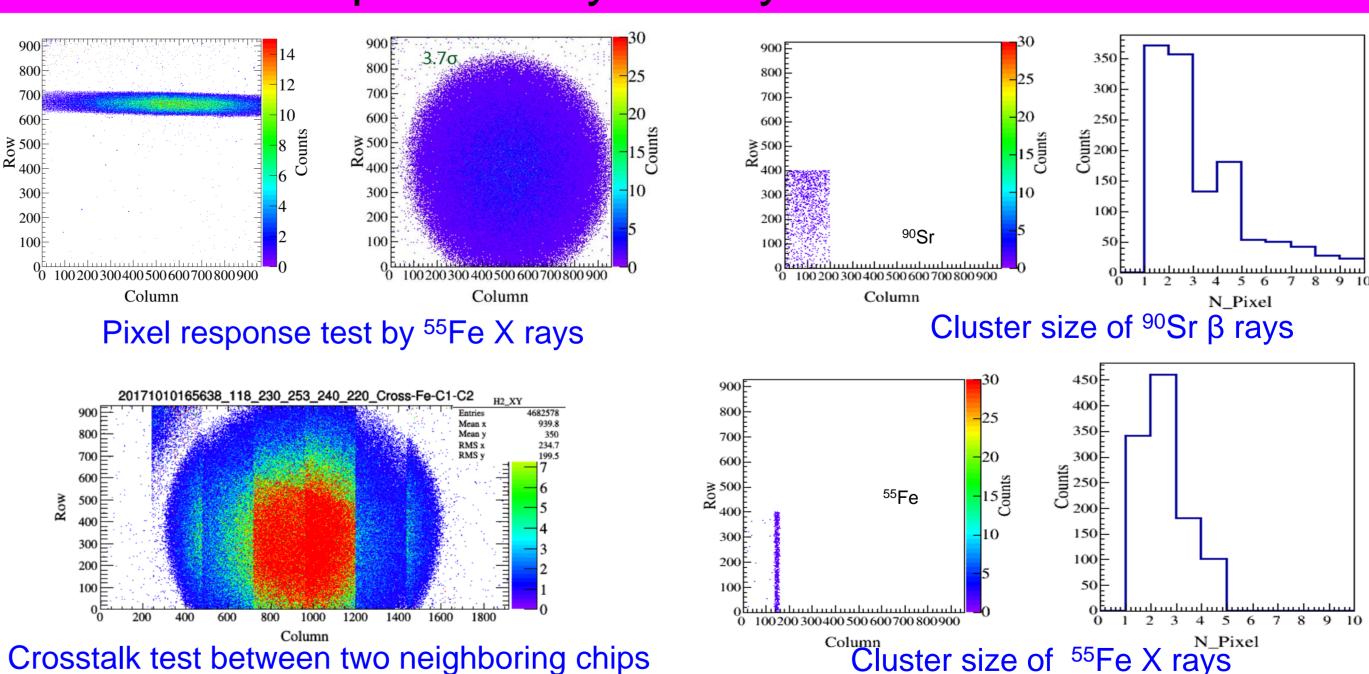

The ladders together with the readout electronics were test by <sup>55</sup>Fe X rays and <sup>90</sup>Sr β rays. The threshold scan, the crosstalk, the imaging performance, temperature effect on the noise level were studied. We also studied the hit reconstruction algorithm.

The test results show that both the ladder and readout electronics work well, and the preliminary results are consistent with the expectation, which meet the requirements of the BESIII inner tracker.

The ladder beam test will be performed next year.