# Fabrication of silicon-supported germanium blocked impurity band detectors for infrared astronomy Otakabira ISHIMARII, Takabika WADA(ISAS(IAVA), Akibira MIVACHI(NACI)

OTakahiro ISHIMARU, Takehiko WADA(ISAS/JAXA), Akihira MIYACHI(NAOJ), Kentaroh WATANABE(The Univ. of Tokyo), Hidehiro KANEDA, Toyoaki SUZUKI(Nagoya Univ.)

## Introduction

Far infrared(FIR) wavelength (30 - 200  $\mu$ m) is important spectral window to study the formation of planets, stars and galaxies.

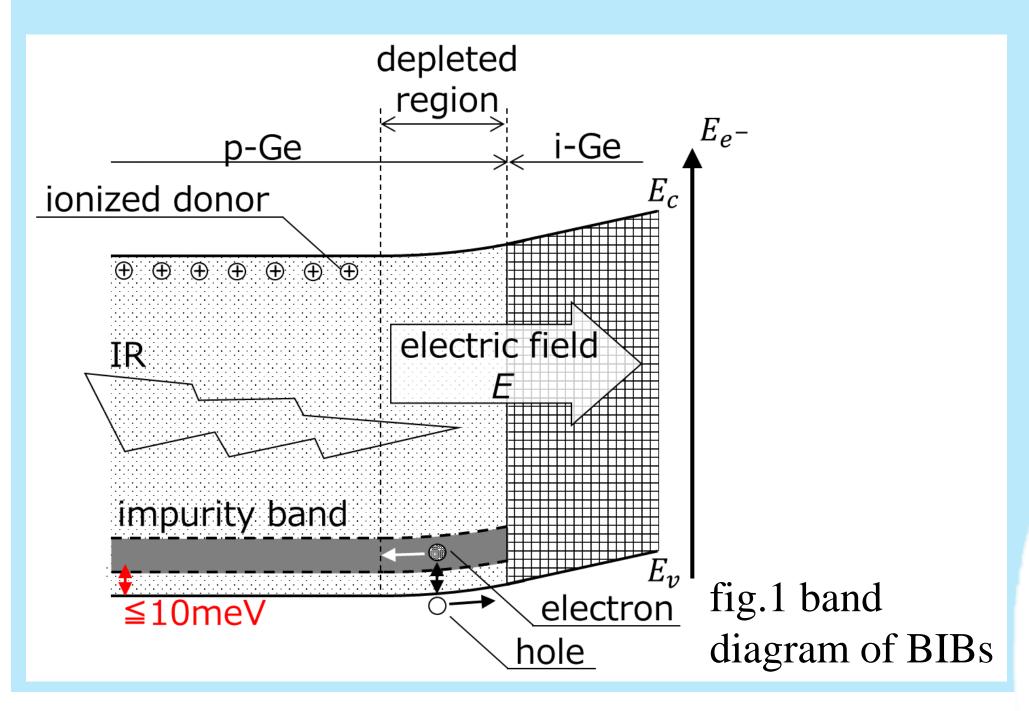

Ge photoconductors(PCs) were used in the previous space IR observations. It is difficult, however, to develop **large format FIR image sensors** because stress mechanism is required to extend their cut-off wavelength λc to FIR photons. To overcome this problem we are developing **germanium Blocked Impurity Band detectors (Ge BIBs)** which respond FIR photons without stress mechanism (see fig.1 for photo detection mechanism).

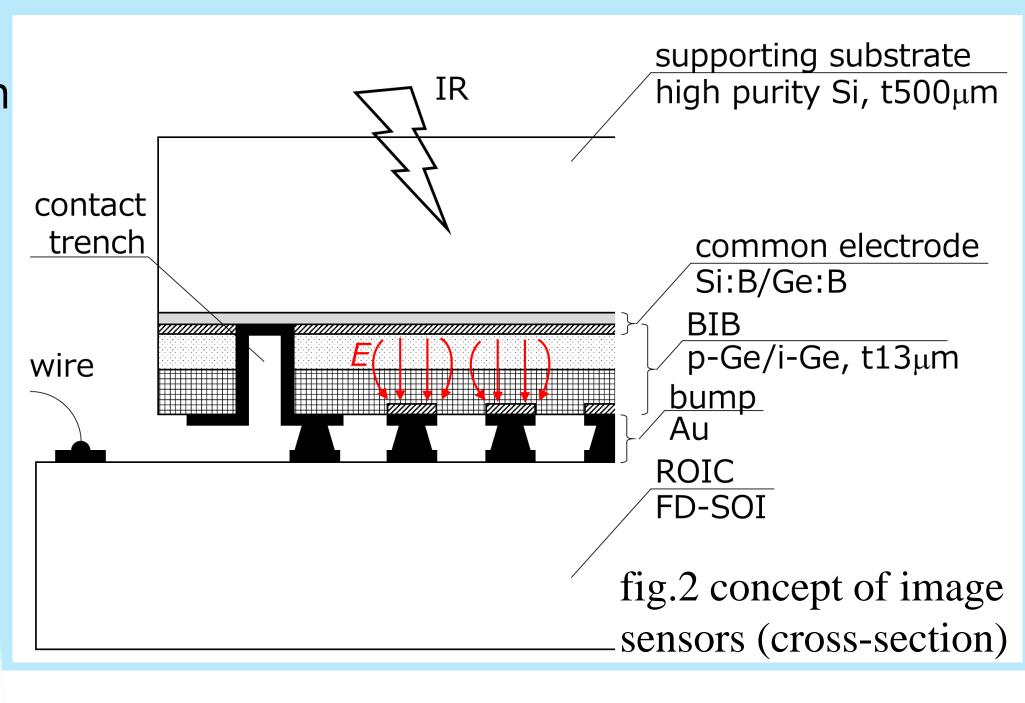

We have proposed the Ge BIB-based FIR image sensor consisted of the Ge BIB array, **FD-SOI read-out integrated circuit (ROIC)** and **nano-particle deposition(NpD)** Au **bump** (see fig.2). This poster is focused on a conceptual design and fabrication of the BIBs.

# Fabrication of Wafers

Wafers ( $\phi$ 50.8mm, t500 $\mu$ m)

Si high purity Si

p-Ge Ge:Ga (Ga concentration of 4x10<sup>16</sup>/cc)

i-Ge high purity Ge

#### Key technologies

- -surface activated bonding(SAB) at room temperature

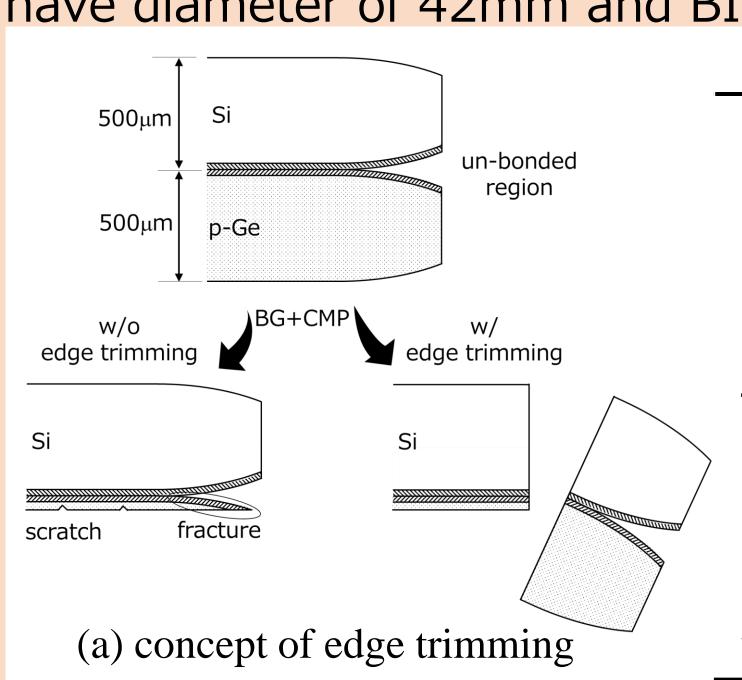

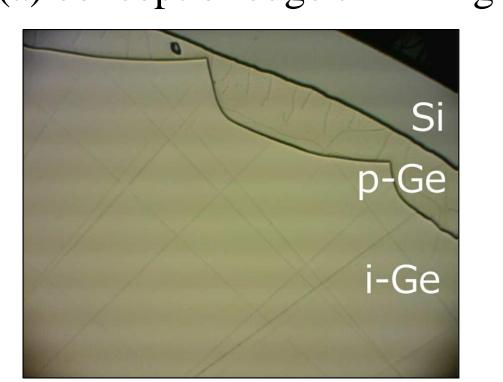

- -back grinding(BG) and chemical mechanical polishing(CMP) -edge trimming(see fig.3)

trimming the un-bonded region to protect surface from fractured Ge particles during CMP

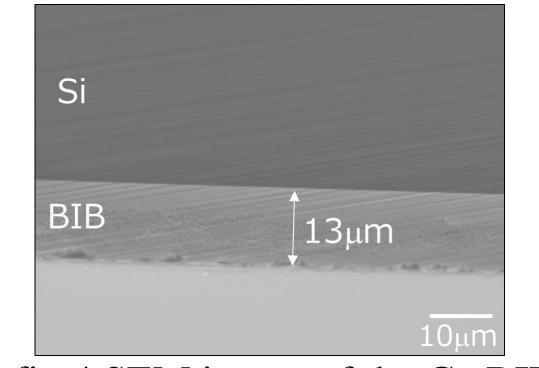

## Result(see fig.4)

we succeeded in fabrication of Ge BIB on Si wafers which have diameter of 42mm and BIB layer thickness of 13um.

table 1 Wafer fabrication

- 1 B+ implantation to Si and p-Ge for common electrode

- 2 SAB of Si and p-Ge

- 3 Edge trimming

- 4 BG+CMP of p-Ge

- 5 SAB of thinned p-Ge of Si/p-Ge and i-Ge

- 6 Edge trimming

- 7 BG+CMP of i-Ge

(b) surface of w/o edge trimming sample fig.3 edge trimming

fig.4 SEM image of the Ge BIB on Si wafer (cross-section)

# Conceptual Design

## Si-supported structure(see fig.2)

Si-supported Ge BIBs structure is employed to mitigate the CTE\*1 mismatch between Ge-based BIBs and Si-based ROICs under operating temperature of 2 K.

## Pixels separation

| pixel isolation   | individual electrode | process                 |

|-------------------|----------------------|-------------------------|

| by electric field | i-Ge side            | masked ion implantation |

| by mesa structure | p-Ge side            | dry / wet mesa etching  |

Separation by electric field is employed.

#### Common electrode

Common electrode is required **high transmittance** for FIR photons in addition to electrical properties. **B ion implanted Si and Ge** layers can be satisfied the requirements through design of density depth profile of implanted B ions and estimation of electrical and optical properties of them.

\*1: coefficient of thermal expansion

# Fabrication of Detectors

#### Fabrication procedure

Ge BIB on Si wafers are processed into detectors array in accordance with the procedure summarized in table 2.

Key process - Contact trench etching

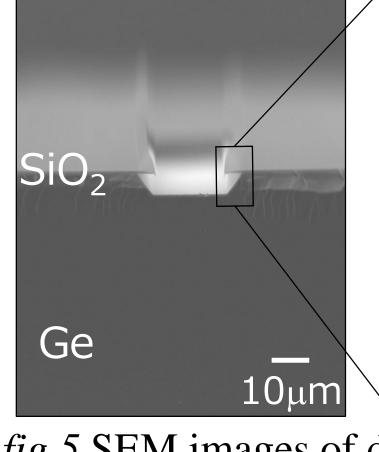

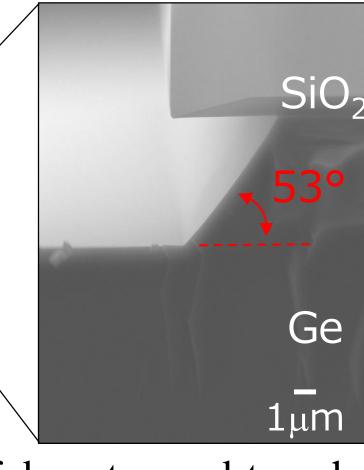

Deep (> $10\mu$ m) and tapered trenches were formed by anisotropic wet etching with  $H_3PO_4+H_2O_2+C_2H_5OH$  mixed solution (fig.5). The solution does not etch Si; therefore, B doped Si surface will be exposed as bottom of the trenches.

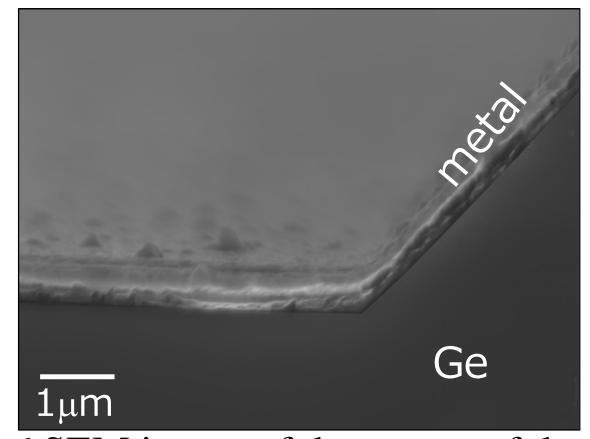

Tapered structure made it easy that metal films contact to the bottom and the corner of the trenches (fig.6).

### **Result**(see the picture in center of this poster)

It was confirmed that the devices is fabricated as designed through electrical continuity checks, resistance measurements between some electrode pads, at room temperature.

#### table 2 Detector fabrication

- 1 Wafer cleaning by HF

- 2 SiO<sub>2</sub> masked B+ implantation for individual electrodes

- 3 SiO<sub>2</sub> re-deposition as capping layer for thermal annealing

- 4 Thermal annealing

- 5 SiO<sub>2</sub> re-deposition as etching mask of contact trench etching

- 6 Contact trench etching with H<sub>3</sub>PO<sub>4</sub>+H<sub>2</sub>O<sub>2</sub>+C<sub>2</sub>H<sub>5</sub>OH

- 7 SiO<sub>2</sub> re-deposition as surface passivation layer

- 8 Al/Ti/Au EB-evaporation

- 9 Lift-off

- 10 Dicing

fig.5 SEM images of deep-tapered-trench

fig.6 SEM image of the corner of deeptapered-trench covered with metal

# Future Works

The 32x32 pixel format image sensors are going be fabricated through bumping process of Ge BIBs and FD-SOI ROICs, and then opto-electrical properties of them will be characterized at cryogenic temperature. The 5x5 pixel arrays will be applied to the balloon astronomical observation for [CII] line ( $\lambda \sim 158 \mu m$ ).