## Radiation Tolerant RF-LDMOS Transistors, Integrated into a 0.25µm SiGe-BICMOS Technology

R. Sorge, J. Schmidt, F. Reimer, Ch. Wipf, F. Korndörfer, R. Pliquett and R. Barth

Abstract- Mixed signal on-chip solutions for space applications and high energy physics experiments require high voltage RF-LDMOS transistors with sufficient ruggedness against ionizing radiation and single event burnout. We report on a novel hardening by design approach for radiation tolerant integrated RF NLDMOS transistors confirmed by single event burn out (SEB) and total ionizing dose (TID) radiation tests. In order to substantially decrease TID induced leakage currents the shallow trench isolation (STI) of MOS transistors was replaced by narrow junction isolated regions. For a significant increase of the SEB onset voltage a cascode arrangement consisting of an isolated NMOS and NLDMOS was chosen. The floating NMOSdrain/NLDMOS-source node in the cascode arrangement is always reverse biased what efficiently avoids a turn-on of the parasitic npn bipolar transistor. The rad-hard isolated NMOS/NLDMOS cascode features a breakdown voltage BVDS > 50 V, a maximum cut off frequency  $f_T = 5$  GHz and a maximum oscillation frequency  $f_{MAX} = 14$  GHz. In comparison NLDMOS with standard transistors the isolated NMOS/NLDMOS cascode device shows an increase of the SEB onset voltage from 14V to 30V at a linear energy transfer LET of 67.7 MeVcm<sup>2</sup>/mg and a negligible increase of source drain leakage currents up to a TID of 1.5 Mrad after irradiation with a <sup>60</sup>Co source.

*Index Terms*— Radiofrequency integrated circuits, Power MOSFET, Total ionizing dose, Radiation hardening (electronics)

## I. INTRODUCTION

**Z**EY challenges for integration of RF LDMOS transistors Ninto highly scaled CMOS processes with a thin gate oxide are good RF performance, high break down voltage, low on resistance and small device parameter degradation due to hot carrier injection (HCI) [1]. RF-LDMOS power transistors are key components in highly efficient DC/DC converter circuits for integrated power management solutions in space applications and high energy physics experiments [2,3]. Similar to their NMOS transistor counterparts NLDMOS transistors also suffer from parameter degradations due to TID related leakage paths between source and drain originating from positive charges trapped in the thick oxide of the lateral STI region. As a second source of device malfunction the generation of electron hole pairs in the active device region during irradiation with charged high energy particles leads temporarily to a dramatic increase of the substrate current which can finally turn on the parasitic npn bipolar transistor. The resulting

All Authors are with IHP, Im Technologiepark 25, 15236 Frankfurt(Oder), Germany.

thermal runaway can finally destroy the NLDMOS transistor. We address the radiation induced malfunctions of NLDMOS with a novel hardening by design (HBD) approach without process changes. The fabricated devices were evaluated by DC-, RF-S-parameter-, 1/f noise measurements. TID and SEB radiation tests were performed on standard NLDMOS (NLD\_ST), NLDMOS with lateral junction isolation (NLD\_JI) and an isolated NMOS/NLDMOS cascode with lateral junction isolation (NLD\_CA) as the proposed target device construction.

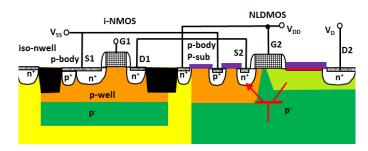

## II. DEVICE

Two constructive measures were applied for improvement of TID and SEB immunity of NLDMOS transistors. First, we introduced a lateral junction isolation to suppress the strong increase of source drain leakage in NMOS transistors after irradiation with a <sup>60</sup>Co source. Secondly an isolated NMOS/LDMOS cascode arrangement was used to substantially increase the SEB onset voltage. Fig. 1 shows the cross section scheme of the isolated NMOS/NLDMOS cascode arrangement. The increase of the SEB onset voltage relies on the fact that the common floating node of drain D1 and source S2 is always weakly reverse biased. This prevents that the base emitter junction of the NLDMOS parasitic npn gets forward biased, so that the blocking properties of the parasitic npn transistor can be maintained under irradiation with high energetic heavy ions.

Figure 1: Cross section A'-A" of isolated NMOS/NLDMOS cascode device (NLD\_CA) according to the layout in Figure 4.

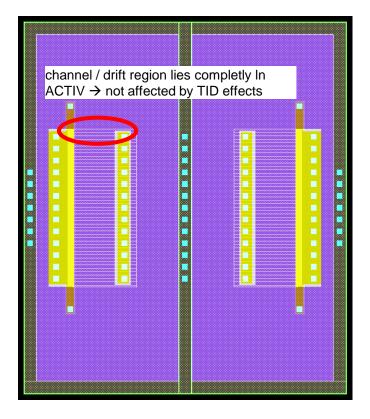

Figure 2 shows a standard NLDMOS (NLD\_ST) layout with two gate fingers and STI isolation in the lateral channel regions. In the layout shown in Fig 3 the lateral STI isolation of the channel regions was replaced by junction isolation to prevent the source drain leakage resulting from the influence of trapped fixed positive charge in the thick STI layers after exposure of the device to ionizing radiation. Note, that the whole device lies now completely in ACTIVE silicon and the poly silicon gate contacts are located also in the ACTIVE region.

# channel / drift region affected by TID effects STI ACTIV

Figure 2: Layout of standard STI isolated NLDMOS (NLD\_ST) with two gate fingers (color legend see Figure 4).

Figure 3: Layout of NLDMOS (NLD\_JI) with lateral junction isolation (two gate finger device, color legend see Fig. 4).

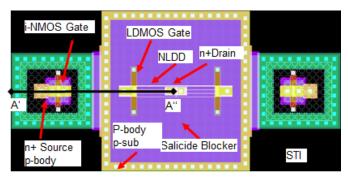

The combination of these device construction measures, i.e. isolated NMOS/NLDMOS arrangement and lateral junction isolation, yields a substantial increase of the radiation hardness of LDMOS power devices in terms of TID and SEB. Fig 4 depicts a layout of the isolated NMOS/NLDMOS cascode arrangement corresponding to the cross section scheme of Fig 1. As shown in Fig. 4 lateral junction isolation (see Fig 3) instead of STI isolation is realized for both the isolated NMOS and the NLDMOS.

## III. EXPERIMENTAL

In order to compare the vulnerability of the several LDMOS device constructions against radiation effects a standard STI isolated NLDMOS (NLD\_ST) , a NLDMOS (NLD\_JI) with lateral junction and an isolated NMOS/NLDMOS cascode arrangement with lateral junction (NLD\_CA) (see Figs 2,3,4) were prepared in one process flow using IHP's 0.25  $\mu m$  SiGe BCD technology SGB25VGDA.

Figure 4: Layout of the target NLDMOS device construction with two gate fingers featuring an isolated NMOS/NLDMOS cascode arrangement with lateral junction isolation (NLD\_CA).

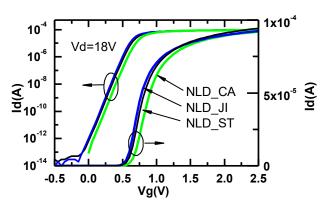

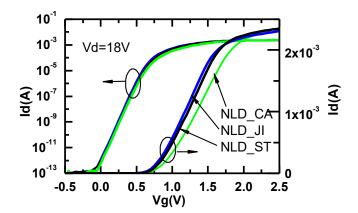

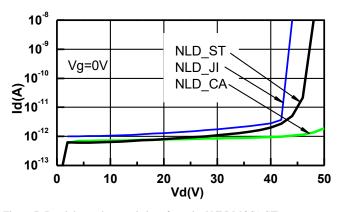

The measured transfer and breakdown characteristics of the NLD\_ST, NLD\_JI and NLD\_CA transistors are depicted in Figs. 5, 6 and 7.

Figure 5: Transfer characteristics at  $V_D$ =0.1 V of standard NLDMOS (\_ST), NLDMOS (\_JI) with lateral junction isolation and isolated NMOS/NLDMOS (\_CA) with lateral junction isolation in linear mode of operation.  $w_G = 10 \mu m$ .

Figure 6: Transfer characteristics at  $V_D$ =18 V of standard NLDMOS (\_ST), NLDMOS (\_JI) with lateral junction isolation and isolated NMOS/NLDMOS (\_CA) with lateral junction isolation in saturation mode of operation.  $w_G = 10 \mu m$ .

Figure 7: Breakdown characteristics of standard NLDMOS(\_ST), NLDMOS(\_JI) with lateral junction isolation and isolated NMOS/NLDMOS (\_CA) with lateral junction isolation .  $w_G = 10 \mu m$ .

There are no significant differences in the DC characteristics of all three devices. An additional potential reliability issue for LDMOS devices is the degradation due to hot carrier injection (HCI). Due to the fact that the gate voltage  $V_{G2}$  of the NLDMOS in the cascode arrangement is connected always with  $V_{DD}$  = 2.5V of the underlying CMOS core the NLDMOS body current is far away from its maximum value at around  $V_G=V_{DD}/2$  what gives a reduced HCI degradation of the NLDMOS. The HCI related degradation of the isolated NMOS transistor in the isolated NMOS/LDMOS cascode arrangement is also very small because it operates always in linear mode with V<sub>DS1</sub> << 2.5 V. The resulting low level of body currents indicate very small HCI induced MOS transistor parameter degradations. Table I shows the maximum drain operation voltage for 10 years lifetime extracted from hot carrier induced drain current degradations in the linear and saturation mode of operation.

The maximum cut off frequency  $f_T$  and the maximum oscillation frequency  $f_{MAX}$  were extracted from S-parameter measurements at  $V_D{=}8~V.$  We obtained for the three devices NLD\_ST: $f_T/f_{MAX}{=}15/34~GHz/GHz},~NLD_JI:~f_T/f_{MAX}{=}15/35~GHz/GHz},~NLD_CA:~f_T_/f_{MAX}{=}5/14~GHz/GHz}.$

## Table I

## $\label{eq:maximum} \begin{array}{l} \text{Maximum drain voltage for 10 years lifetime} \\ \text{extracted from hot carrier injection related drain} \\ \text{current degradation } \Delta \text{ID}/\text{ID0} < 0.1 \text{ in linear}(\text{IDLIN}) \\ \text{and saturation}(\text{IDSAT}) \text{ mode of operation at 100\%} \\ \text{duty cycle} \end{array}$

| Device                                                                  | IDLIN | IDSAT |

|-------------------------------------------------------------------------|-------|-------|

| Standard NLDMOS<br>(NLD_STA)                                            | 22 V  | 21 V  |

| NLDMOS, lateral junction isolation (NLD_JI)                             | 23 V  | 21 V  |

| Isolated NMOS/NLDMOS<br>Cascode, lateral junction isolation<br>(NLD_CA) | 36 V  | 33 V  |

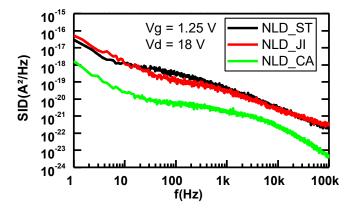

Figure 8: 1/f (Flicker) noise of standard NLDMOS (\_ST), NLDMOS with lateral junction isolation (\_JI) and isolated cascode NMOS/NLDMOS with lateral junction isolation (\_CA).

Fig. 8 shows the results of 1/f (Flicker) noise measurements for the three investigated LDMOS devices performed with the AdMOS 3001B Flicker Noise Measurement System. STI and junction isolated LDMOS transistors exhibit a similar noise performance. In contrast, the isolated NMOS/NLDMOS cascode configuration shows a significantly decreased 1/f (Flicker) noise.

## IV. RADIATION TESTS

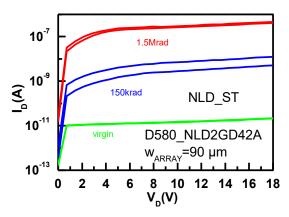

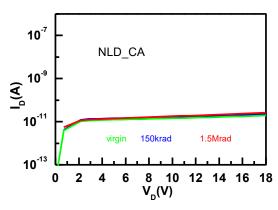

We have evaluated the radiation hardness in terms of TID and SEB for a standard NLDMOS, a NLDMOS with lateral junction isolation and an isolated NMOS/LDMOS cascode arrangement with lateral junction isolation. The TID tests were performed at a dose rate of 10 krad(Si)/h, using the <sup>60</sup>Co source at the Helmholtz Zentrum Berlin (HZB). In contrast to the standard NLDMOS device (see Figure 9) we observed no TID induced increase of source drain leakage for the isolated NMOS/NLDMOS cascode arrangement with lateral junction isolation up to a radiation dose of 1.5 Mrad, which proves the effectiveness of the applied concept of lateral junction isolation

(see Figure 10). The leakage current remains unchanged at a very low level of < 1pA/edge.

Figure 9: Source drain leakage of standard NLDMOS (\_ST,w\_{G,ARRAY} =90  $\mu m$ ) before and after gamma irradiation.

SEB tests were performed in the Accelerator Laboratory at the University of Jyväskylä, Finland. The test conditions for determination of the SEB onset voltage of the NLDMOS devices were:  $131Xe^{+35}$  Xenon ions, energy 1217 MeV, Tilt 0°, LET at the surface 57.36 MeVcm<sup>2</sup>/mg, LET at 57µm depth 67.9 MeVcm<sup>2</sup>/mg, beam fluence  $10^7$ cm<sup>-2</sup>. For the proposed junction isolated NMOS/NLDMOS cascode arrangement (NLD\_CA)) we measured a SEB onset voltage V<sub>SEBTH</sub> > 30V. For the corresponding standard NLDMOS device NLD\_ST and the NLDMOS NLD\_JI with lateral junction isolation we obtained for V<sub>SEBTH</sub> < 14V only.

Figure 10: Source drain leakage of junction isolated NMOS/NLDMOS cascode (\_CA,  $w_{G,ARRAY}$ =180 $\mu$ m).

## V. SUMMARY AND OUTLOOK

A novel radiation hardening by design approach for NLDMOS transistors based on an isolated NMOS/NLDMOS cascode arrangement has been successfully verified. In order to suppress TID induced drain leakage currents in the lateral regions of the MOS transistor channel junction isolation was applied instead of shallow trench isolation. The chosen approach enables the fabrication of radiation tolerant RF LDMOS transistors with blocking voltages > 50 V and a SEB onset voltage > 30 V. The devices were fabricated in IHP's  $0.25\mu$ m SiGe BCD SGB25VGDA process without process changes. In comparison to standard LDMOS transistors the isolated NMOS/NLDMOS cascode transistors with lateral junction isolation show a substantial improvement of radiation hardness in terms of TID and SEB. The substantial improvement of the radiation hardness was achieved together with a good DC and RF device performance, HCI stability and a very low Flicker noise level.

## **ACKNOWLEDGEMENTS**

The authors would like to thank Dr. Andrea Denker and coworkers at Helmholtz Zentrum Berlin for their support in performing the TID irradiation tests of our devices. We also thank Prof. Ari Virtanen and his team at the Accelerator Laboratory at the University of Jyväskylä, for help and valuable discussion during the heavy ions irradiation tests.

### REFERENCES

- K.-E. Ehwald, et al., "High performance RF LDMOS transistors with 5 nm gate oxide in a 0.25 pm SiGe:C BiCMOS technology," in *IEDM Symp. Tech. Dig.*, Dec. (2001), 895

- [2] F. Faccio et al., TID and Displacement Damage Effects in Vertical and Lateral Power MOSFETs for Integrated DC-DC converters, IEEE Trans. Nucl. Sci. 57, (2010) 1790

- [3] F. Faccio et al., "Total ionizing dose effects in shallow trench isolation oxides", Microel. Rel. 48 (2008) 1000.