# The upgrade of LHCb VELO

Kazuyoshi Akiba on behalf of the VELO group

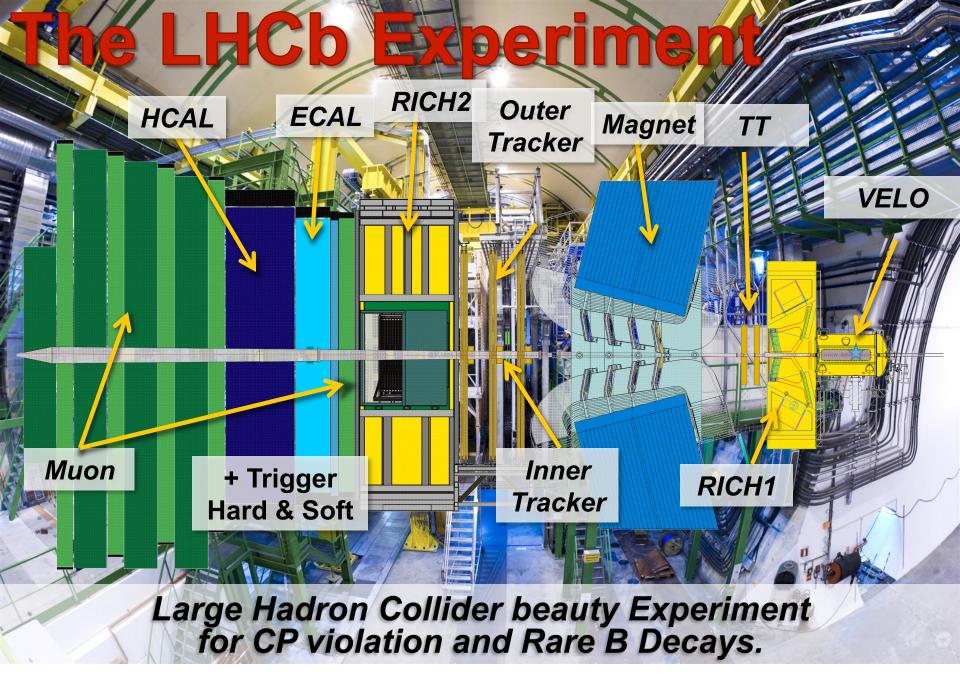

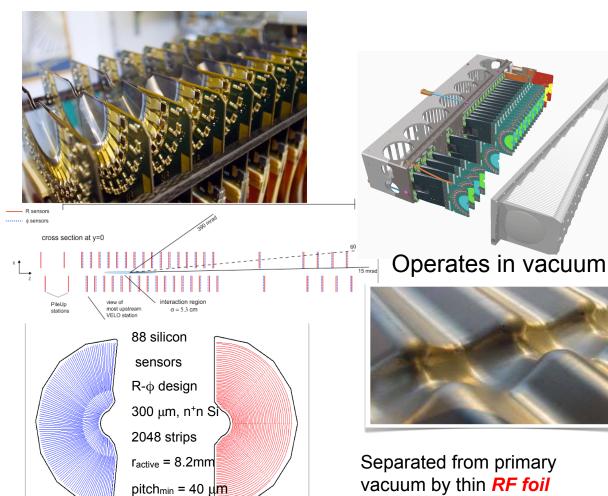

### The current Vertex Locator (VELO):

Moves away every fill and centers around the beam with self measured vertices

with complex shape Protection from beam pickup

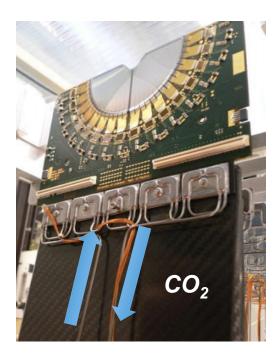

### biphase cooling

**Evaporation** of CO<sub>2</sub> keeps the temperature stable.

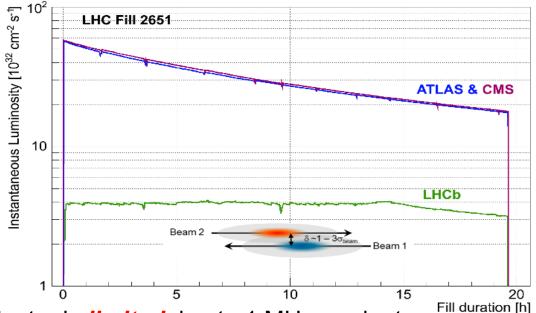

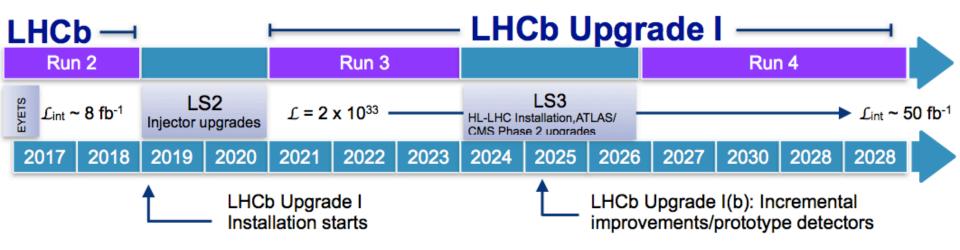

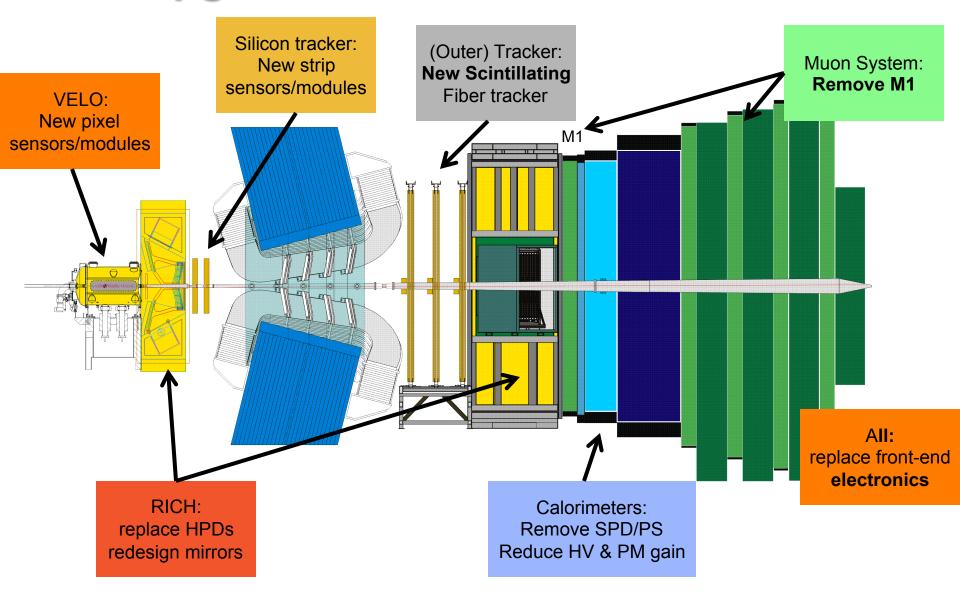

# Why upgrade LHCb – Phase 1 (LS2)

- Currently LHCb can cope with a inst. lumi. higher than design

- LHC still provides more than what we can handle:

- Current detector is limited due to 1 MHz readout.

- Higher Luminosities do not translate to higher physics: need smart Trigger.

- The upgrade is planned as a major Trigger/Readout upgrade:

- From 1 to 40 MHz full readout → Every collision read out to a computing farm

- Higher instantaneous Luminosity → Higher occupancies/Faster Ageing

- Change all the front-end!

### Main challenges for the Velo Upgrade

| Non uniform <i>Radiation</i> exposure | 8 x 10 <sup>15</sup> n <sub>eq</sub> /cm <sup>2</sup> @ tip close to IP,<br>~0.1 x 10 <sup>15</sup> n <sub>eq</sub> /cm <sup>2</sup> @ outer edge |

|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Sensor <u>HV</u> tolerance            | 1000V after 50 fb <sup>-1</sup>                                                                                                                   |

| Readout data <u>rate</u>              | ~33tracks/Event/module.<br>(LHC: 40 MHz/25 ns)                                                                                                    |

| Low <u>Temperature</u> operation      | -20 C @ tip close to the beam                                                                                                                     |

| ASIC power consumption                | 3W/ASIC; up to 36 W/module;                                                                                                                       |

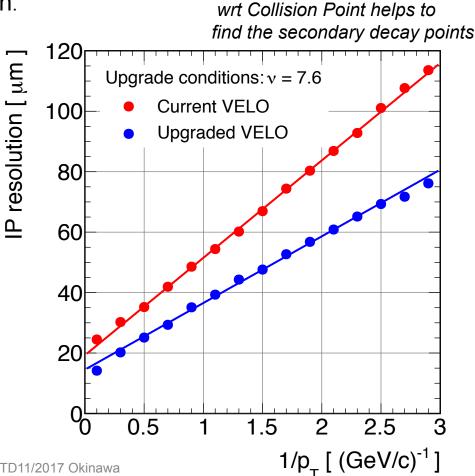

| <i>Material</i> budget                | <ul> <li>Good IP and tracking resolution currently:</li> <li>Proper time resolution ~ 50 fs</li> <li>IP resolution ~ 40 mm (p=1GeV)</li> </ul>    |

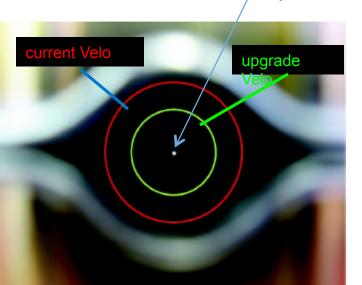

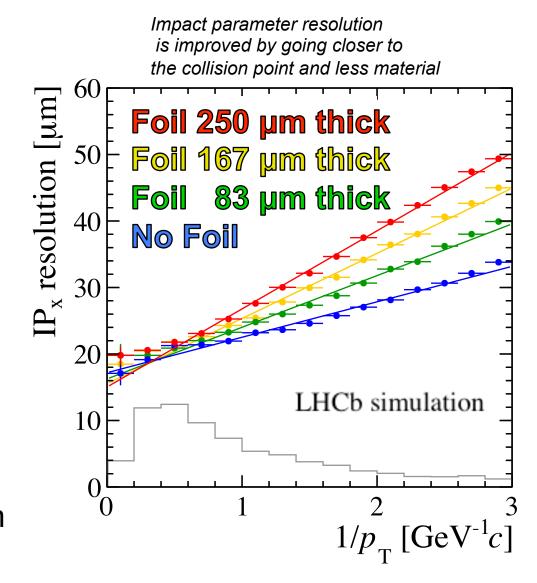

### Changes to improve: Closer, lighter, more segmented

- From strips to pixels: 55x55 μm² pixel.

- Fast and robust pattern recognition. better signal to noise

- Cooling interface needs to come closer to the tip.

- Plan to use <u>μ-channels</u> etched in silicon.

- First active element at 5.1 mm from beam

(was 8.2 mm)

New RF-foil required.

Collision point "proton view"

Impact parameter resolution

### **Upgrade Plan**

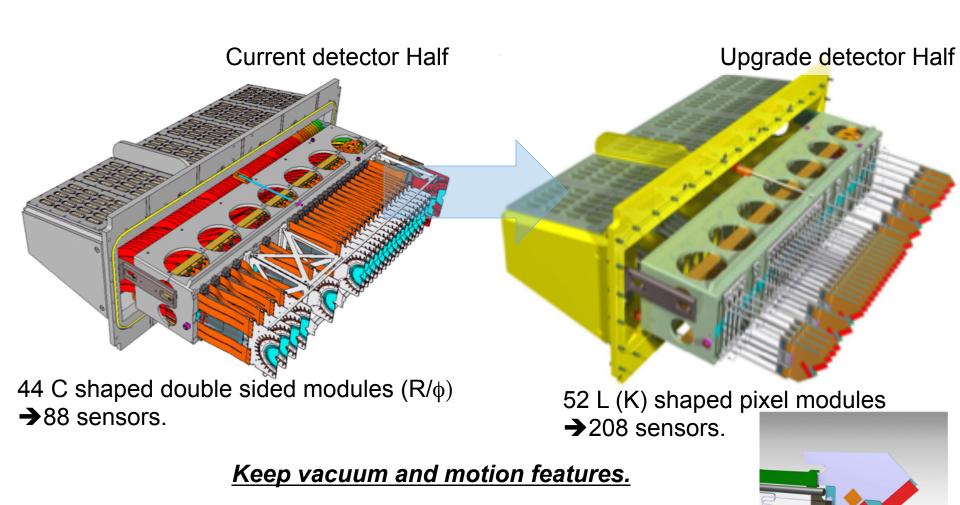

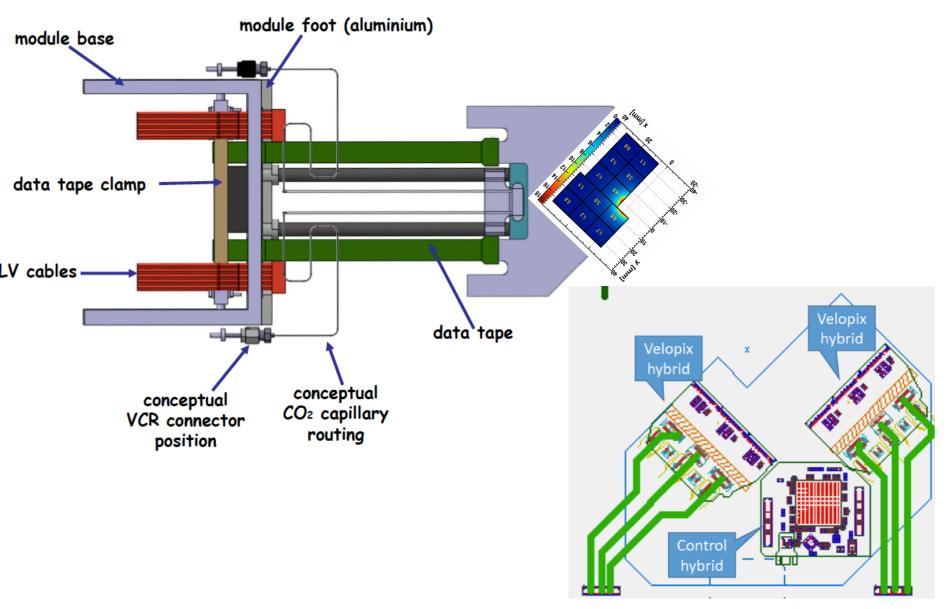

# Modules: 52 @ 25mm pitch (along beam)

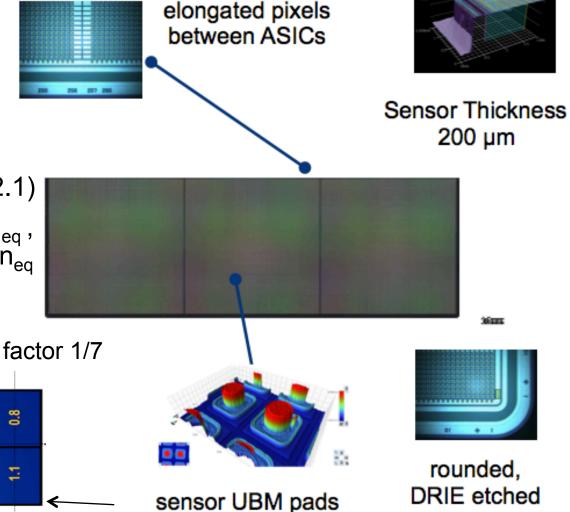

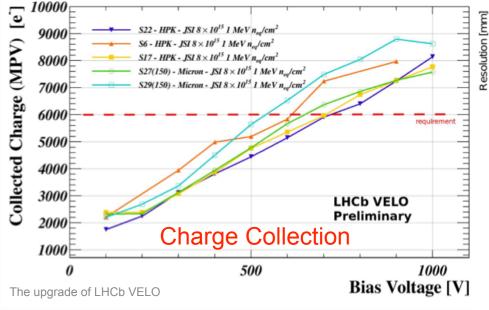

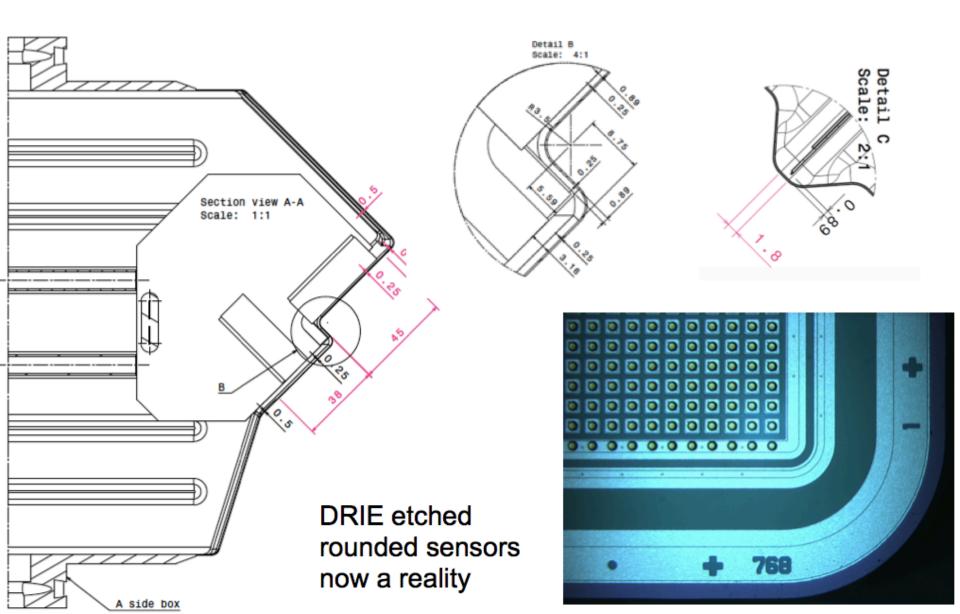

### Silicon sensors

- n-in-p

- Tile for 3 ASIC chips

- 200 μm thick

- 55x55 μm² pixels

- Non uniform irradiation (~ r-2.1)

- Tip close to beam:  $8 \times 10^{15} \, n_{eq}$ , far corner only at  $0.8 \times 10^{14} \, n_{eq}$

- guard ring width ~450 μm

• Bias of 1000V after 50 fb<sup>-1</sup>

factor 1/100

factor 1/20

3.0

corners

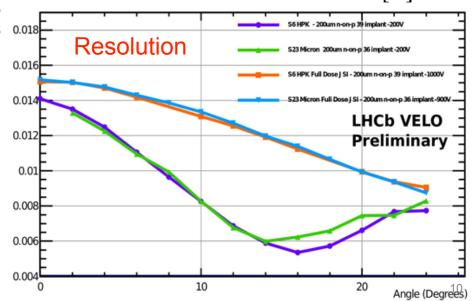

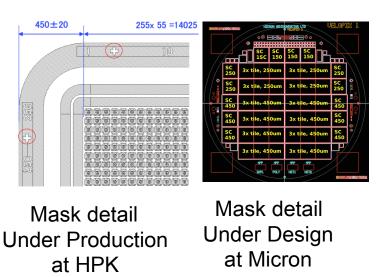

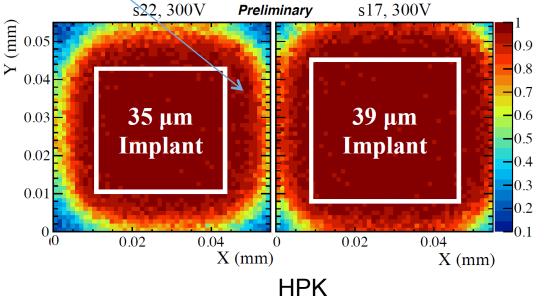

## **Sensor: Prototyping**

|                          | Micron<br>n-on-n    | Micron<br>n-on-p                  | Hamamatsu<br>n-on-p |

|--------------------------|---------------------|-----------------------------------|---------------------|

| Thickness                | 150 µm              | 200 µm                            | 200 µm              |

| Implant size             | 36 µm               | 36 µm                             | 39 μm<br>35 μm      |

| Guard ring pixel to edge | 450, 250,<br>150 μm | <mark>450</mark> , 250,<br>150 μm | 450, 600 μm         |

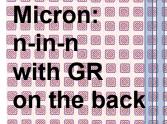

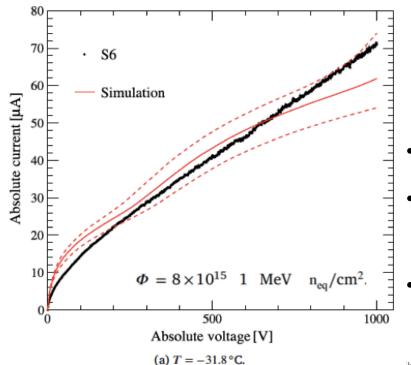

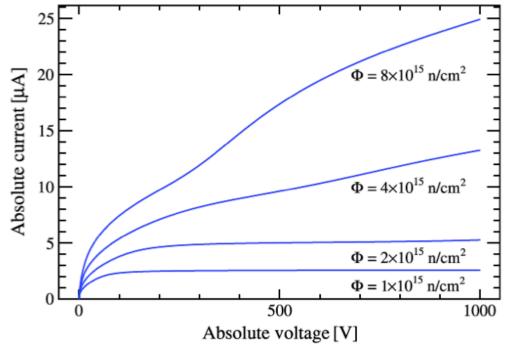

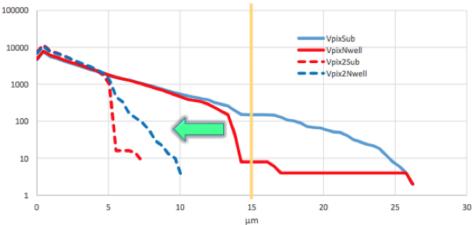

### Current model for irradiated sensors

### need a model

- valid for our irradiation range

- capable of describing the changing IV curves we see

- focus on bulk effects

### Folkestad-LHCb model:

Nucl. Inst. and Meth. A 874 (2017) p94-102

inspired by Perugia and EVL models

contains one donor level, one shallow and one deep acceptor

TCAD simulations show Reasonable agreement with data Linear Increase in current for heavily Irradiated substrates Due to avalanche

### **ASIC Challenges**

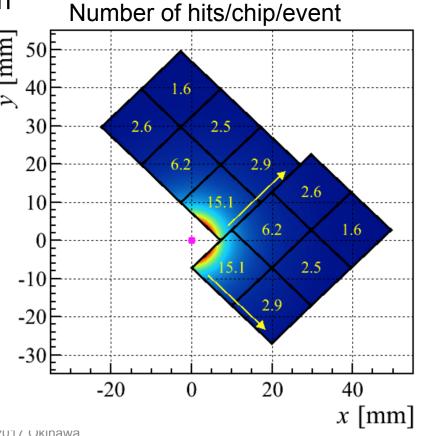

- Average # particles / chip / event

- average (peak) rate: multiply by 26.8 (40) MHz

- Hottest chip →230 (320) Mtracks/s ~ 600 (900) Mhits/s per chip

- grouping of pixel hits

2x4 super pixels → 30 % data reduction

- Output bandwidth of (hottest) VeloPix:

- Average: 13 Gbit/s; peak: 20 Gbit/s

- 4 links at ~ 5 Gbit/s

- High radiation environment:

- SEU protection: triple redundancy

- Extensive tests with heavy lon irradiation

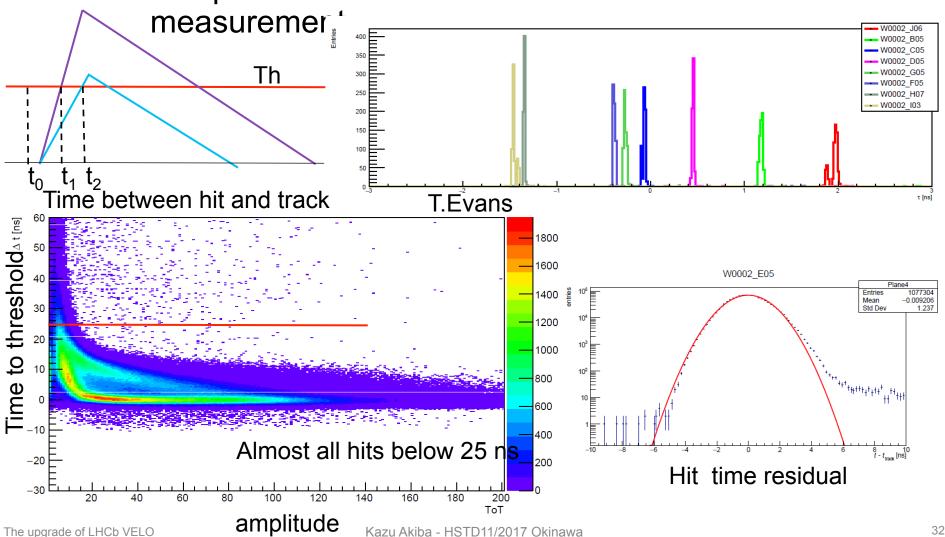

### VeloPix ASIC

- Key features

- Data driven readout: Each hit time-stamped, sent off chip immediately

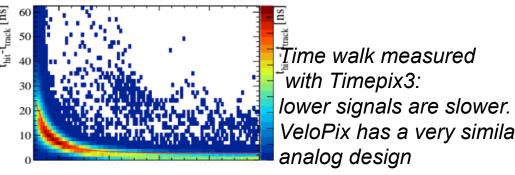

- Fast front-end: *time walk < 25 ns*

- Binary readout but optional Amplitude (slow) for calibration

- Technology (130 nm TSMC)

- Chips will be thinned to 200 µm:

→ minimize material

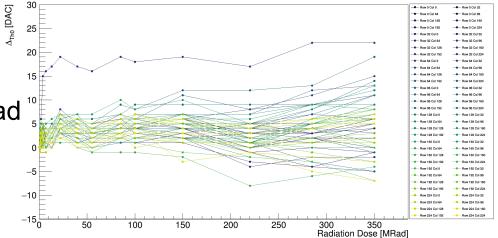

- Test done with X-ray up to 400 MRad

- No change in digital power consumption

- No drift in analogue parameters:

- pixel thresholds, noise and global DACs remain stable

VeloPix Wafer: Probe test station ready

threshold shift w.r.t. 0 Mrad

### Single Event Upset Testing

- determine rate of single event upsets (bit-flips)

- Shoot heavy ions of various type / angles

- Using heavy ion facility in Louvain-la-Neuve

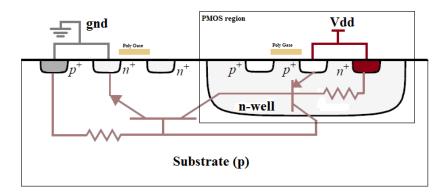

- Single Event Latch-up (SEL): a (local) short circuit on the power lines

- And large x-sec for the reset circuit

- SEL occurs in the matrix only

- strongly temperature dependent, not observed below -10 °C

- though might still occur if tested for longer time

- SEL is due to higher substrate/well resistance in TSMC process.

- Solution: add extra substrate contacts to reduce distance to contact

14

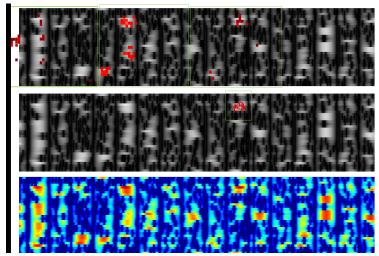

### Laser testing

SEL confirmed by injection of laser light at Montpellier facility

- very precise position of charge injection

- but can not scan whole chip, too many steps (1 or 3 µm step size)

- NIR photons shot into chip from back side

- Local charge injection (also in depth) possible by two photon absorption

- VeloPix2 has these change already implemented.

observed **SEL** 3 um steps

observed **SEL** 1 um steps

design: distance to contact

Distribution of contacts distances

15 The upgrade of LHCb VELO

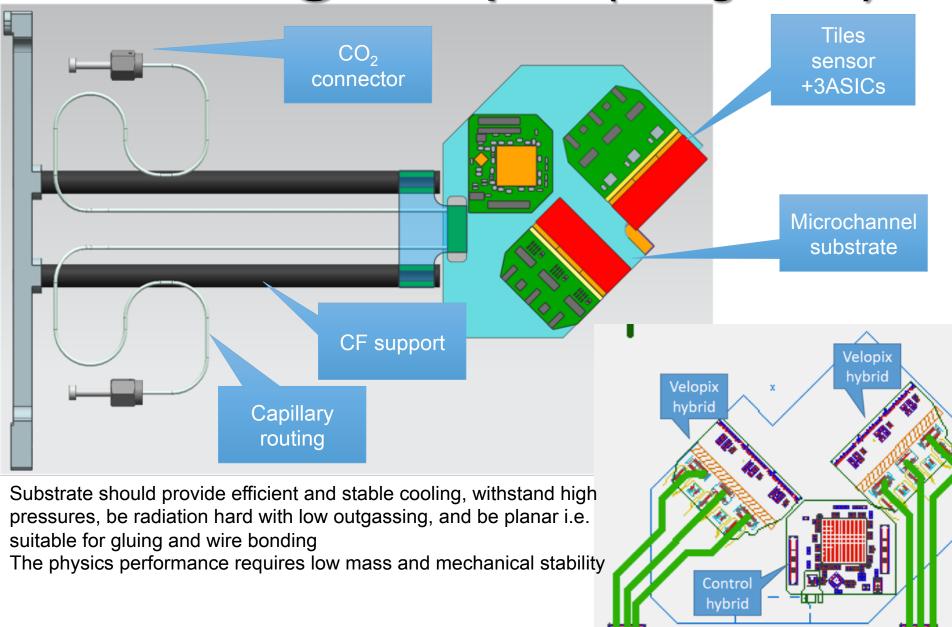

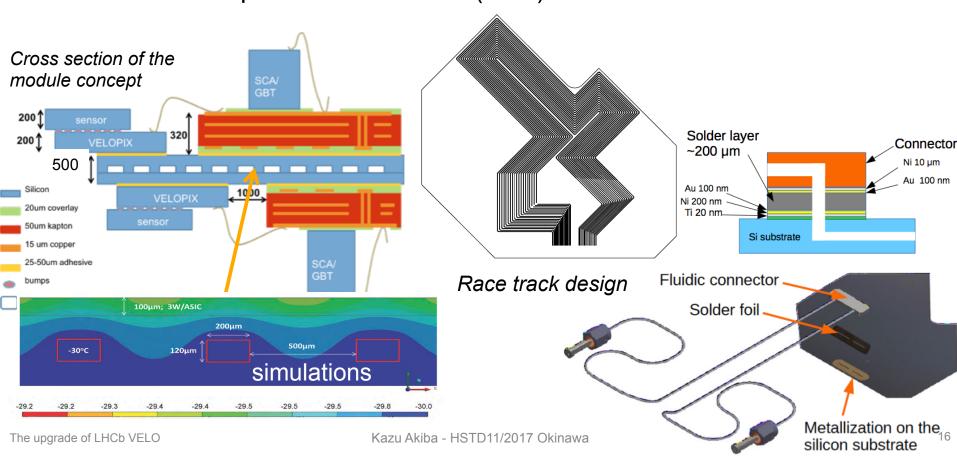

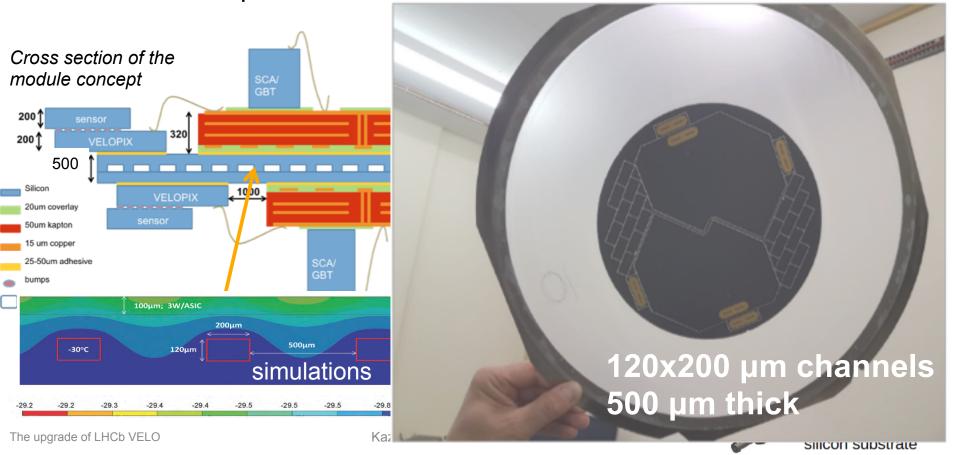

### Cooling: micro channel substrate

- Power consumption can go up to ~40W/module.

- Keep the sensors at < -20 °C to minimize the effects of radiation damage, and avoid thermal runaway

- Novel method: evaporate CO₂ via micro-channels etched in Si substrate →

Same Thermal Expansion Coefficient (CTE)

### Cooling: micro channel substrate

- Power consumption can go up to ~40W/module.

- Keep the sensors at < -20 °C to minimize the effects of radiation damage, and avoid thermal runaway

Novel method: evaporate CO₂ via micro-channels etched in Si substrate →

Same Thermal Expansion Coefficient (CTE)

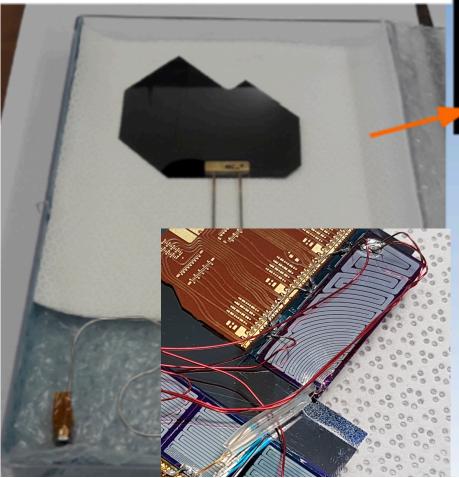

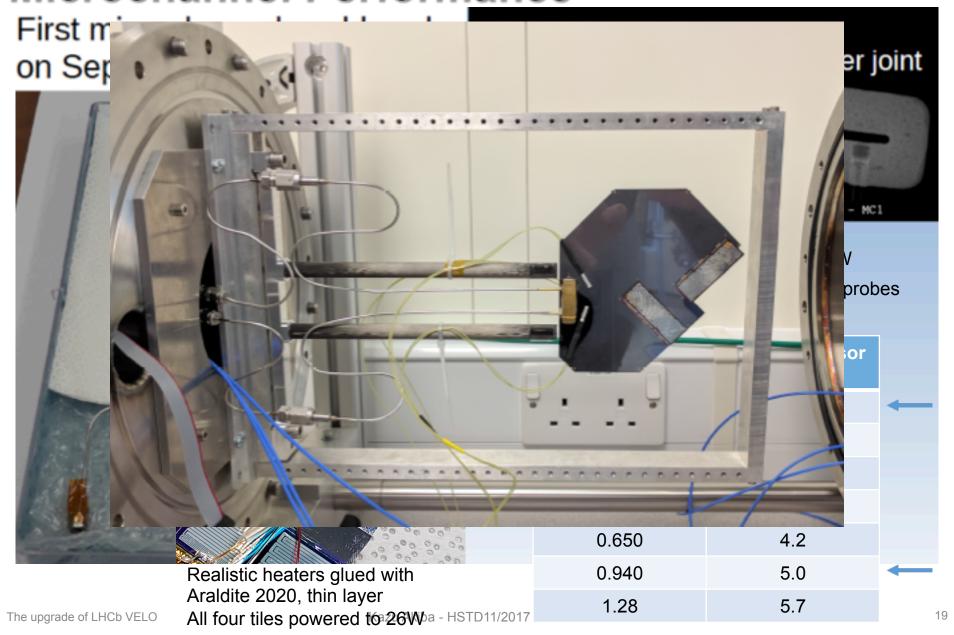

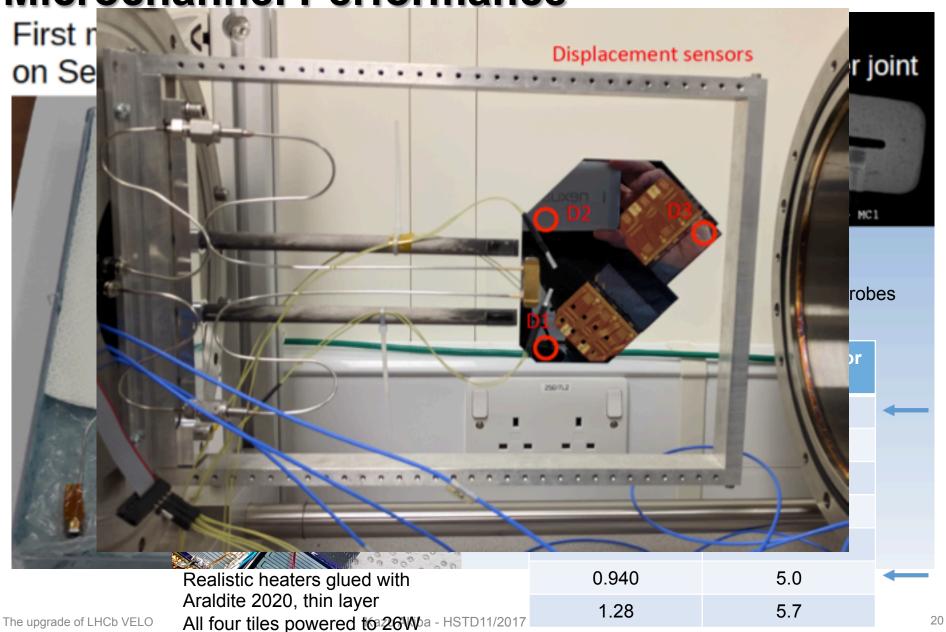

### **Microchannel Performance**

First microchannels soldered on September 1<sup>st</sup> 2017

Realistic heaters glued with Araldite 2020, thin layer

All four tiles powered to 26Wa - HSTD11/2017

- Overhang sensor powered up to 1.3W

- Temperatures measured with PT100 probes

- In vacuum

|   | Sensor Power<br>(W) | dT (C) of Sensor<br>tip |   |

|---|---------------------|-------------------------|---|

|   | 0                   | 2.7                     | 4 |

|   | 0.100               | 2.9                     |   |

|   | 0.240               | 3.3                     |   |

|   | 0.400               | 3.7                     |   |

|   | 0.650               | 4.2                     |   |

|   | 0.940               | 5.0                     | 4 |

| 7 | 1.28                | 5.7                     |   |

|   |                     |                         |   |

### **Microchannel Performance**

Microchannel Performance

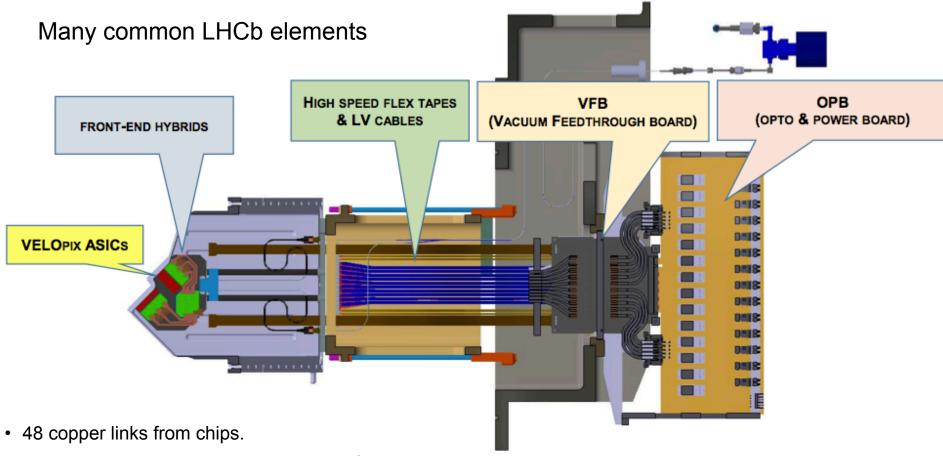

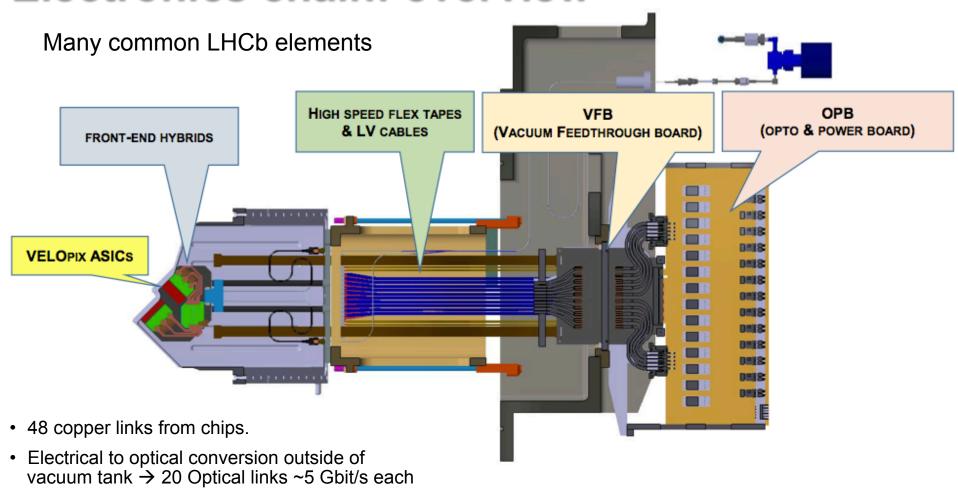

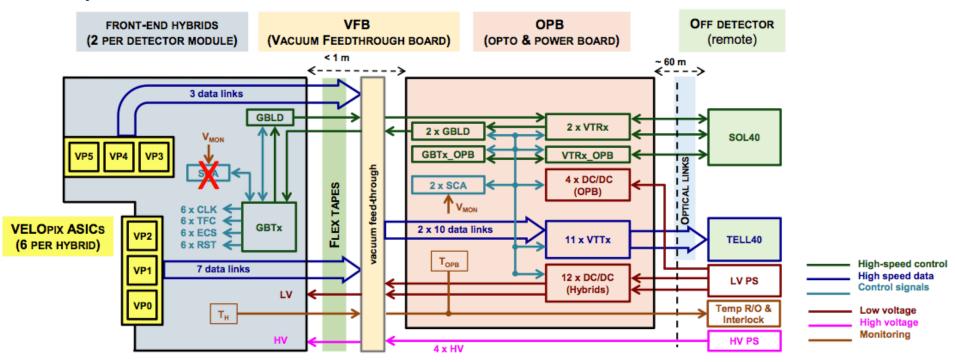

### **Electronics chain: overview**

- Electrical to optical conversion outside of vacuum tank → 20 Optical links ~5 Gbit/s each

- 1 FPGA to reads out 1 module

VELO specific components involve: data transmission, backend data acquisition and Time reordering of hits/clusters.

21

### **Electronics chain: overview**

1 FPGA to reads out 1 module

### Prototypes of all components currently under test

22

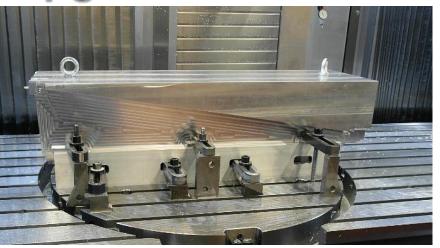

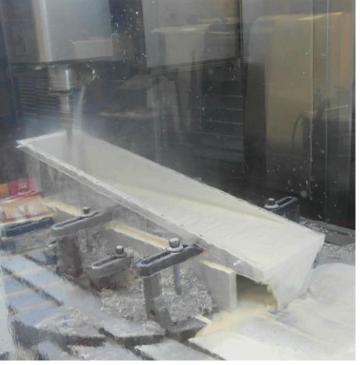

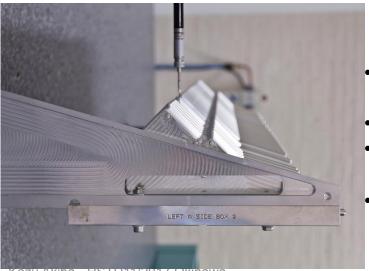

### **Upgrade RF Foil**

### Requirements

- Vacuum tight (< 10<sup>-9</sup> mbar l/s)

- Radiation hard

- Low Mass

- Good electrical conductivity

- Thermally stable and conductive

### Material and fabrication:

- Aluminium (AlMgMn).

- <u>500 µm thickness</u>:

- By 5-axis milling of a single homogeneous block

- Chemical etching 250µm

### **Upgrade RF Foil Prototypes**

- TL: start with an Al Block.

- BL: milling machine

- TR Full size foil with 500 μm

- BR: metrology of prototype

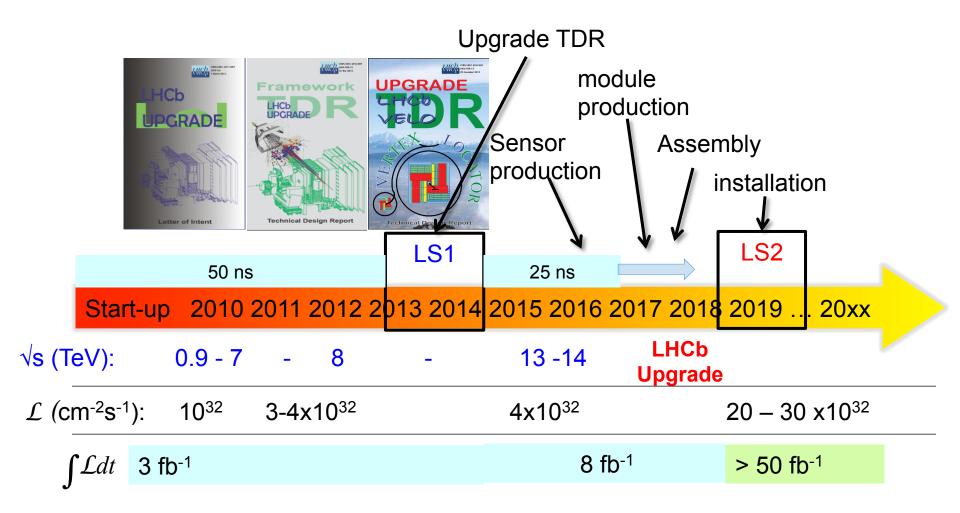

### **Timeline**

Many Engineering Design Reviews (EDR) done in 2017 Some parts already gone through Production Readiness Review (PRR)

25

### **Summary**

- We plan to install a fully upgraded detector in the LS2/2019

- With a 40 MHz "triggerless" readout

- Run @ L =  $2 \times 10^{33}$  cm<sup>-2</sup> s<sup>-1</sup> ( $5 \times 10^{33}$  cm<sup></sup>

- VELO subdetector will consist planar silicon pixel sensors with 55 x 55 μm<sup>2</sup> pitch

- Get closer to the collision point

- Bigger segmentation

- New ASIC VeloPix with 20 Gbit/s output bandwidth

- Evaporative CO<sub>2</sub> cooling in Silicon with a micro-channel substrate as interface

- 500/250 μm thick RF-box milled from solid block of Aluminum

- Developments for the upgrade going well and on schedule

The LHCb VELO upgrade is a challenging project with many new techniques

# Back up

### Foil clearances and dedicated sensors

### **LHCb Upgrade Overview**

29

### VeloPix ASIC

| Specification                | Timepix3                 | VeloPix           |

|------------------------------|--------------------------|-------------------|

| pixel dimension              | $55x55 \ \mu m^2$        | $55x55 \ \mu m^2$ |

| matrix size                  | 256x256                  | 256x256           |

| timewalk                     | < 25  ns                 | < 25  ns          |

| Time over Threshold range    | 10 bit                   | 4 bit             |

| leakage current compensation | > 20 nA                  | > 20 nA           |

| (per pixel)                  |                          |                   |

| Time stamp resolution        | 1.6 ns                   | 25 ns             |

| Time stamp range             | 18 bit                   | 12 bit            |

| sustainable hit rate         | 40 MHits/s               | > 600  MHits/s    |

| output bandwidth             | $2.5 \; \mathrm{Gbit/s}$ | > 13.6  Gbit/s    |

| power consumption per chip   | < 2 Watts                | < 3 Watts         |

| radiation hardness           | no spec.                 | > 400 MRad        |

| single event upset robust    | no                       | yes               |

### Silicon sensors

• Focus on two vendors with proven track record in radiation hard and HV tolerant sensor designs:

VELO PIXEL Layout (Draft)

HPK

Single PIX 3x1 PIXEL

Micron

- n-in-p, 200 um thick

- 450 um guard ring

- 3x1 and single-ASIC sensors

- n-in-n or n-in-p, 150/200 um

- Baseline of 450 um guard ring

- Reduced width guard rings (150um) and overlapping guard rings on backside in n-in-n case

- Irradiation and test beam program to validate Sensor and ASIC tech at high rates.

31

un 0

25

10 x 450 um

### **Timing**

Telescope has a very stable and precise time  Single TPX3 measurement resolution measured to 1 ns and telescope down to 0.4 ns.

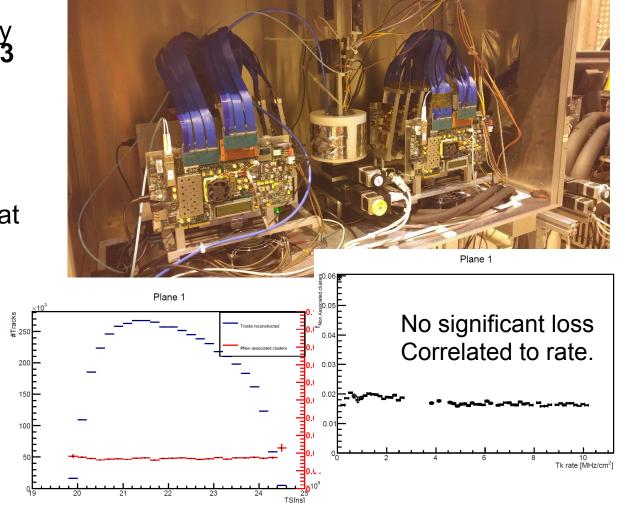

### The Telescope – our infrastructure.

- The Timepix3 telescope is fast, precise, and easy to combine with Timepix3 DUTs.

- The software is written in Gaudi architecture: Kepler. ~15k tracks/s.

- Charge measurement and clustering give a great pointing resolution

down to 2 μm.

- Precise time stamps make it simple and clean for the PatRec.

- Tracks can be measured with 0.4 ns timing precision

- We have operated up to 10 Mtracks/s/cm<sup>2</sup>.

A.DosilSuarez

### **Timeline**

Current upgrade plan still compatible with post LS3 ...

# **Module prototypes**

The modules will be produced in both Nikhef and Mancheter University

# Modules: 52 @ 25mm pitch (along beam)

Micron

# **Sensor Production**

- Sensor corners to be rounded to optimise foil clearance

- Implant width: 39 μm chosen better efficiency

300V: Underdepleted

### Electronics chain: overview

### Many common LHCb elements

- 48 copper links from chips.

- Electrical to optical conversion outside of vacuum tank → 20 Optical links ~5 Gbit/s each

- 1 FPGA to reads out 1 module

VELO specific components involve: data transmission, backend data acquisition and Time reordering of hits/clusters.

38