### Digital Readout for Cryogenic Detectors using Superconductor Integrated Circuits

Timur V. Filippov, Dmitri E. Kirichenko,Anubhav Sahu, Masoud Radparvar,M. Eren Celik, and Deepnarayan Gupta

HYPRES, Inc 175 Clearbrook Road, Elmsford, NY 10523

Superconductor fast digitizers and low-power logic are well suited for sensor array readout, enabling precise pulse timing and digital multiplexing.

#### We can do both

- Digital time-division multiplexing

- Time-of-arrival measurements

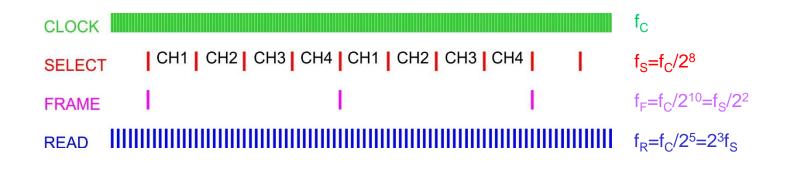

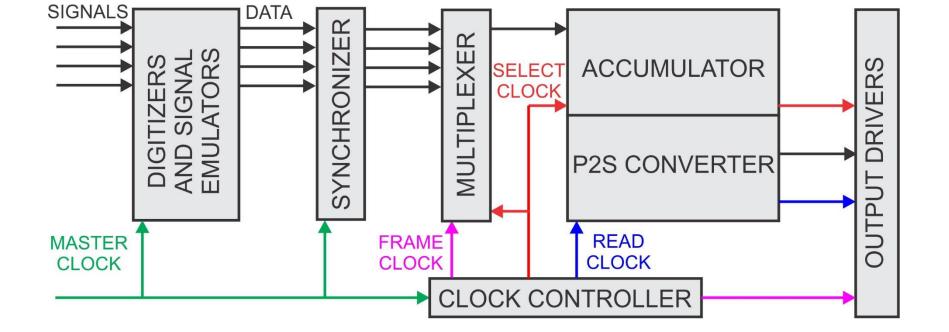

### Digital Time-Division Multiplexing Readout Circuit for Sensor Arrays

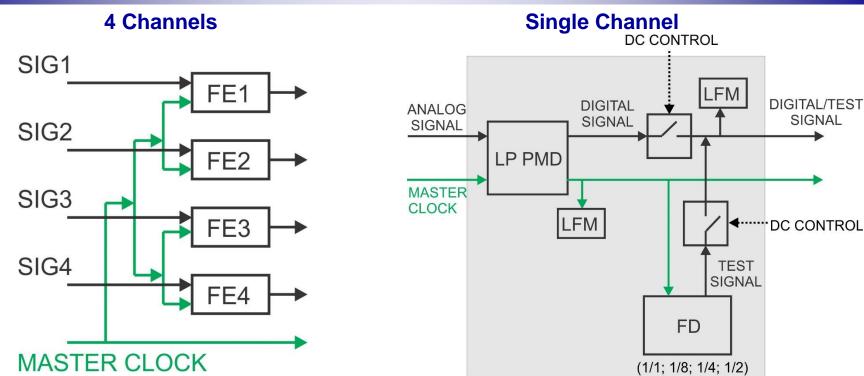

### **Synchronous 4-Channel Front-End**

#### **Signal Variations at each Channels**

| CHANNEL<br>NAME | SIGNAL<br>NAME | TEST<br>PATTERN 1 | TEST<br>PATTERN 2 | TEST<br>PATTERN 3 |

|-----------------|----------------|-------------------|-------------------|-------------------|

| CH1             | SIG1           | f <sub>c</sub>    | f <sub>c</sub> /2 | NO SIG            |

| CH2             | SIG2           | f <sub>c</sub> /8 | f <sub>c</sub> /2 | NO SIG            |

| СНЗ             | SIG3           | f <sub>c</sub> /4 | f <sub>c</sub> /2 | NO SIG            |

| CH4             | SIG4           | f <sub>c</sub> /2 | f <sub>c</sub> /2 | NO SIG            |

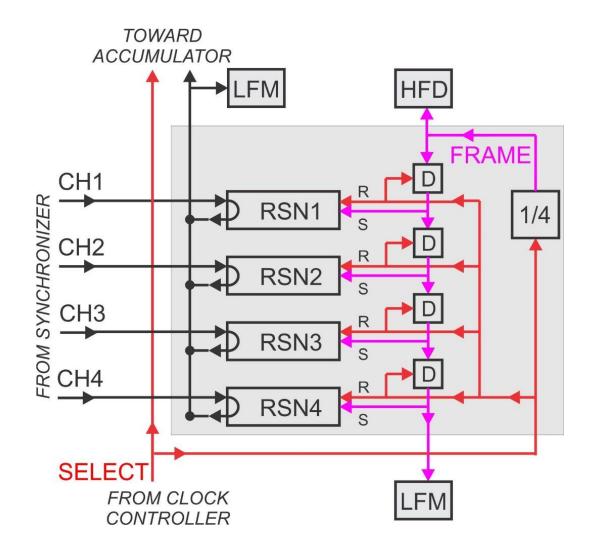

#### **Design Components: Multiplexer**

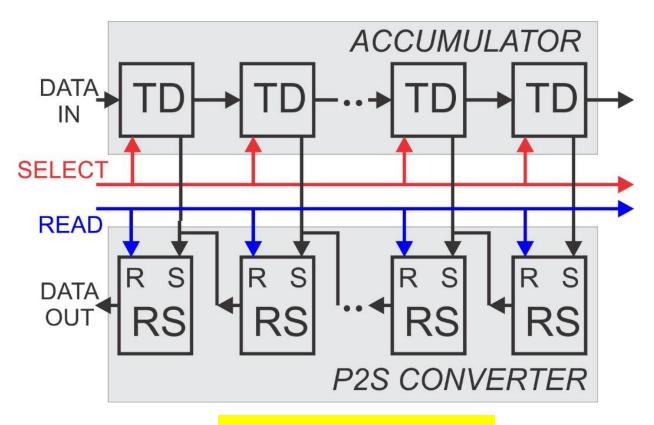

#### **Accumulator and P2S Converter**

12345678 **C**  $f_{\rm C}/8: 256/8=2^5 \rightarrow 00000100$

$f_{\rm C}/4:256/4=2^6 \rightarrow 000000100$

$f_{\rm C}/2:256/2=2^7 \rightarrow 00000010$

$f_{C}$  : 256 = 2<sup>8</sup>  $\rightarrow$  00000000 1

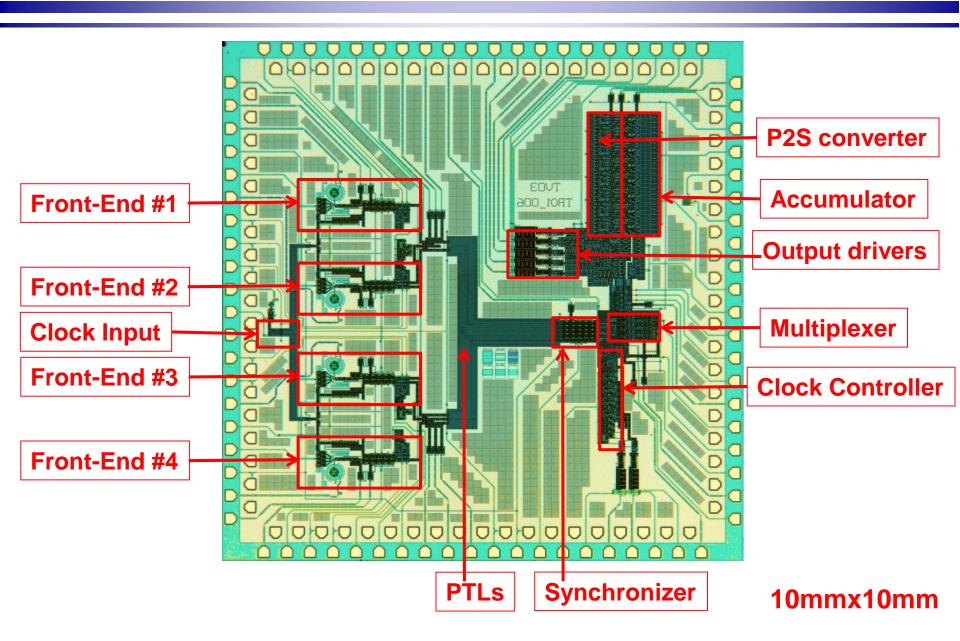

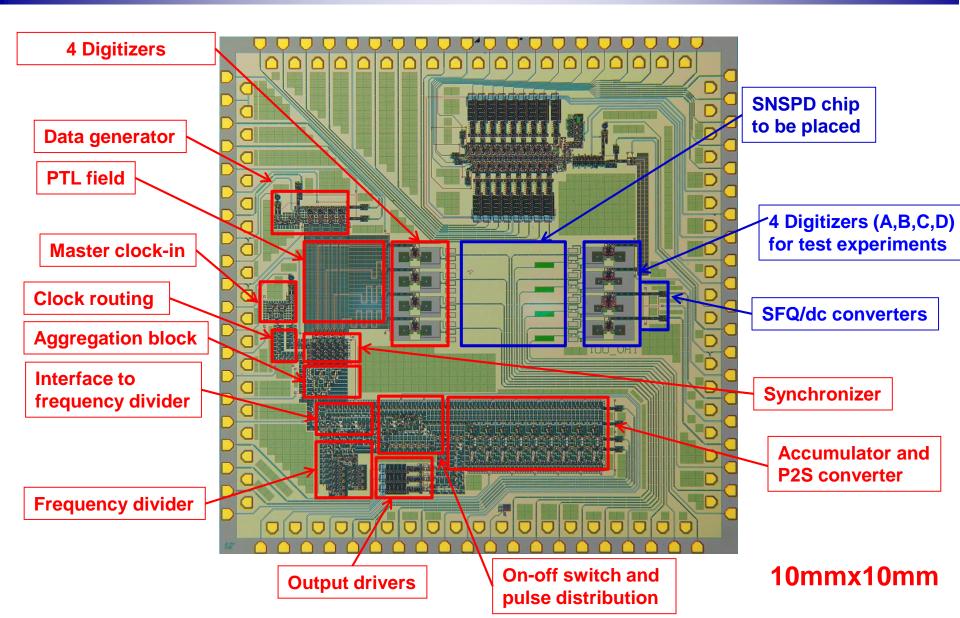

## **Chip Layout**

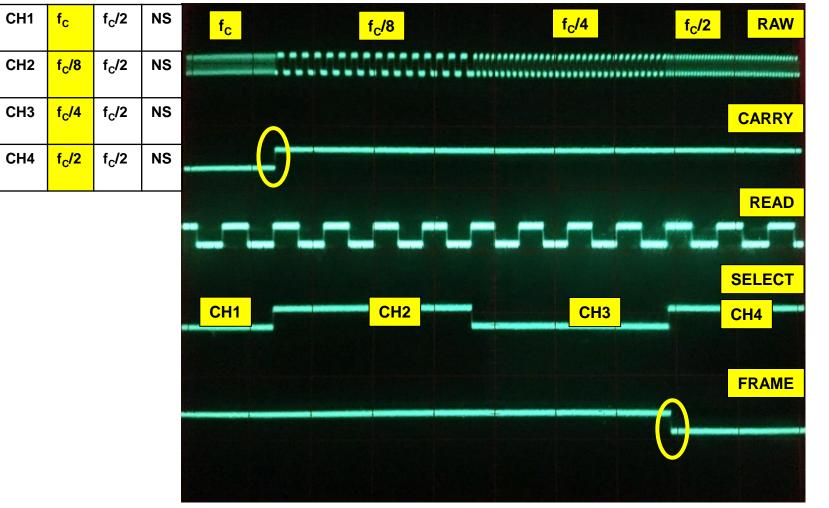

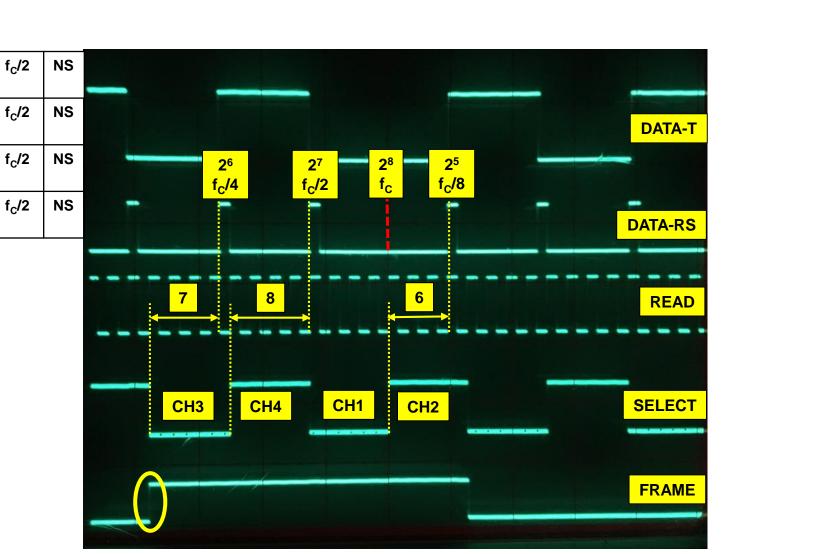

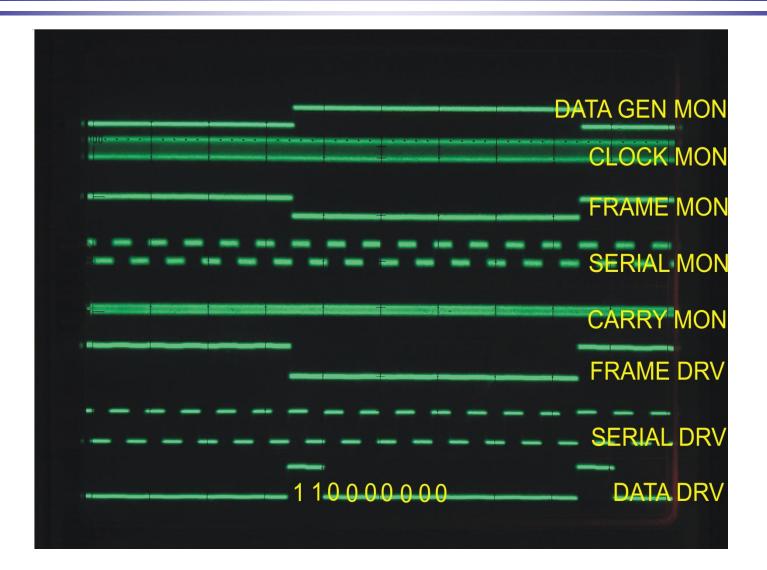

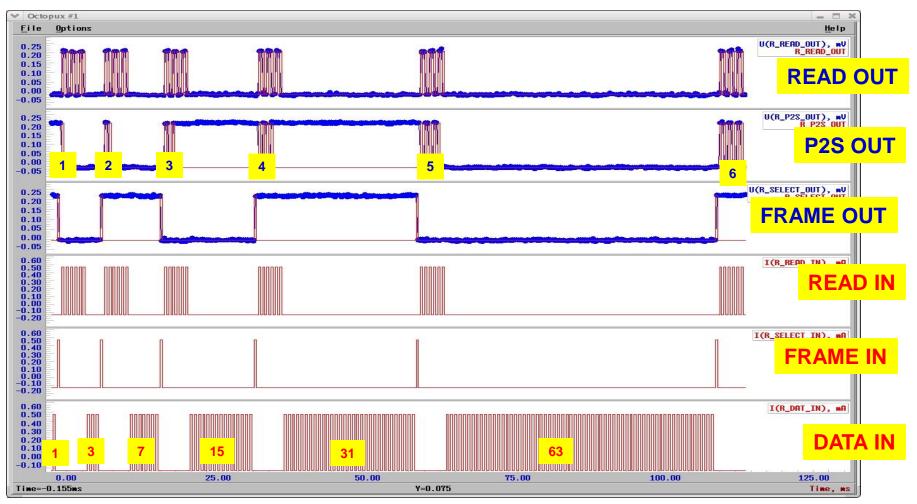

#### LOW FREQUENCY TESTING AT MONITOR LEVEL (1)

CIRCULATING ORDER: CH1,CH2,CH3,CH4 CARRY PULSE AT THE END OF CH1 IF f<sub>c</sub> APPLIED FRAME PULSE AT THE BEGINNING OF CH4

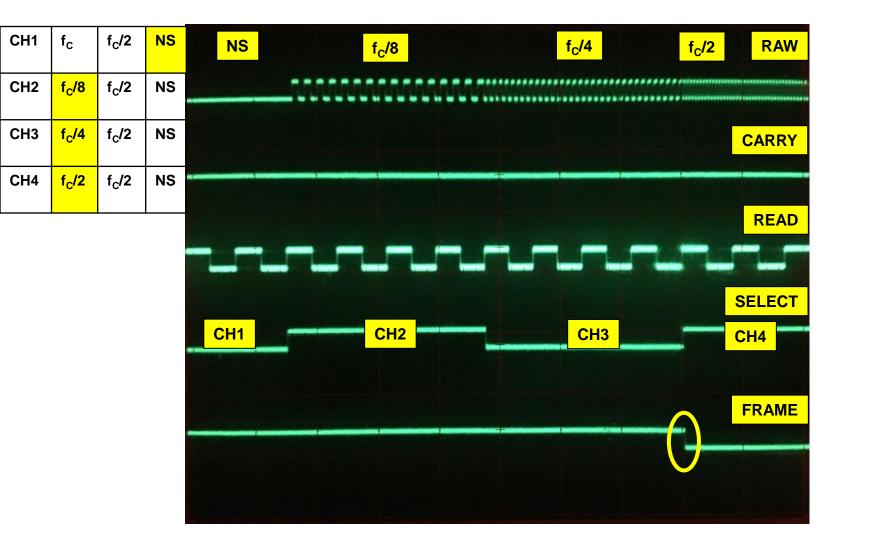

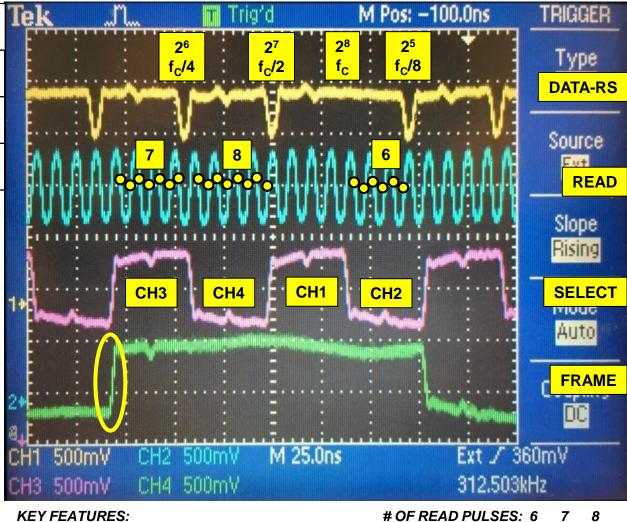

#### LOW FREQUENCY TESTING AT MONITOR LEVEL (2)

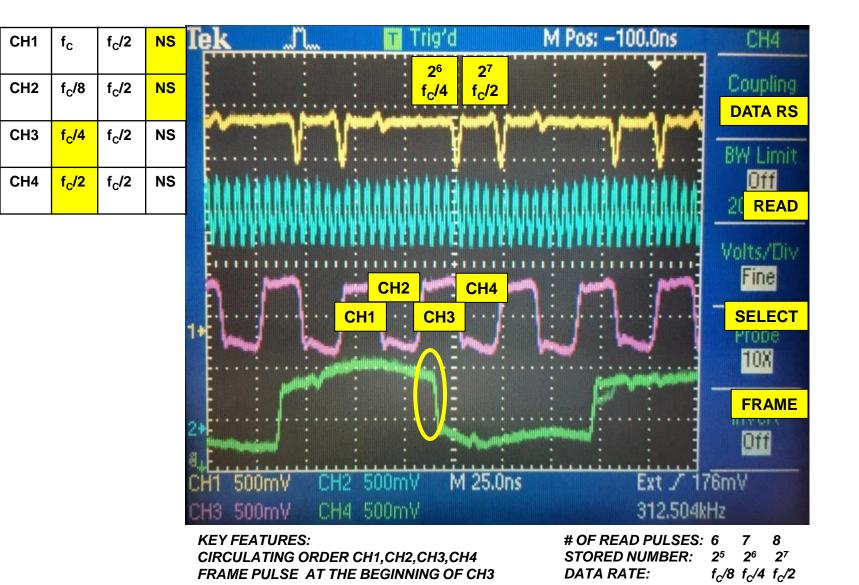

#### LOW FREQUENCY TESTING AT DRIVER LEVEL

KEY FEATURES: CIRCULATING ORDER CH1,CH2,CH3,CH4 FRAME PULSE AT THE BEGINNING OF CH3

CH1

CH2

CH3

CH4

f<sub>c</sub>

f<sub>c</sub>/8

$f_c/4$

$f_c/2$

# OF READ PULSES: 6 7 8 STORED NUMBER: 2<sup>5</sup> 2<sup>6</sup> 2<sup>7</sup> DATA RATE: f<sub>c</sub>/8 f<sub>c</sub>/4 f<sub>c</sub>/2

### **HIGH FREQUENCY TESTING @6.4GHz**

| CH1 | f <sub>c</sub>    | f <sub>c</sub> /2 | NS | 1 |

|-----|-------------------|-------------------|----|---|

| CH2 | f <sub>c</sub> /8 | f <sub>c</sub> /2 | NS |   |

| СНЗ | f <sub>c</sub> /4 | f <sub>c</sub> /2 | NS |   |

| CH4 | f <sub>c</sub> /2 | f <sub>c</sub> /2 | NS |   |

CIRCULATING ORDER CH1,CH2,CH3,CH4 FRAME PULSE AT THE BEGINNING OF CH3 # OF READ PULSES: 6 7 8 STORED NUMBER:  $2^5$   $2^6$   $2^7$ DATA RATE:  $f_c/8$   $f_c/4$   $f_c/2$

### HIGH FREQUENCY TESTING @12.8GHz

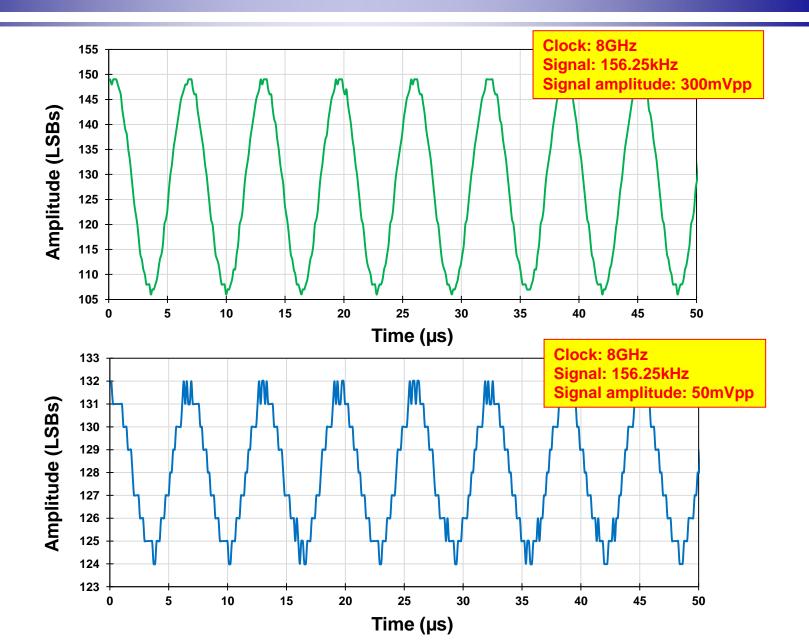

### **Signal Reconstruction**

### **Digital SNSPD Readout**

## **Digital SNSPD Readout**

- SNSPD Output: Fast rise-time (~100 ps) pulse, 10-20 µA

- Requirement: Precise measurement of time-of-arrival

- High clock speed (time-to-digital conversion)

- Power consumption ~ 10 μW

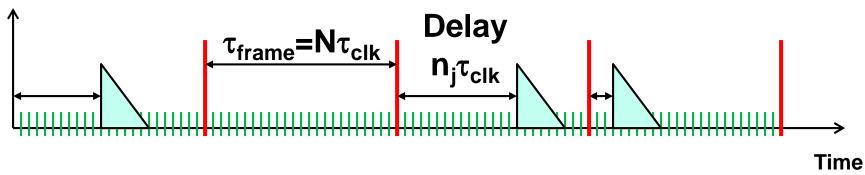

- Time-of-arrival of photons measured as the number (n) of clock periods (τ<sub>clk</sub>) in a frame of N clock periods

- > Discrete time resolution  $\tau_{clk}$  ~30 ps

- > Count Rate =  $1/\tau_{\text{frame}} \sim 65 \text{ MHz}$

- Counting of clock pulses started at the beginning of a frame and stopped at the arrival of the first SNSPD output pulse

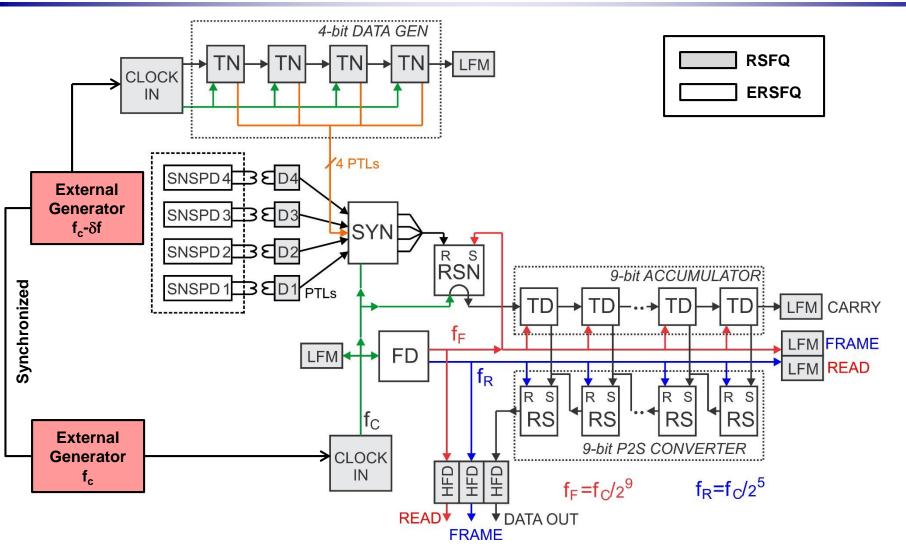

### **Readout Chip Test with On-chip Data Generator**

O. A. Mukhanov and S. R. Rylov, "Time-to-digital converters based on RSFQ digital counters," IEEE Trans. Appl. Supercond., vol. 7, pp. 2669-2672, June 1997.

A. Kirichenko, S. Sarwana, D. Gupta, I. Rochwarger, and O. Mukhanov, "Multi Channel Time Digitizing Systems," IEEE Trans. Appl. Supercond., vol. 13, pp. 454-458, June 2003

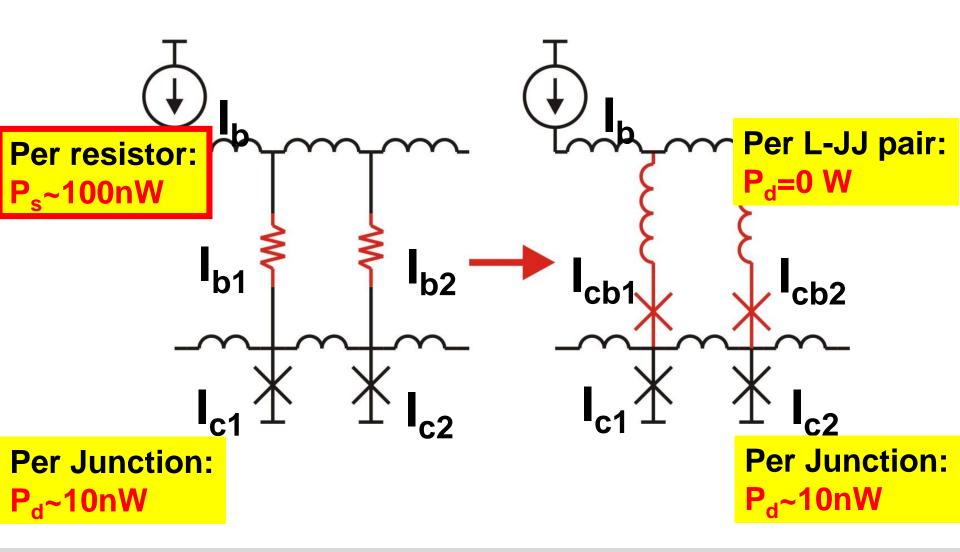

### **RSFQ vs ERSFQ: power consumption**

#### Power consumption balance: (10+100)nW→(10+0)nW

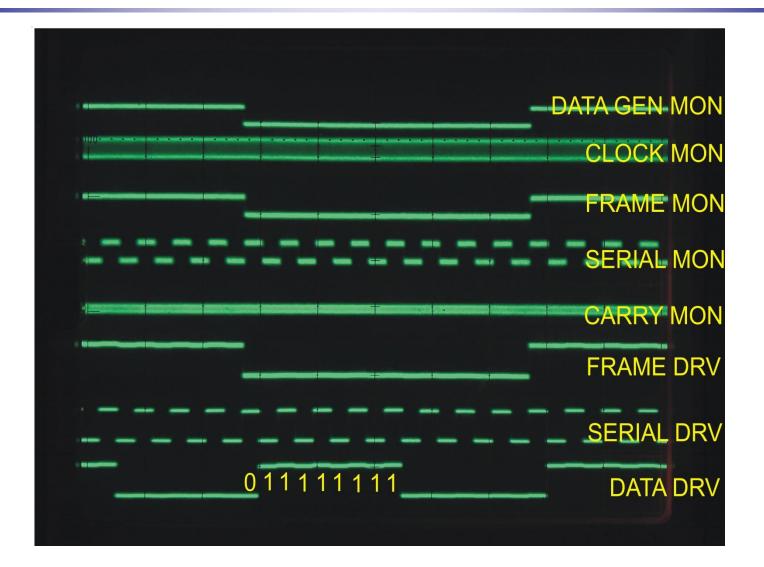

### **Digital Readout Chip for 4 SNSPDs**

|          | DATA GEN MON |

|----------|--------------|

|          | CLOCK MON    |

|          |              |

|          | SERIAL MON   |

|          | CARRY MON    |

|          | FRAME DRV    |

|          | SERIAL DRV   |

| 00000000 | DATA DRV     |

|          |              |

|         | DATA GEN MON |

|---------|--------------|

|         | CLOCK MON    |

|         | FRAME MON    |

|         | SERIAL MON   |

|         | CARRY MON    |

|         | FRAME DRV    |

|         | SERIAL DRV   |

| 1000000 | DATA DRV     |

|         |              |

|          | DATA GEN MON |

|----------|--------------|

|          | CLOCK MON    |

|          | FRAME MON    |

|          | - SERIAL MON |

|          | CARRY MON    |

|          | FRAME DRV    |

|          | SERIAL DRV   |

| 01000000 | DATA DRV     |

|          | - DATA GEN MON |

|----------|----------------|

|          | CLOCK MON      |

|          | FRAME MON      |

|          | SERIAL MON     |

|          | CARRY MON      |

|          | FRAME DRV      |

|          | SERIAL DRV     |

| 11111111 | DATA DRV       |

|          |                |

|          | DATA GEN MON |

|----------|--------------|

|          | CLOCK MON    |

|          |              |

|          | SERIAL MON   |

|          | CARRY MON    |

|          | FRAME DRV    |

|          | SERIAL DRV   |

| 00000000 | DATA DRV     |

|          |              |

### **Power Consumption and Scalability**

| All power numbers in µW |                                | Conservative<br>Design (I <sub>c-avg</sub> =<br>250µA, V <sub>bias</sub> =<br>2.6mV) | Optimized<br>Design | Scaled RSFQ<br>(I <sub>c-avg</sub> = 125 μA,<br>V <sub>bias</sub> = 1mV) |

|-------------------------|--------------------------------|--------------------------------------------------------------------------------------|---------------------|--------------------------------------------------------------------------|

|                         | 4 digitizers + routing         | 37.20                                                                                | 22.80               | 4.38                                                                     |

|                         | PTL field                      | 17.60                                                                                | 5.50                | 1.06                                                                     |

| RSFQ                    | Master clock-in                | 25.80                                                                                | 25.80               | 4.96                                                                     |

|                         | 3 Output drivers               | 109.20                                                                               | 11.47               | 2.21                                                                     |

|                         | RSFQ total:                    | 189.8                                                                                | 65.6                | 12.6                                                                     |

|                         | Clock routing                  | 0.44                                                                                 | 0.44                | 0.44                                                                     |

|                         | Synchronizer                   | 1.14                                                                                 | 1.14                | 1.14                                                                     |

|                         | Aggregation block              | 0.90                                                                                 | 0.90                | 0.90                                                                     |

| eRSFQ                   | Interface to frequency divider | 2.00                                                                                 | 2.00                | 2.00                                                                     |

|                         | Frequency divider              | 1.36                                                                                 | 1.36                | 1.36                                                                     |

|                         | Switch and pulse distribution  | 3.63                                                                                 | 3.63                | 3.63                                                                     |

|                         | Counter and serializer         | 6.39                                                                                 | 6.39                | 6.39                                                                     |

|                         | eRSFQ total @32GHz:            | 15.9                                                                                 | 15.9                | 15.9                                                                     |

|                         | Chip total:                    | 205.7                                                                                | 81.4                | 28.5                                                                     |

## **Power Consumption and Scalability (contd.)**

|                             |                                | 4-SNSPD Readout                 | 8-SNSPD Readout                 | 16-SNSPD Readout                   |

|-----------------------------|--------------------------------|---------------------------------|---------------------------------|------------------------------------|

|                             | All power numbers in µW        | Scaled RSFQ (I <sub>c-avg</sub> | Scaled RSFQ (I <sub>c-avg</sub> | Scaled RSFQ (I <sub>c-avg</sub>    |

|                             |                                | = 125 µA, V <sub>bias</sub> =   | = 125 µA, V <sub>bias</sub> =   | = 125 $\mu$ A, V <sub>bias</sub> = |

|                             |                                | 1mV)                            | 1mV)                            | 1mV)                               |

|                             | 4 digitizers + routing         | 4.38                            | 8.77                            | 17.54                              |

|                             | PTL field                      | 1.06                            | 2.12                            | 4.23                               |

| RSFQ                        | Master clock-in                | 4.96                            | 4.96                            | 4.96                               |

|                             | 3 Output drivers               | 2.21                            | 2.21                            | 2.21                               |

|                             | RSFQ total:                    | 12.61                           | 18.05                           | 28.94                              |

|                             | Clock routing                  | 0.44                            | 0.44                            | 0.44                               |

|                             | Synchronizer                   | 1.14                            | 2.28                            | 4.56                               |

|                             | Aggregation block              | 0.90                            | 1.80                            | 3.60                               |

| eRSFQ                       | Interface to frequency divider | 2.00                            | 2.00                            | 2.00                               |

| eksrų                       | Frequency divider              | 1.36                            | 1.36                            | 1.36                               |

|                             | Switch and pulse distribution  | 3.63                            | 3.63                            | 3.63                               |

|                             | Counter and serializer         | 6.39                            | 6.39                            | 6.39                               |

|                             | eRSFQ total @32GHz:            | 15.9                            | 17.9                            | 22.0                               |

|                             | Chip total:                    | 28.5                            | 36.0                            | 50.9                               |

| Power Consumption per SNSPD |                                | 7.1                             | 4.5                             | 3.2                                |

## **Converting to SFQ5EE process at MIT/LL**

We designed both RSFQ and ERSFQ 6-bit counters using MIT/LL SFQ5EE process

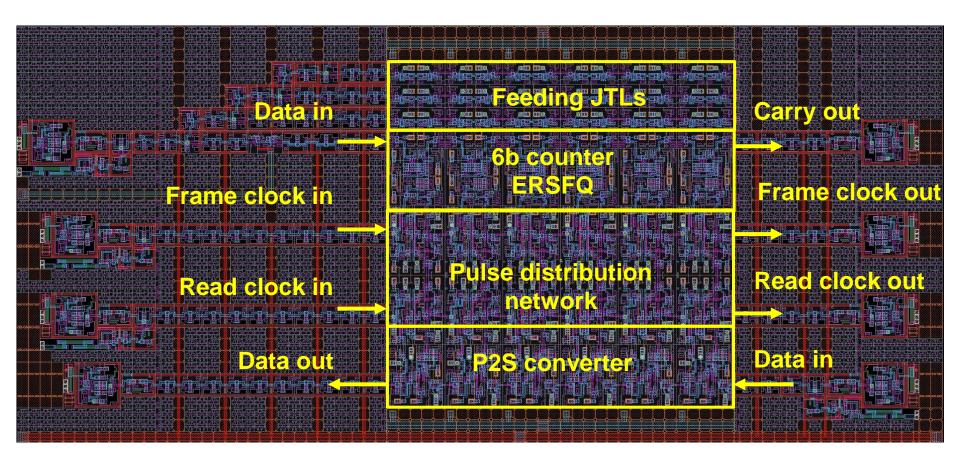

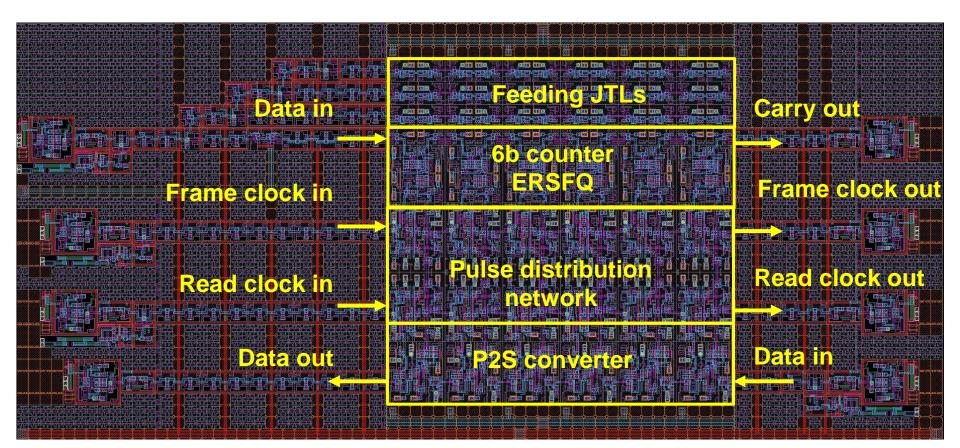

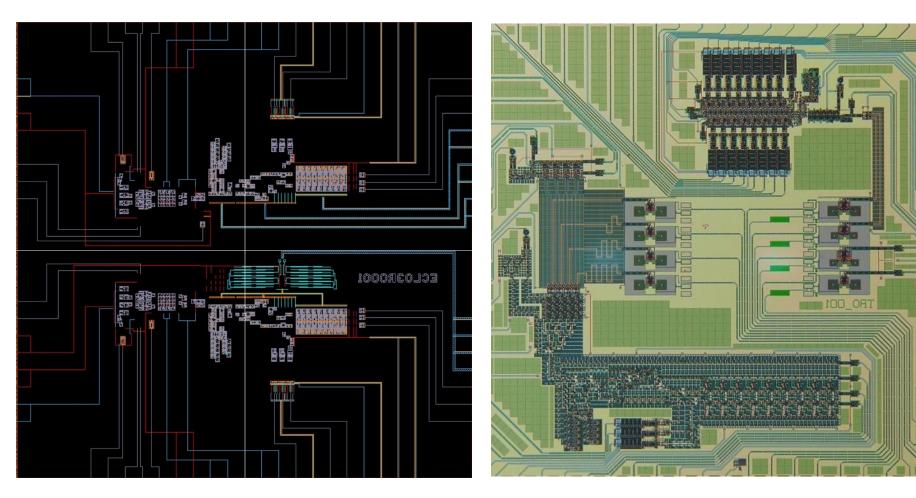

#### tvI03\_ed\_003: 6b counter

#### tvI03\_ed\_003: 6b counter

ERSFQ counter is 22.5 times smaller in area by converting to SFQ5EE

#### **Test Results**

**RSFQ margins: 41mA-68mA**

ERSFQ margins: 45mA-65mA Critical Current 51mA

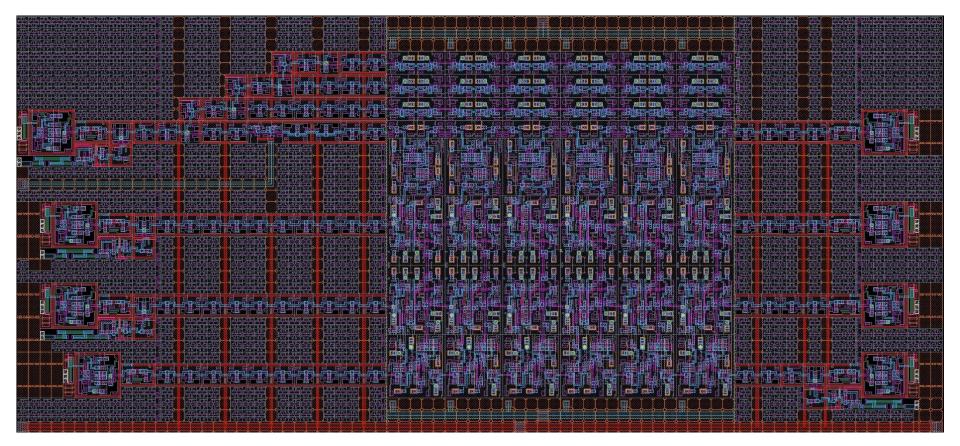

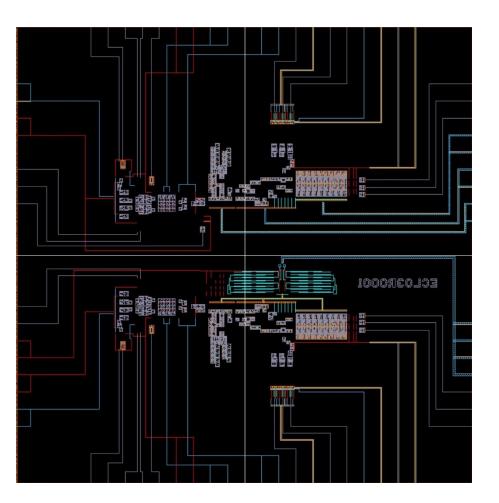

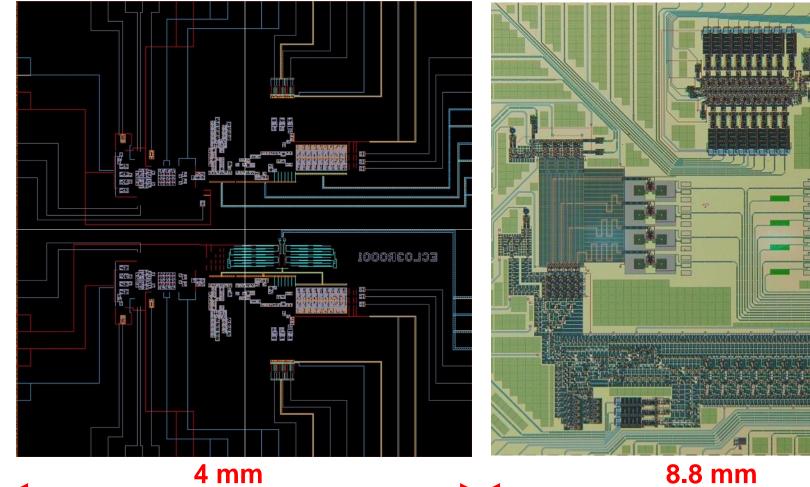

### 4-channel SNSPD Aggregating Readout Chip

2 readouts (ERSFQ and RSFQ) are placed on the same chip

### 4-channel SNSPD Aggregating Readout Chip

2 readouts (ERSFQ and RSFQ) are placed on the same chip

## 4-channel SNSPD Aggregating Readout Chip

#### **4 mm**

2 readouts (ERSFQ and RSFQ) are placed on the same chip

## Conclusion

#### **Digital TDM Readout**

- By means of embedded pattern generators we proved the correct operation of each channel and of all 4 channels combined at frequencies up to 12.8 GHz.

- We were able to perform reconstruction of signal applied to individual ADC.

#### **Time-to-Digital Readout for SNSPDs**

- > Current sensitivity ( $\Delta I$ ) < 10  $\mu A$

- Preserves fast rise times (< 100 ps)</p>

- Time-of-arrival can be measured with 30 ps digital resolution

- Low power, scalable eRFSQ circuitry

- ERSFQ digital circuit density is 22.5X higher with 8-layer MIT/LL process than 4-layer HYPRES process

- > The goal of 10 $\mu$ W per SNSPD is reachable.

- Digital TDM readout was supported in part by a grant from DOE office of Nuclear Physics

- **TDC** readout was supported by MIT/LL

- New RSFQ/ERSFQ Counters for MIT/LL SFQ5ee process was supported by a research grant from the Office of Naval Research

- The authors would like to thank

- HYPRES and MIT/LL fab teams for fabricating the chips,

- > Andrew J. Kerman, Eric Dauler for fruitful discussions,

- Igor Vernik for preliminary testing,

- Denis Amparo for taking photographs.