# VMM discussion

Michael Lupberger (CERN)

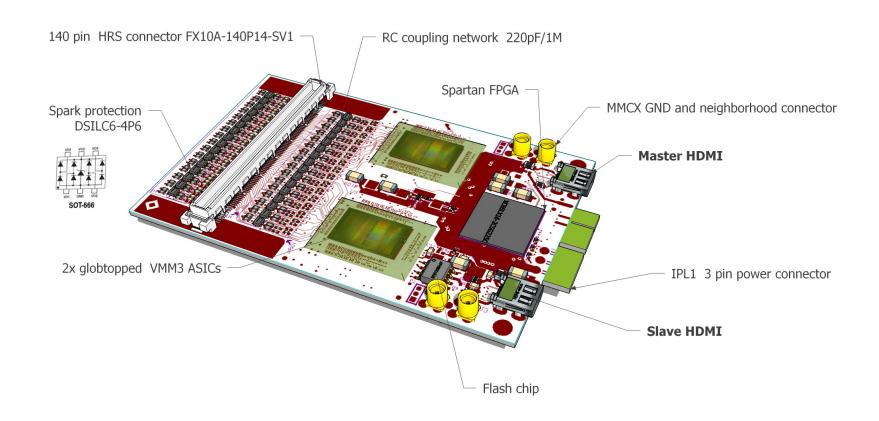

## FECv6 with D-Card connects to VMM hybrids

VMM ASIC: Readout chip for ATLAS NSW

- 130 nm CMOS technology

- VMM3 delivered: end 2016

- Configuration via CMOS lines (data+clock)

- · 64 channels (preamp and shaper, ADCs)

- Output: digitised data (38 bit/hit), 0-supp.

- · Up to 200 MHz clock

- · Self triggered

#### VMM hybrid:

- · Two VMM ASICs

- · Spartan6 FPGA

- · LDOs for power

- Protection circuit

#### Adapter card:

- Mainly SVDS drivers

- · Can read up to 8 VMM hybrids

- Work on possible master/slave ongoing

## **VMM**

# News from ATLAS (from RD51 Miniweek)

| Issue in VMM2               | Circuit                             | Status in VMM3 | Notes               |

|-----------------------------|-------------------------------------|----------------|---------------------|

| Handling sTGC rates         | analog front-end                    | þ              | - 5<br>- 5<br>- 240 |

| Early saturation            | current-out peak detector           | P              | - W                 |

| ADC accumulation            | ADCs                                | ₽              | improveme           |

| Pulser DAC saturation       | DAC bias circuit                    | þ              | 160                 |

| Pulser rise-time and noise  | pulser circuit and injection switch | Po             | - 140               |

| Prompt output disabled      | control logic                       | Po Po          | - 120               |

| <b>Event loss</b>           | ADC reset logic                     | þ              | _ 100               |

| Threshold bit error         | discrimination logic                | þ              | -                   |

| BCID advance-latch issue    | Gray-code counter                   | þ              | - 12                |

| Other data integrity issues | data, token & FIFO logic            | þ              | _ 126               |

| Counter turnaround          | counter logic                       | þ              | - 124               |

| Front-end off w/SFM         | analog front-end                    | Po             | -                   |

| Peak detect hold time       | hold node                           |                | not tested          |

| Buffer float at bypass      | buffer input stage                  | þ              | -                   |

| High baseline (5% samples)  | baseline stabilizer                 | <b>(₽)</b>     | yield, workaround   |

## News from ATLAS (from RD51 Miniweek)

| New Function in VMM3             | Circuit                | Status in VMM3     | Notes                         |

|----------------------------------|------------------------|--------------------|-------------------------------|

| Handle sTGC capacitance & charge | analog front-end       | Pa<br>Pa           | impact of protection resistor |

| Tail cancellation                | analog front-end       | Pa Pa              | -                             |

| Trimming range extension         | trimmer analog/logic   | Ъ                  | 3/4 of targeted               |

| L0 handling logic                | digital implementation | Ъ                  | stress tests in progre        |

| Simultaneous readout             | various logic changes  | ( <del>[</del> 2]) | locking, workaroun            |

| CMOS IOs config. and new reset   | config. logic and IOs  | Ъ                  | -350                          |

| SLVS-400 IOs                     | digital interface      | Ъ                  | - 100                         |

| iming ramp optimization          | timing circuit         | Ъ                  | —не                           |

| imeout ramp autoreset            | timing circuit         | Ъ                  | <del>-</del>                  |

| equisition reset on ENA          | control logic          | (₽)                | single event, workaround      |

| 2-channel skip                   | inter-channel logic    | Ъ                  | -                             |

| ART flag synchronization         | ART logic              | Ъ                  | -                             |

| EU tolerance                     | logic                  |                    | tests queued                  |

| Pulser range extension           | injection circuit      | Po                 | -                             |

| Timing ramp at threshold         | timing circuit         | Po                 | -                             |

## News from ATLAS (from RD51 Miniweek)

- VMM3 is being <u>extensively tested</u> at several institutions, and <u>five residual issues</u> have been found two from VMM2 still present in smaller amount:

- $\Rightarrow$  ADC resolution (10b >  $\sim$ 7b and 8b >  $\sim$ 6b)

- ⇒ trimming (3/4 of planned extended range)

thee have a workaround

- direct output locking in ToT, workaround TtP

- acquisition reset on EN, workaround CS

- ⇒ 5% high analog baseline, workaround STLC

- VMM3 solved all readout stability issues we found in VMM2, added many more features

- VMM3 will be tested for SEU in Democritus Greece under Neutron irradiation in Spring 2017

- Revision to fix residual issue recommended, if schedule allows on May 2014 (Going to production for ATLAS) although the current version looks that it is enough good for trigger + readout (charge & timing measurements of high precision).

### **VMM**

#### Clarification

From Vinnies summary slide @ Mini week in December

- No export license needed

- CERN working for a universal license for all ASICs fabricated by Global Foundries, please check with P. Farthouat

Triggered fear/misunderstanding regarding availability of

VMM for certain regions = export restrictions

George and Vinnie solved this misunderstanding:

- CERN works on license for all Global foundries chips

- VMM might be included if this puts no limitations

- BNL works on license with goal: no export restrictions

VMM3 production: ATLAS is working on it

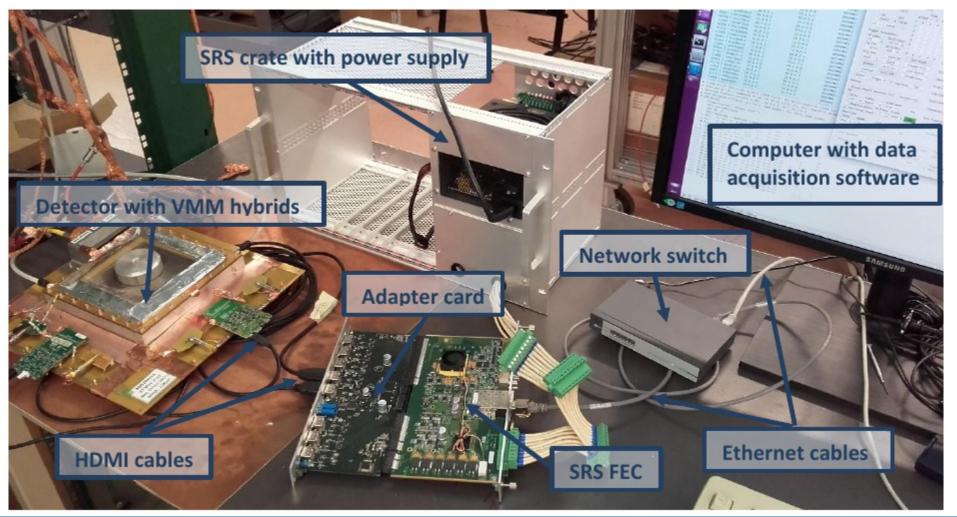

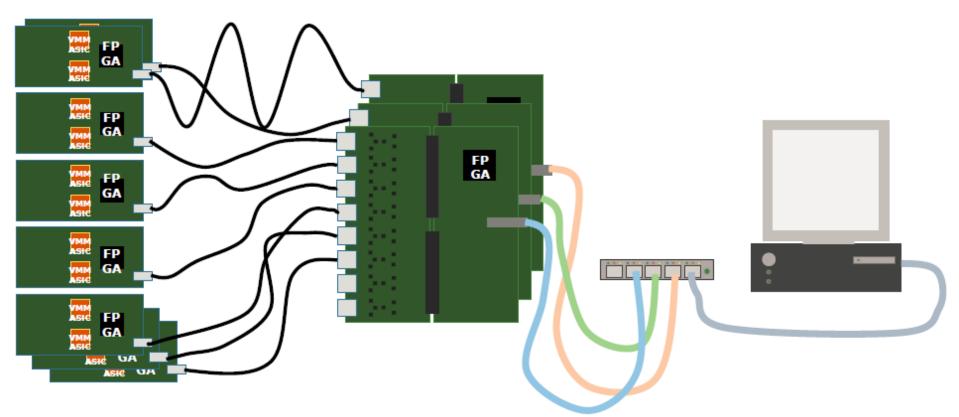

### Detector electronics chain

#### Detector electronics chain

VMM Hybrid  $\rightarrow$  HDMI cable  $\rightarrow$  Adapter card + FEC  $\rightarrow$  Ethernet  $\rightarrow$  Switch  $\rightarrow$ Ethernet  $\rightarrow$  PC

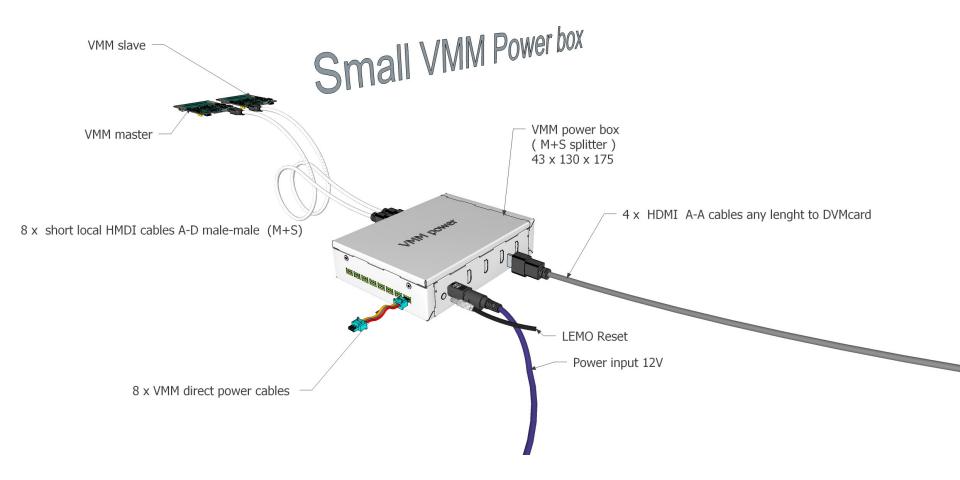

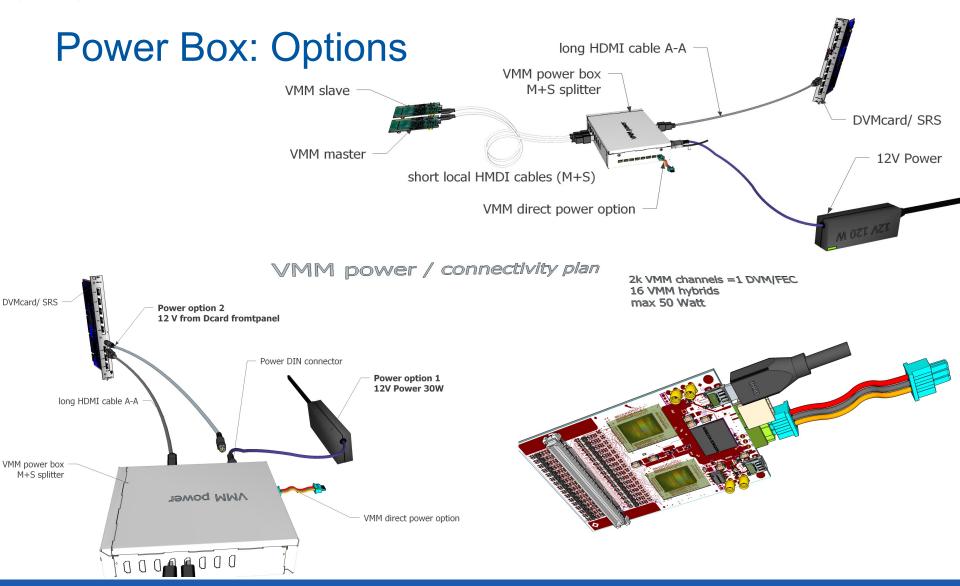

## High VMM power consumption: Power Box

## VMM3 hybrid with new connector

## **VMM**

## **Availability**

#### VMM3

- 4 hybrids at CERN

- ~32 VMM3 in stock, possibility to get 1-2 dozen more could build 16 up to 30 more hybrids (still on Panasonic)

#### more VMM3

- Low quantities: join next ATLAS production for prototypes

- Large quantities: join ATLAS NSW mass production

## **Availability**

#### D-Card:

- 2 at CERN + 1 that needs to be fixed

- For final version: minor power routing and outline changes

#### FEC

- You will need the FECv\_6

- Available at CERN store or directly from Samway also via SRStechnology.ch

- Power box: one prototype

## Manpower at CERN GDD

- Alex Rusu: (VMM hybrid, Dcard) (25% for 3 month by ESS)

- Hans: (50% @ CERN GDD lab as unpaid member)

- Michael Lupberger: 100% @CERN GDD lab

very limited → need help from the community / possible users

Things to be done:

- Master/Slave option with boundary conditions: use with power box, master only when directly connected to D-Card, hybrids must be identical, (FPGA code must be identical)

- → upgrade VMM to M/S mode (FPGA code) make Dcard M/S capable (power routing)

## VMM3 hybrid first price estimate by Alex

no guarantee

- a factor 2 more compared to APV25 when in production

- Depends on production quantities:

- >500 hybrids → 250 chf/hybrid (~2x APV25)

- 100 hybrids → 450 chf/hybrid

- 50 hybrids → 680 chf/hybrid

- 10 hybrids → 920 chf/hybrid (APV25 protos where about the same)

- 1 hybrids → 4000 chf/hybrid

Need small quantity phase for prototyping before large production

#### VMM3 ASIC RD51 order

- Next production (small quantities)

- ATLAS mass production

Request received: ASICs

Lev Shekhtman (Novosibirsk): 4/20

Dorothea Pfeiffer (ESS): 24/96