# Advanced Through Silicon Vias for Pixel Detectors

WP 2 Session

F. Hügging, N. Owtscharenko, N. Wermes (U Bonn)

T. Fritzsch, O. Ehrmann, K. Zoschke (Fraunhofer IZM)

- Through Silicon Vias are nowadays widely used in industry for different purposes, e.g:

- Memory chips

- 3D integration

- Interposers

- Usually these are dedicated, highly industrialized processes which are not accessible for other costumers

- Scope of the project is the development of a post processing TSV for a wider range of input material like:

- Readout ICs for silicon pixel detectors

- X-ray imager

- IR cameras

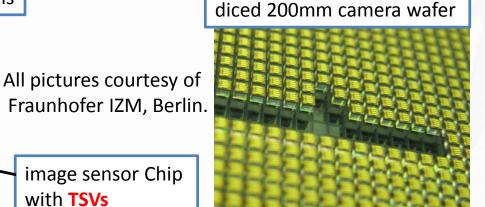

- Packaging of CMOS cameras

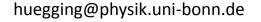

# **3D Integration Technology Using TSVs**

**3D Packaging:**

- CMOS Image Sensors

- MEMS

**3D Chipstacking:**

- Logic & DRAM for higher bandwidth (WIDE I/O interface)

- Memory stacking

Lateral die stacking for high bandwidth:

- Power/RF/Analog

- Logic & Analog

- Logic & Memory (GPU for Gaming)

Yole Report 2012: 3DIC & TSV Interconnects

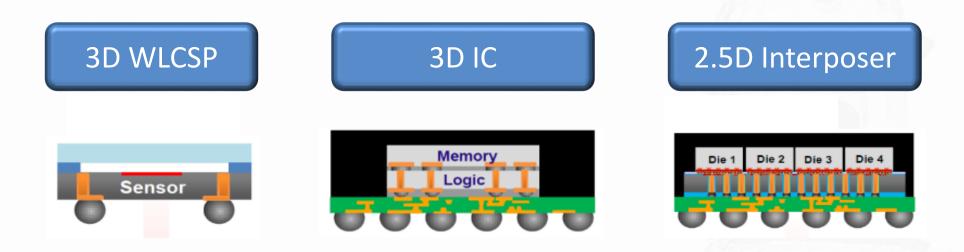

MD has introduced its highly anticipated "Fiji" solution for the graphics market atures a 595mm<sup>2</sup> logic device (ASIC) mounted in the center of a 1,011mm<sup>2</sup> Si inter our HBM stacks, each containing four DRAMs and a logic die, are also mounted on terposer

here are approximately 200,000 interconnects in the module including Cu pillar icrobumps and C4 bumps

ie interposer has 65,000 TSVs with 10µm-diameter vias

hsearchinc.com

© 2015 TechSearch International, Inc.

taken from T. Fritzsch, Interposer – An enabling technology for fan-out hybrid pixel modules, IWORID 2016, Barcelona.

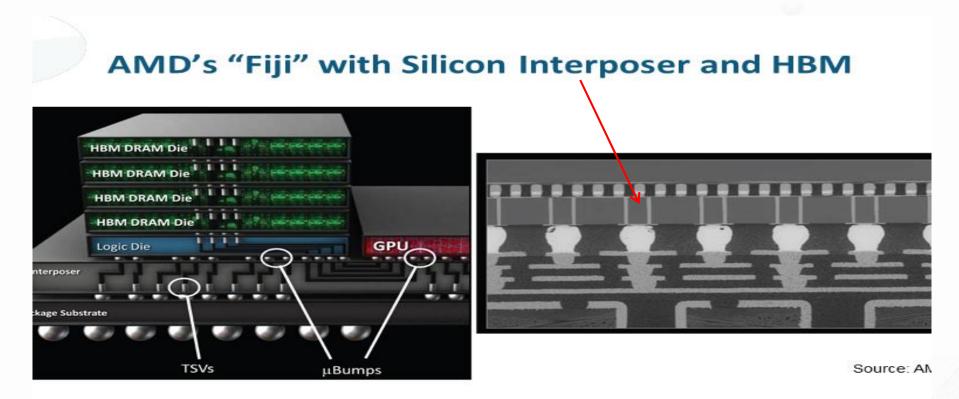

TSVs + wafer thinning + aligned bonding are the key technical elements for a 3D extension of electronics integration -> eminent field of industrial research

• denser packaging - lower power - larger I/O bandwidth - more functionality at lower cost

- Huge interest (and market) in packaging industry with fast recent advances

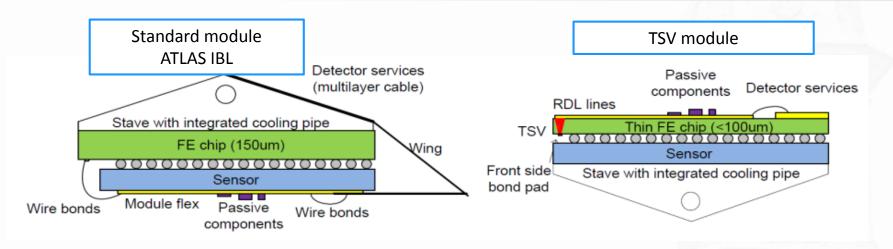

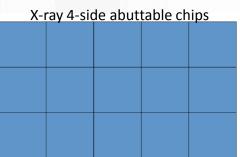

- Promise for <u>pixel detectors</u> -> more compact modules with active area maximization, no wire bonds, and 4-side abuttable (X-ray), use backside for wiring (RDL) → joint interest Bonn IZM

- Needs/challenges which both partners profit from

- o large length and relatively large aspect ratio (length/diameter) TSVs with reliable fabrication yield

- Goal: develop pixel modules for HL-LHC employing TSVs in a via-last process (after CMOS process)

#### **Through Silicon Via Types**

# **Bonn/IZM TSV experience**

universität**bonn**

#### Demonstrator single chip TSV modules built using

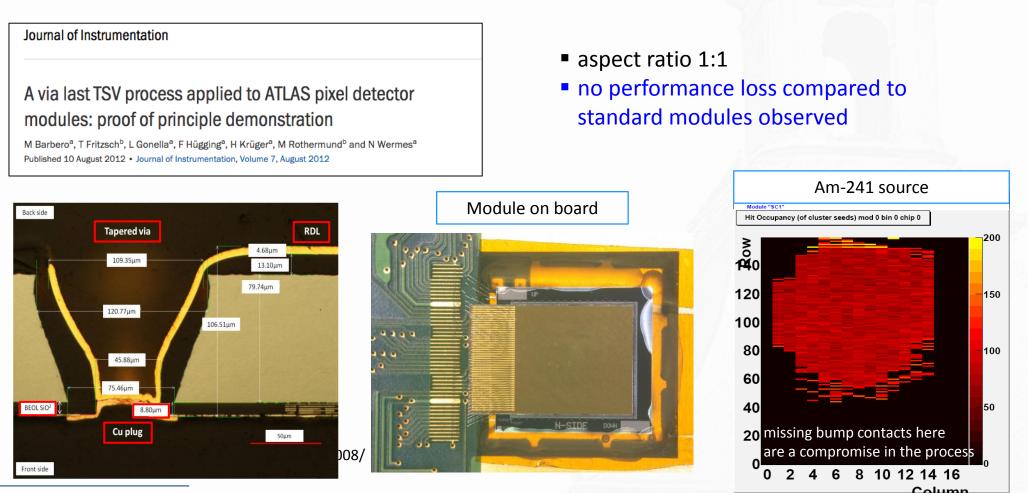

FE-I3 ATLAS pixel readout chip 90 μm thin, 6 x 11 mm<sup>2</sup>, with tapered profile TSVs and RDL

Followed by solder bumping and flip chip

huegging@physik.uni-bonn.de

#### **Bonn/IZM TSV experience**

universität**bonn**

# TSV modules using FE-I4 (ATLAS IBL chip): $160\mu$ m thick, 2 x 2 cm<sup>2</sup>

use straight vias with aspect ratio 3.5 : 1

Goal: demonstration of TSV/RDL processing together with solder bump bonding method on 8" FE-I4 wafers thinned to 160µm (3 wafer pilot run)

#### **Results:**

- first processing attempt failed (no connection to M1)

- reworking (!), however, was successful

- yield ... not quite satisfactory

# PoC project: Advanced Through Silicon Vias for Pixel Detectors

- Goal: establish high yield TSV + RDL process for pixel modules

- straight vias through (ultra?) thinned FE-I4 wafers and chips: note 2x2 cm<sup>2</sup> chip size

- 80 120 μm thickness (to be optimized),

- aspect ratio = 2 : 1

- one handle wafer step needed

- complete development including flip-chipping process for the final pixel module

#### **Challenges of the proposal**

- reliable TSV fabrication ... yield hoped/expected to be <u>much</u> better than for project 2

- thin (o(100 µm)) wafers are <u>needed</u> for the goal of "large yield" challenge is the handling of large and very thin wafers/chips

- surprises during flip-chipping can also be an issue

huegging@physik.uni-bonn.de

AIDA-2020 2nd Annual Meeting, Paris - 06/04/2017

huegging@physik.uni-bonn.de

with **TSVs**

11

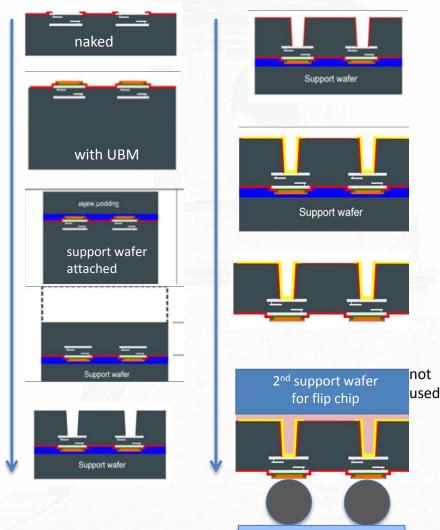

#### The approach in general

- Breakthrough for close to 100% yield multi TSV/backside RDL heterogeneous integration with high performance quality on small and medium production scales

- $\rightarrow$  benefits for many applications in CMOS tier stacking and for sensor/chip packaging applications

- **Specific applications** (beyond HL-LHC) in development with IZM

- 1) 4-side abuttable X-ray sensors (a la Medipix)

- 2) Backside processed (front side contact free) light and IR sensors

- 3) CMOS camera wafer level packaging with backside contacts  $\rightarrow$  used in endoscopy (medical) object lens camera module with flex

#### □ WP1:

Process optimization for very thin (80-120 μm) readout wafers

□ WP 2:

- Design optimization of the TSV and RDL layers

- **WP 3**:

- TSV run with optimized RDL design on FE-I4 wafer batch incl. electrical tests

- **W**P4:

- Optimization of bumping and flip-chip using (ultra?) thin TSV chips to sensors

- **WP** 5:

- Characterization of TSV chip sensor assemblies

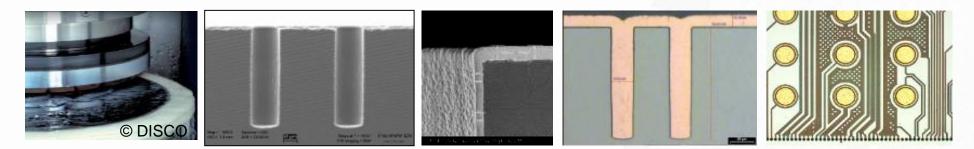

Through Silicon Via (TSV) Formation – Basic Process Steps

- 1. Wafer Thinning: Grinding, Wet Etching, DRIE

- 2. TSV Si-etching: DRIE BOSCH Process

- 3. TSV-Insulation: TEOS, PE-CVD, SA-CVD, Polymer

- 4. Adhesion-/Barrier-/Seed-Layer: Ti (TiW, TiN, Ta(N)) / Cu HI-PVD

- 5. Via filling: ECD Cu bottom up filling, liner filling

- 6. RDL / UBM pad metallization

All pictures courtesy of Fraunhofer IZM, Berlin.

huegging@physik.uni-bonn.de

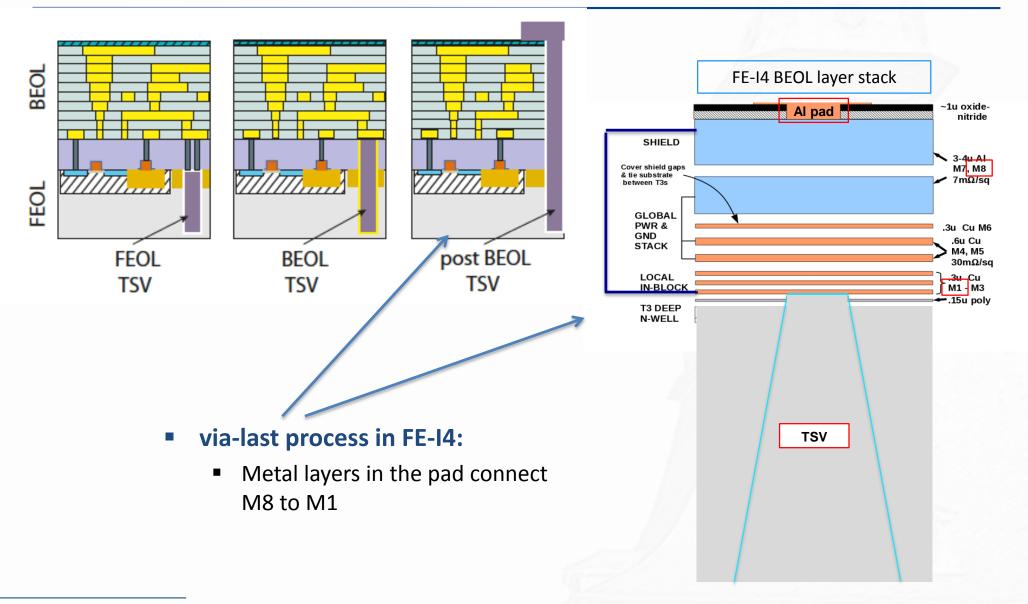

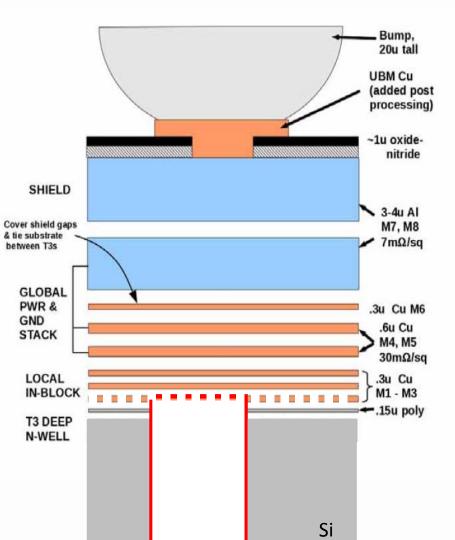

# **TSV Via Backside – Via Last Process**

TSV and Oxide Etch Process

TSV from backside:

- Etch: Si / oxide / Poly-Si / oxide

- stop on M1 (cheesed M1)

- PECVD oxide deposition

- Oxide etch

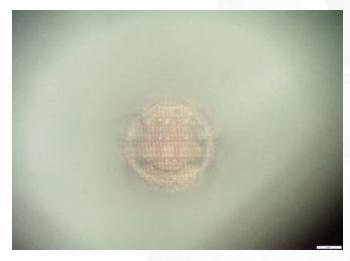

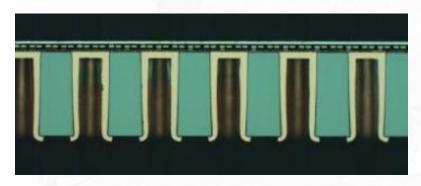

TSV after silicon / Oxide etch (500x): microscopic view into TSV AR2-3/ diam.60µm

- $\rightarrow$  cheesed/meshed M1

- $\rightarrow$  oxide opened?

- ightarrow harder decision for smaller diameter

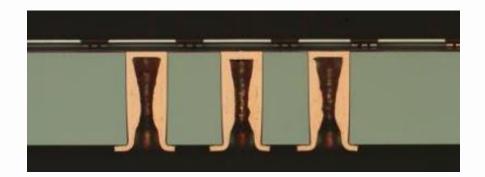

**TSV Filling Process by Electroplating**

- IZM ATLAS FE-I4 TSV Phase 2:

- First setup with not optimized via filling parameters

→ TSV filling tends to close the TSV at half of the TSV depth

- Rework + second fill

- Final cross section of TSVs after rework of the first via filling process step and 2nd filling

- MEDIPIX3 TSV Pilot Batch:

- same IBM technology, same wafer size

- Cross section of TSVs with optimized via filling process

- TSV process already OK after first setup

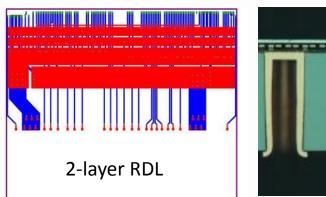

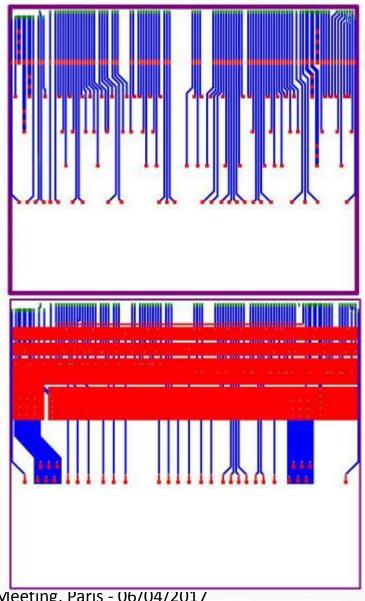

#### **RDL designs of the FE-I4 TSV chips**

- Two different RDL designs are used for the FE-I4 chips with TSV:

- simple design with one metal layer as for the Fe-I2/3 modules

- a more complex RDL layout features 2 metal layers with an additional BCB passivation between the metal layers

→ takes over some of the functionality of the module flex (power distribution etc., only passive components are missing but can be added later)

- both RDL designs are compatible with advanced laser soldering techniques

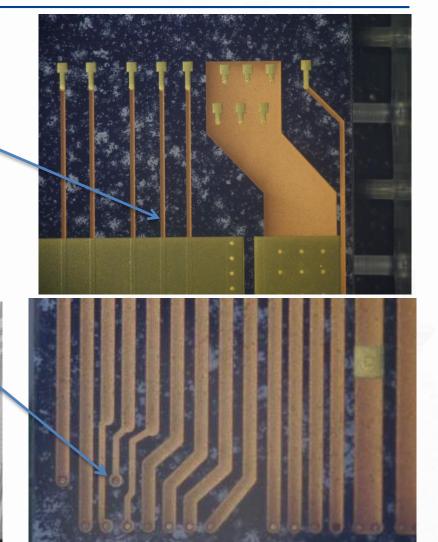

#### **RDL structuring and visual inspection**

- Inspected chips chips showed good processing results regarding RDL processing:

- good shape of the RDL layers (Cu and NiAu) and clear vias

- X-ray image shows good metal coverage over full TSV depth

Backside discoloration pattern due to rework process

**Cu-RDL** lines

Cu-filled TSVs

X-ray check of TSV filling and RDL-connection:

NiAu – solder/wire bond pads

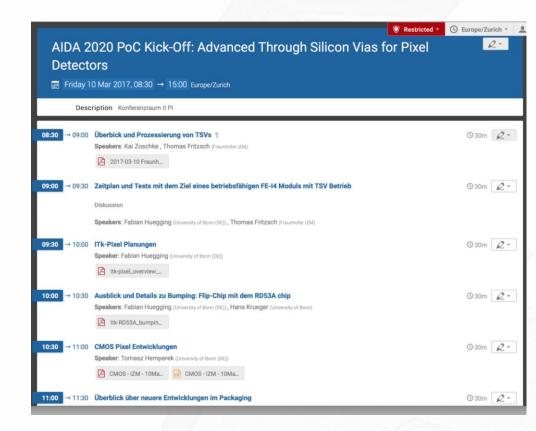

# **Kick-off Meeting of TSV project**

- Kick-off Meeting for the project in Bonn at 10/03/2017

- Project partner (U Bonn and IZM) agreed upon the implementation plan

- First actions about the next steps discussed:

- Lessons learned from the previous experiences

- TSV setup run process optimization

- design of dedicated test structures for TSV setup run → special structures for measuring capacitance and inductance of TSV and RDL layers

### ATLAS FE-I4 TSV Work Planning

WP1: TSV process step evaluation

- Fabrication of process setup wafer with dedicated test structures

- Evaluation of individual process steps (wafer thinning, TSV etching, passivation and RDL layer deposition) ٠

- Characterization of test structures ٠

WP2: TSV wafer design and mask fabrication

- Development of gds2 wafer layout mask set (TSV etch, passivation etch, RDL structuring, ...) ٠

- Fabrication of lithography glass masks ٠

#### WP3: ATLAS FE-I4 batch TSV process

- UBM deposition on the wafer front side, ٠

- thinning of the wafer ٠

- bonding of the thinned wafer onto carrier ٠

- backside processing including TSV etch, deposition of passivation, plating base TSV filling and RDL multi-layer •

AIDA-2020 2nd Annual Meeting, Paris - 06/04/2017

#### WP4: Flip chip bonding process

- Assembly of setup modules and optimization of bonding parameters ٠

- Characterization of bonding interfaces and bonding yield ٠

- Assembly of functional modules ٠

WP5: Characterization of TSV chip sensor assemblies

- Initial functional tests and tuning ٠

- Full characterization of TSV pixel detector modules in lab and at test beams ٠

August to October 2017

November to December 2017

#### June to July 2017

March to May 2017

#### WP1 – Process Modifications:

•Reduced wafer thickness:  $160\mu m \rightarrow 120...90\mu m$ :

- + better visibility of via bottom after TSV etch / oxide etch

- + improvement of TSV filling behaviour

- higher risk of wafer breakage

• Fabrication of TSV Daisy Chain Testwafer with dedicated M1 setup layer:

- +/- setup of TSV etch process but without poly-Si layer

- additional wafer fabrication (process steps)

Test of backside carrier wafer process:

- + higher stability up to dicing process

- + stabilisation of FE-I4 chip during flip chip process

- carrier release after flip chip assembly

- more cleaning steps necessary

#### Conclusions

- U Bonn and IZM have long term relationship for bump bonding of hybrid pixel detectors including post processing of Readout IC wafers.

- Experience of usage of post process TSV for pixel detectors already for some years with quite some success.

- Goal is to generalize this approach not only for HEP pixel detectors but also for industrial similar detector projects like imager or compact CMOS cameras

- A versatile via last TSV process with straight side vias on IO pads and a multi-layer RDL is being developed for the ATLAS FE-I4 Pixel Detector as Proof-of-Concept

- Project started with a Kick-off Meeting on March 10, 2017 and currently a setup TSV run is prepared to find optimal processing parameters for the TSV process.

huegging@physik.uni-bonn.de