S. Centro (ICARUS Collaboration)

Università di Padova / INFN Padova

European Strategy for Future Neutrino Physics CERN, 1-3 October 2009

### **Outline**

- Charge signals from liquid Argon TPC

- Characteristics and critical issues

- A proven architecture

- Toward updated schemes

- Light signals from liquid & gaseous Argon

- Characteristics and critical issues

- Basic DAQ architecture

### The ICARUS-like read-out

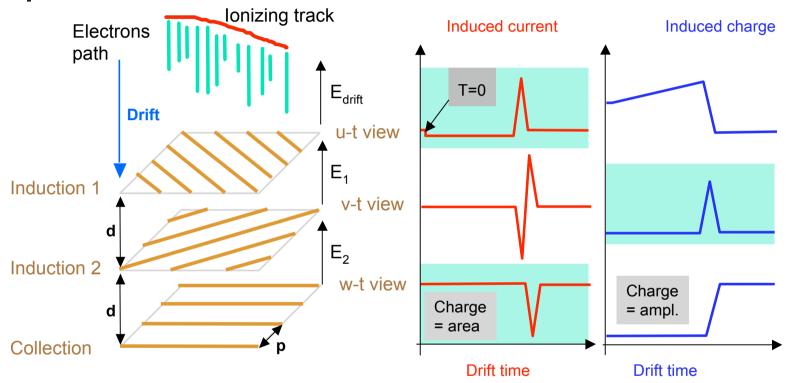

# The induction/collection signals

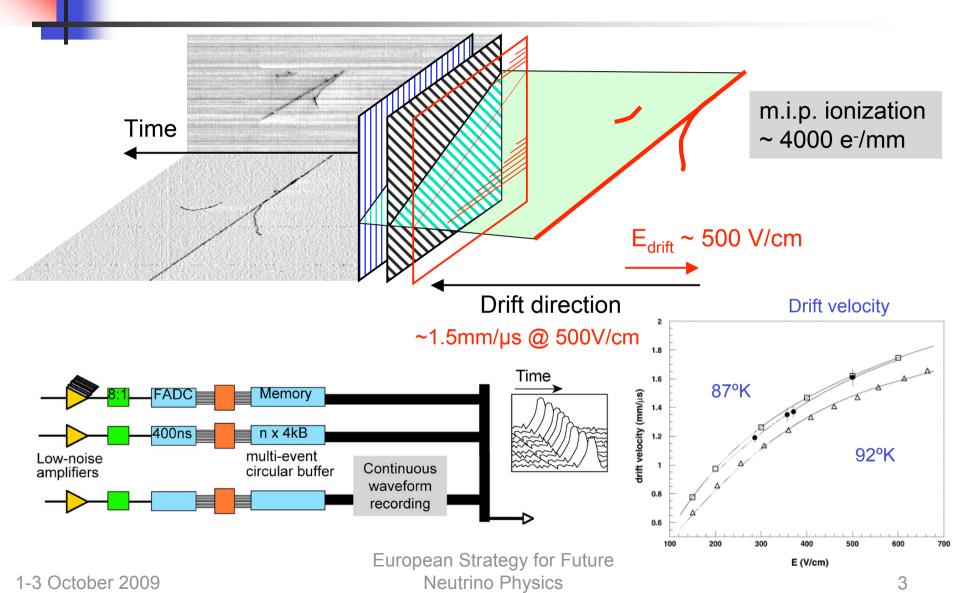

• ICARUS T600: three wire planes (pitch 3mm, separation 3mm)

$E_{drift}$  = 500 V/cm Mip signal ~ 12000 e<sup>-</sup> (inc. recombinantion) Electron drift velocity ~ 1.5 mm/ $\mu$ s Typical grid transit time ~ 2-3  $\mu$ s

# **Induction** signals require different treatment, but proper filtering makes the signal shape very much the same.

European Strategy for Future Neutrino Physics

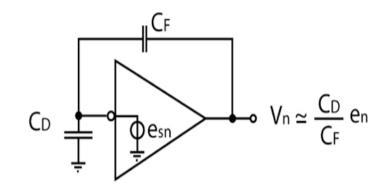

## Preamplifier for LAr TPC

- Need of very low noise amplifier:

- No amplification around sense wires

Collected charge ~ 10<sup>4</sup> electrons/mip

- Large input capacitance (C<sub>D</sub>)

- Wires (20 pF/m)\* + cables (50 pF/m)

- In T600  $C_D \sim 300-400 pF$

- Serial noise (proportional to C<sub>D</sub>)

dominates over parallel noise

(proportional only to signal bandwidth)

- High trans-conductance  $(g_m)$  input devices are required to ensure acceptable Signal-to-Noise level (S/N ≥ 10)

$$e_{sn}^2 \propto \frac{1}{g_m}T$$

<sup>\* 3</sup>mm wire pitch

# Choice of the active input device

- Bipolar transistors

- $g_m \approx 400 \text{mS}$  @  $I_c \approx 10 \text{ mA}$  (Amplification merit factor  $g_m \cdot Z_{out} \approx 10^5$ )

- BUT: parallel noise density ≈ 2 pA / √ Hz too high (with a typical LAr signal bandwidth of ~ 1 MHz gives unacceptable noise contribution)

- jFET

- Good  $g_m \approx 40$ mS @  $I_{ds} \approx 10$  mA (Amplif. **merit factor**  $g_m \cdot Z_{out} \approx 10^4$ )

- negligible parallel noise density ≈ 0.001 pA / √ Hz

- VLSI-CMOS

- Lower  $g_{m_i}$  (Amplif. merit factor  $g_m \cdot Z_{out} \approx 10^3$ )

jFET was the ICARUS choice : charge sensitive preamplifier with high  $g_m$  **2-jFET input** stage

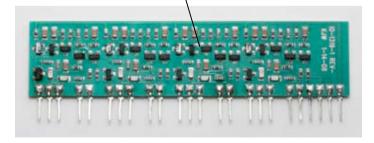

# The ICARUS T600 preamplifier

#### Custom IC in BiCMOS technology

- Classical unfolded cascode integrator

- External input stage jFET's

- Two IF4500 (Interfet) or BF861/2/3 (Philips) in parallel to increase g<sub>m</sub> (50-60 mS)

- External feedback network

- Allow sensitivity and decay time optimization

- High value f.b. resistor (100MΩ) reduce parallel noise

#### Two channels per IC

symmetrical layout guarantees identical electrical behavior Two versions:

"quasi-current" mode:  $R_fC_f \approx 1.6\mu s$  (collection + first induction)

"quasi-charge" mode:  $R_fC_f \approx 30\mu s$  (mid induction)

Sensitivity  $\approx$  6 mV/fC Dynamic range > 200 fC Linearity < 0.5% @ full scale Gain 6.5±.5 mV/fC, Gain uniformity < 3% E.N.C.  $\approx$  (350 + 2.5 x C<sub>D</sub>) el  $\approx$  1200 el. @ 400pF Power consumption  $\approx$  40 mW 1LSB = 1 mV

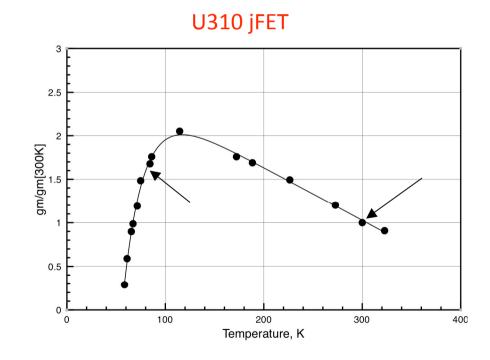

### Electronics in LAr?

#### Deeply investigated within ICARUS collaboration (since 1988)

- Limited choice of active devices working at LAr temperature

- GAs-jFET (High Electron Mobility Transistor technology)

- Silicon jFET (High Resistive Substrate technology)

- CMOS very low temp. **now** available but...

- Issues:

- Better S/N due to improved g<sub>m</sub> at cryogenic temperature

- Reliability at LAr temperature

- Availability on the market

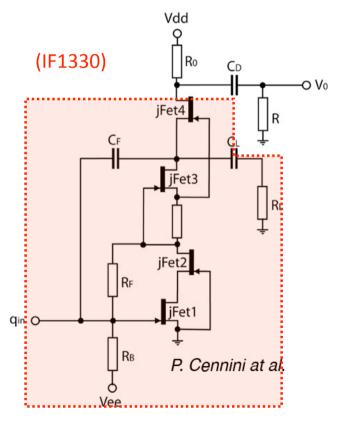

### The TOTEM architecture

- Charge Integrator made on Thick Film Hybrid technology with discrete jFET only

- Minimum active and passive components

- Ability to drive long transmission line

- Reduced power consumption

- Minimum cable connections

- Current signal from Positive Power Supply

- Common Negative polarization

- Characteristics

- Optimized for low detector capacitance

Sensitivity  $\approx 0.45$  mV/fC (0.9  $\mu$ A/fC) Dynamic range  $\pm 1.5$  pC Linearity < 0.5% @ full scale Input impedance  $\approx 420 \ \Omega$ Input capacitance  $\approx 20$  pF E.N.C.  $\approx (390 + 7 \times C_D)$  el Power consumption  $\approx 11$  mW

$$V_0 = \frac{R_0}{R_L} * \frac{q_{in}}{C_F}$$

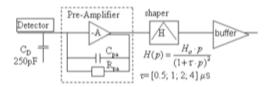

## MicroBooNE: cryogenic front-end

#### Electronics chain

JFet discrete amplifier

Several years of experience in NA-34 & NA-48

#### CNRS/IN2P3/UCBL

Step 2) (2008) on the basis of the experience acquired during the first phase, new version (TOPEST) integrating also the shaper+buffer, 8 channels + single components for characterization.

Received at the end of July 2008. Tests at IPNL. Typical total gain 7.5 mV/fC,

40 mip dynamic range.

selectable:

feedback capacitance (500 fF-1 pf) feedback resistor (2 - 10 M $\Omega$ )

- selectable shaping times (0.5 4 µs range)

- power switching on-off

Step 3) (End 2008), detector tests 64 channels:

study noise vs track reconstruction as a function of angles and shaping times

#### **Private communication:**

$g_{m} = 117 \text{ mS}$   $i_{d} = 8.655 \text{mA}$   $W_{tot} = 8100 \mu \text{W}$  $L = 0.35 \mu$

g = 10 (gates)

Noise=1000e @ Cd 250pF ??

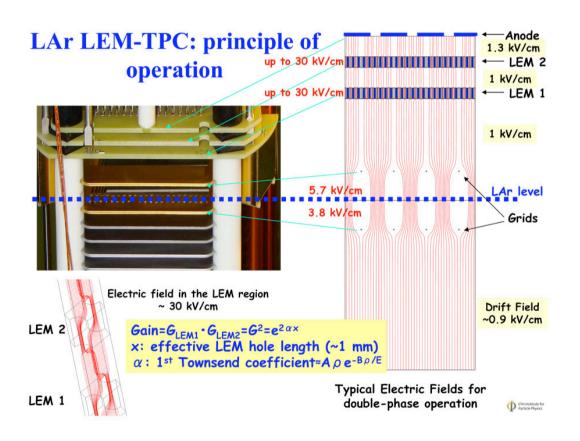

### Double phase Ar detectors

Double phase detectors enhance charge generated in liquid.

Similar signal shape

S/N intrinsically higher

Previous issues also apply

### Pro & Contra cold amps

#### Advantages

- Reduction of input capacitance due to cable absence

- Reduction of micro-phonic noise (detector = Faraday cage)

- Improvement of S/N [~ 2.4] due the combined effect of lower [~1.9] Johnson noise and higher [~1.26] g<sub>m</sub> @ 86°K

#### Disadvantages

- Inaccessibility during detector operation

- Need of careful selection of components, extensive burn-in and temperature cycles before installation to minimize components failure

- Design architecture and technology restricted by limited choice of active components

- Limit on power dissipation (< 100 mW/cm<sup>2</sup> to avoid LAr boil-off)

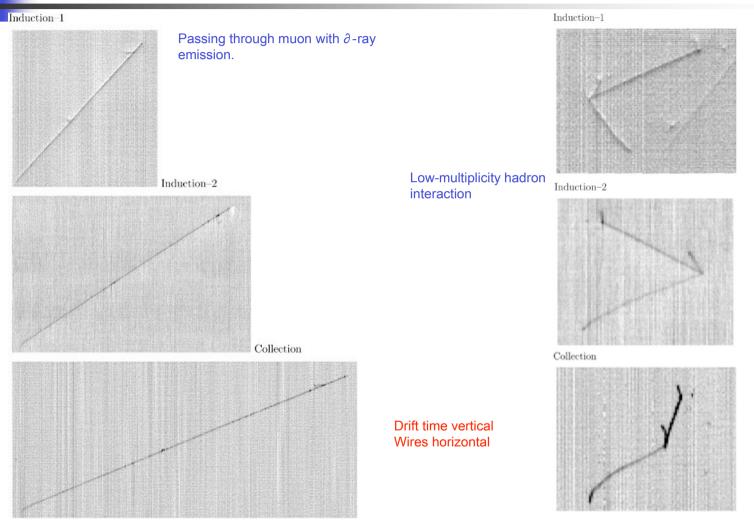

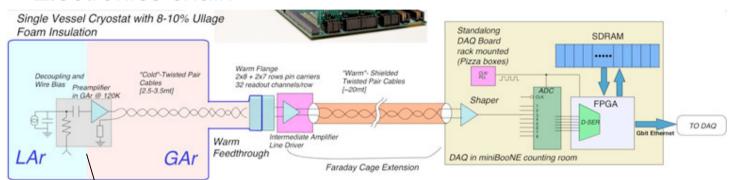

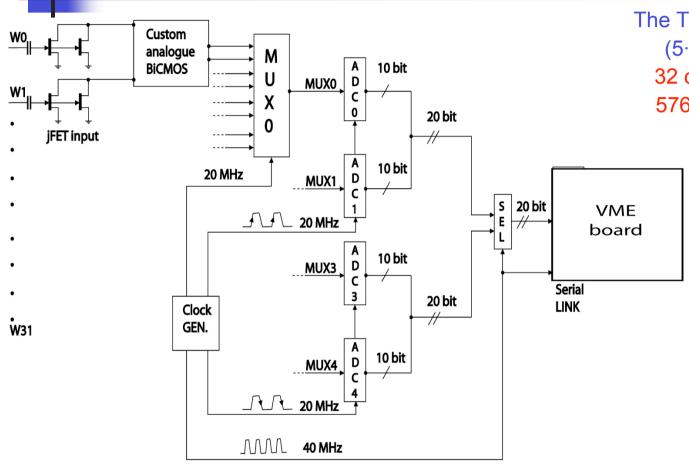

# The ICARUS T600 experience

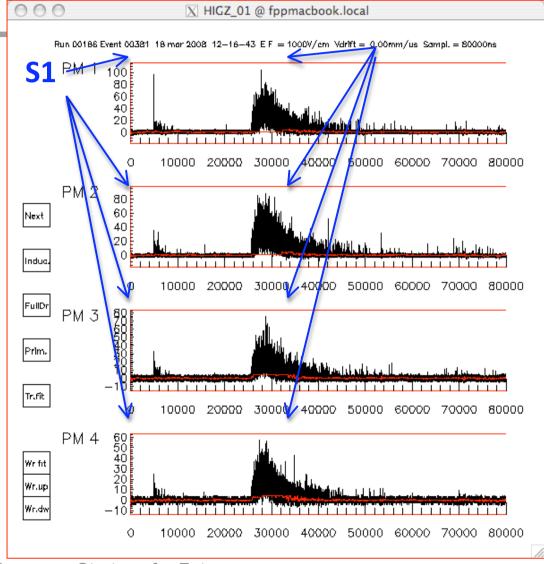

- Analogue front-end followed by a multiplexed ADC (1LSB≅1000e<sup>-</sup>) whose output is stored in RAM: waveform recorder.

- Digital VME module performs local storage, hit finding and facor 4 data compression (recent improvement).

# T600 DAQ block diagram

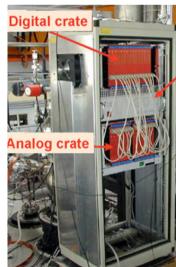

The T600 DAQ system (5·10<sup>4</sup> channels)

32 channels/board

576 channels/rack

### Signals and noise in large TPC

- In a multi-kton TPC we can foresee wires with a pitch larger than the 3mm used in the T600

- The adoption of 6mm pitch for a large TPC seems reasonable and

- A realistic capacitance value for 10*m* electrode wires, 6*mm* pitch, and average 8*m* of cable is ~600*pF* (cfr.: 300-400*pF* in the T600)

- It follows that the Signal to Noise Ratio should be very similar to that of the T600.

- Hence a completely new design of the analogue frontend would hardly improve the performance

### AD conversion

- Serial ADC are now preferable over Flash ADC.

- To reach the 3MHz sampling rate, AD must be clocked at 48MHz.

- Mini Small Outline Package (MSOP) smaller than 5x5 mm<sup>2</sup>. Many house 2 or even 4 channels. Competitive in price and power consumption.

- We can assume a resolution of 10bit but 12bit ADCs are also available at reasonable cost. More components available soon.

### **Available Serial ADC**

|   | Manufacturer      | Res | Part. Num. | Freq.<br><i>MHz</i> | Power mW typ. | Supply     | Cost \$ 1000 pcs |

|---|-------------------|-----|------------|---------------------|---------------|------------|------------------|

| • | Analog Devices    | 10  | AD7273     | 3                   | 11.4          | 2.35 – 3.6 | 3.75             |

|   | Analog Devices    | 10  | AD7277     | 3                   | 10.5          | 2.35 – 3.6 | 3.60             |

|   | Maxim             | 10  | MAX1334    | 4.5                 | 40            | 5, 3.3     | NA               |

|   | Maxim             | 10  | MAX1335    | 4                   | 40            | 3.3        | NA               |

|   | Analog Devices    | 12  | AD7274     | 3                   | 11.4          | 2.35 – 3.6 | 3.75             |

|   | Analog Devices    | 12  | AD7276     | 3                   | 10.5          | 2.35 – 3.6 | 4.0 – 6.25       |

|   | Linear Technology | 12  | LTC1403-1  | 2.8                 | 14            | 2.7 – 3.3  | 4.00             |

|   | Maxim             | 12  | MAX1332    | 3                   | 38            | 5, 3.3     | NA               |

|   | Linear Technology | 14  | LTC1403A-1 | 2.8                 | 14            | 2.7 – 3.3  | 7.00             |

|   | Analog Devices    | 16  | AD7621     | 3                   | 86            | 2.5        | 29.95            |

The frequency given in the table refers to the sampling rate.

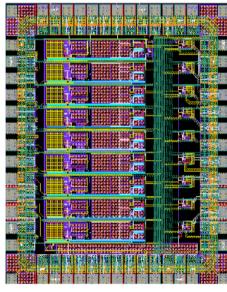

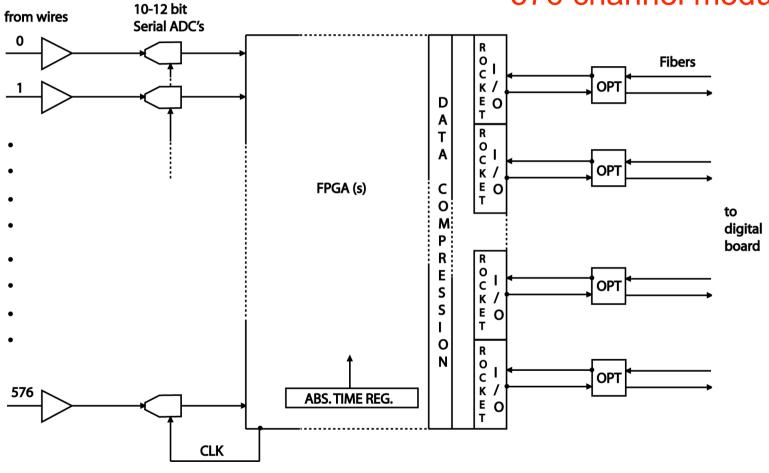

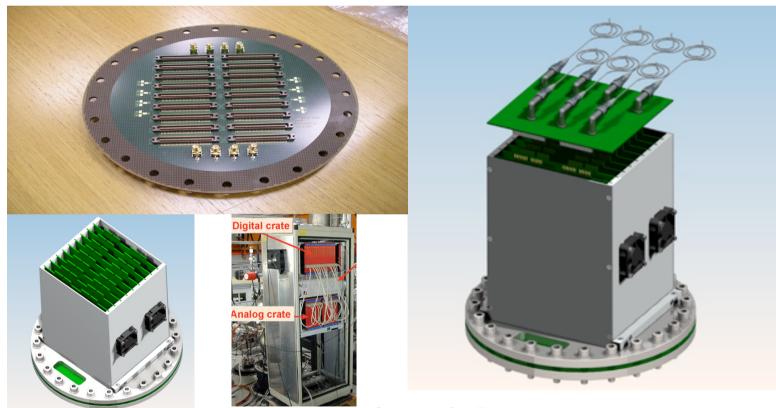

# Compact architecture

#### 576 channel module

### New data distribution

- A set of a few FPGA for 576 channels (one flange) will be used to handle, filter, and organize the serial information provided by the serial ADC's.

- Assuming a sampling frequency of 1.5*Mhz*, 10*bit* ADC's we need to transmit ~8 G*bit*/s, (including error correction redundancy).

- Optical links with 1.5Gbit/s data rates are standards and can be driven by suitable interfaces available on FPGA from different vendors.

- Six optical links could serve all the channels of one module (576) and convey also extra information as absolute time.

- The architecture of the DAQ system can be enhanced through the adoption of a modern switched I/O allowing the parallelization of the serial data flows.

# New electronics layout

- The whole electronics of ~600 channels can be hosted in a compact crate (~12 liter volume) incorporating the feed-through flange that forms a sort of backplane.

- External cables will be essentially eliminated.

### Conclusions on charge read-out

- The ICARUS DAQ basic architecture is well suited even for larger size LAr-TPC (single phase);

- Similar structures adopted by other projects. Differences limited to the front-end choice: cold versus warm.

- Main upgrades concern:

- More compact version of the front-end amplifier

- Adoption of high frequency serial ADCs

- Housing and integration electronics on detector

- Optical links for Gbit/s transmission rate

### Photo-detectors readout

Ionization in **liquid** Argon (LAr) is accompanied by **scintillation light emission**.

The two processes are **complementary** through recombination and their relative weight depends on the strength of **the electric field** and **dE/dx**.

Electron and photon yield similar ( $Y_{ion} = \sim 2.9*10^4 \text{ e}^-\text{/MeV}$ ,  $Y_{ph} = \sim 2.4*10^4 \text{ g}^-\text{/MeV}$  @ 500v/cm for *mip*).

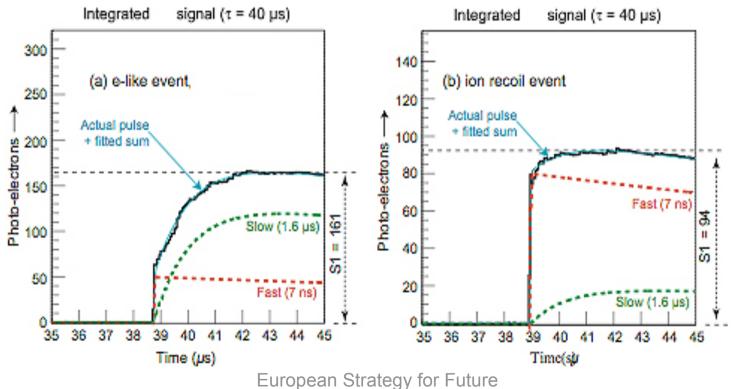

Light is emitted at 128nm (detection generally through wave-shifting) with **two-component** exponential decay ( $\tau_s \sim 6$  ns and  $\tau_L \sim 1.5 \mu$ s).

Prompt light signal typically used for **trigger** (eg. lcarus) or for **calorimetry/particle identification** (eg. WArP).

### Example of light coll. in WArP

*mip*: ~25% of light **short time** constant ~75% **long time** constant.

*recoil:* ~75% of light **short time** constant ~25% **long time** constant.

**S2**

- S1 primary scintillation.

- S2 scintillation in gas phase proportional to extracted ionization electrons.

- Ionization electrons identified individually.

- Efficient alternative to direct charge measurement for tiny signals (few electrons)

- S1 and S2 have similar characteristics.

European Strategy for Future Neutrino Physics

#### Conclusion

Waveform recording based on high performance (expensive) commercial solution (≥1GHz-≥8bit, multi buffering) is well suited for signals provided by PMTs in single and double phase Ar detectors, allowing full measurement of the signal structure.

#### **Investment required:**

for low cost waveform recorders for experiments requiring high number of channels; for **on line data reduction**, **signal recognition**, **and trigger pre-processing** through high speed FPGAs.

Also **onto detector integration** would be a benefit (see first part).