# Improvement of planar silicon Pixel Sensors for the ATLAS ITk upgrade

BCD School Cargèse, April 5<sup>th</sup> 2017 Sascha Dungs

TU Dortmund, Experimentelle Physik IV

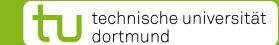

## **ATLAS Pixel Detector**

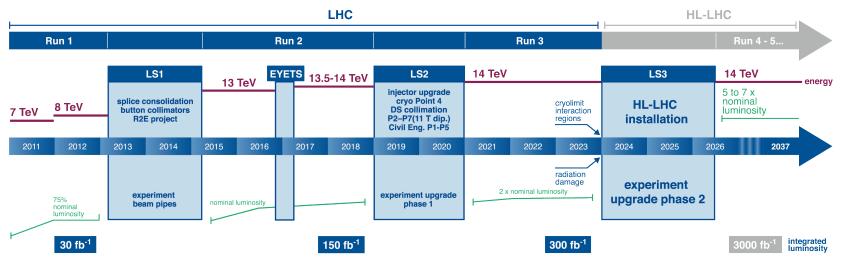

## LHC / HL-LHC Plan

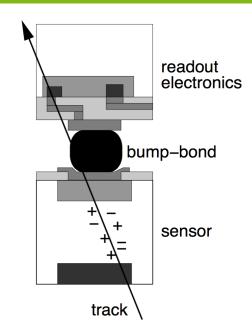

- currently the pixel detector consists of hybrid modules with n-in-n type pixel sensors

- for the phase 2 upgrade the inner detector will be replaced completely

- final layout is not set yet, but well-established hybrid concept is preferred

- n-in-p type pixel sensors could be a possible costeffective alternative for n-in-n sensors

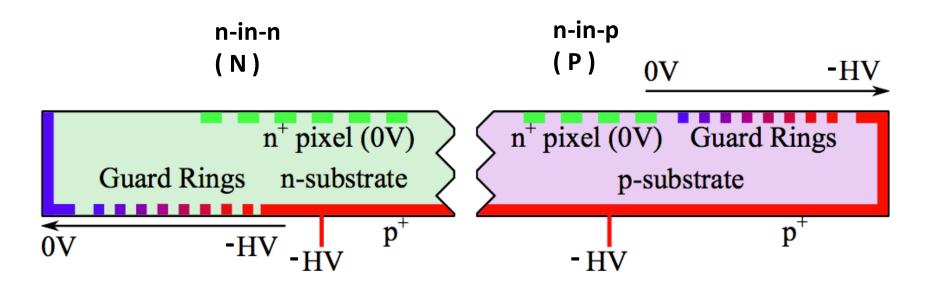

## **Sensor Types**

- n-type substrate

- GR on p-side

- two side processing

- front side: n⁺-implants (→ pixels)

- back side : p\*-implants

- Guard Rings for defined potential drop

- p-type substrate

- GR on n-side

- one side processing

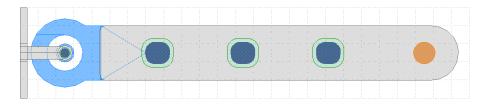

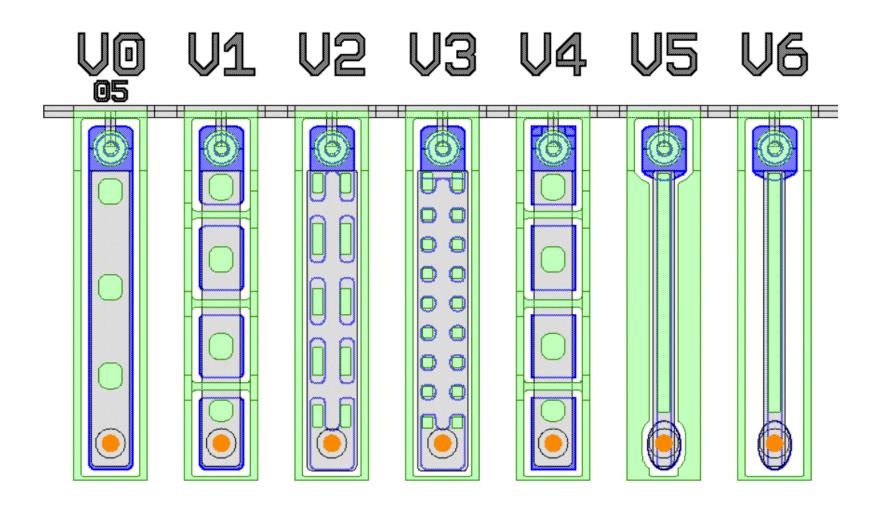

#### Design of new n-in-p sensors:

- efficiency improvements

- material reduction

- same design to compare the types

- new FE-Chip -> pixel size 50x50 μm<sup>2</sup>

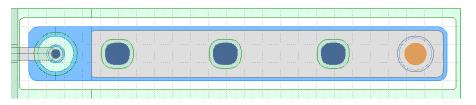

#### Standard n-in-n IBL pixel design (250x50 μm<sup>2</sup>)

#### Example for equivalent n-in-p pixel design

#### **Comparing measurements:**

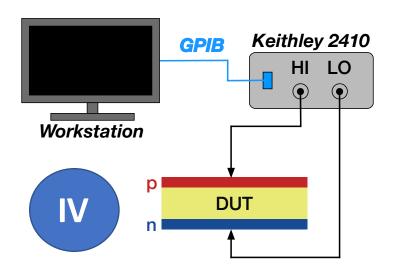

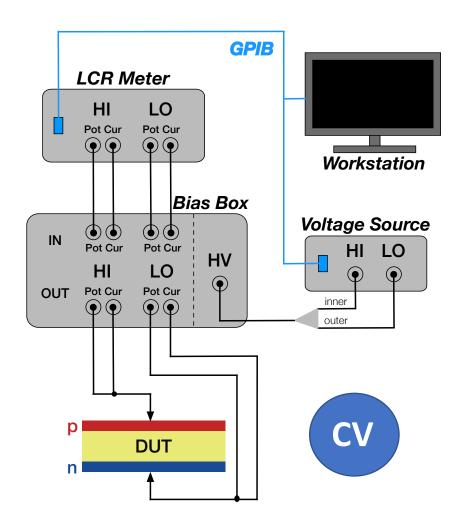

- IV and CV characterizations are done

- further measurements follow, e.g. hit efficiency

|                | D-01   | D-02   | M-01   | M-02   | M-03   |

|----------------|--------|--------|--------|--------|--------|

| manufacture    | CIS    | CIS    | HLL    | HLL    | CIS    |

| type           | n-in-n | n-in-n | n-in-p | n-in-p | n-in-p |

| thickness [µm] | 200    | 200    | 150    | 150    | 100    |

# Thank you for your attention!

# Backup

## **Setup for IV and CV Characterizations**

#### Criteria for good sensor:

- thickness ≤ 200μm

- leakage current:

- $I_{total} \le 0.75 \mu A/cm^2$  at 20°C  $\Rightarrow I_{max} \approx 2.5 \mu A$

- measured at V<sub>depl</sub> + 50 V

# **FE** specifications

|                   | RD53                  | FE-14                   |  |

|-------------------|-----------------------|-------------------------|--|

| technology        | 65 nm                 | 130 nm                  |  |

| Pixel dimension   | 50 μm x 50 μm         | 50 μm x 250 μm          |  |

| # of pixels       | ~140 000              | 26880                   |  |

| chip dimension    | 18 mm x 20 mm         | 19 mm x 20 mm           |  |

| hit rate          | 3 GHz/cm <sup>2</sup> | 0.4 GHz/cm <sup>2</sup> |  |

| in-time threshold | < 1000 e              | < 4000 e                |  |

| typ. noise (ENC)  | < 100 e               | < 300 e                 |  |

| bandwidth         | 5 Gb/s                | 160 Mb/s                |  |

| rad. hardness     | > 5 MGy               | > 2.5 MGy               |  |