# State of the art and perspectives of CMOS avalanche detectors

Lucio Pancheri

DII, University of Trento & TIFPA-INFN, Italy

**CERN** seminar

January 20, 2017

CERN, January 20, 2017

#### **Research on silicon detectors in Trento**

### Outline

- Introduction

- CMOS-integrated single-photon detectors: an overview

- APiX: Geiger-mode avalanche pixel detectors for ionizing particles

- Conclusion and future perspectives

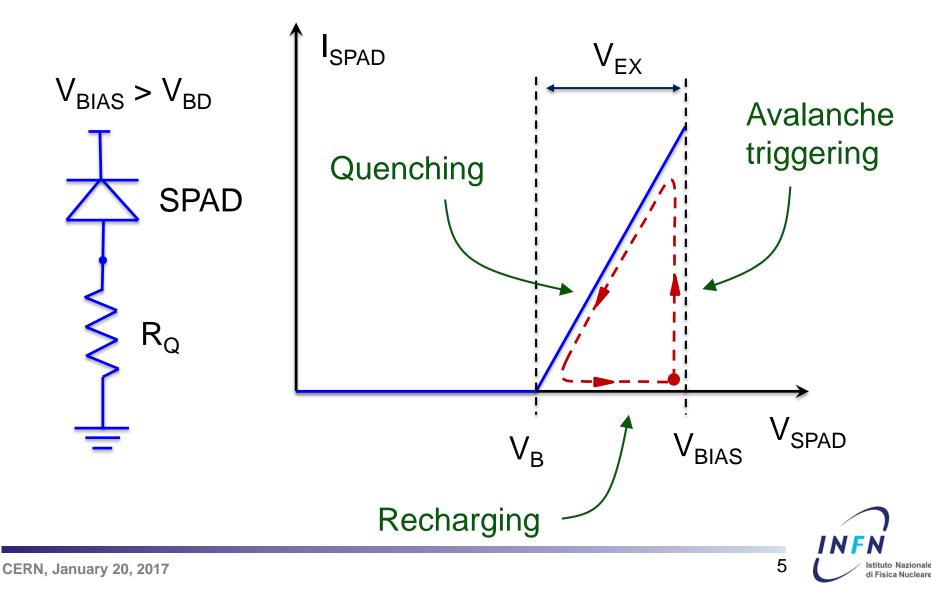

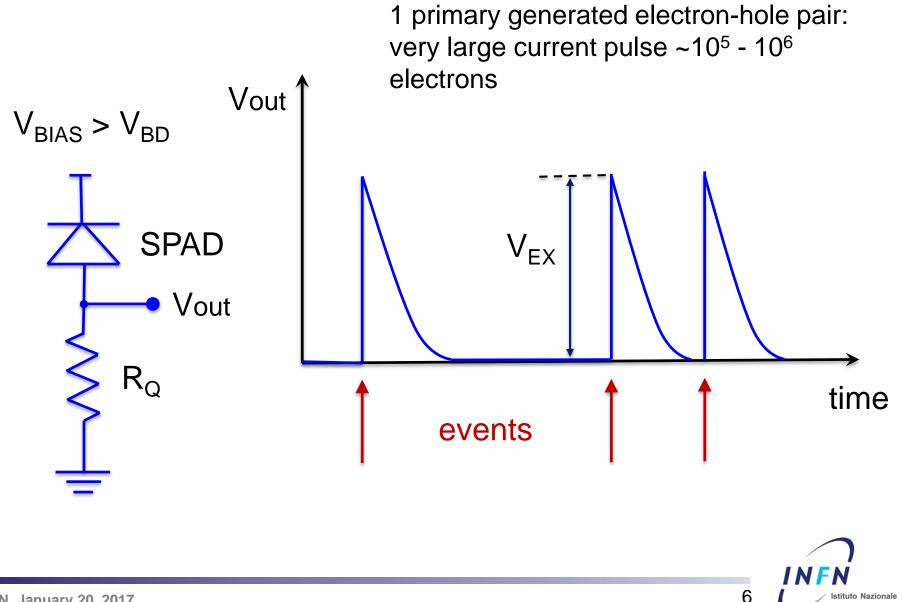

# **Geiger-mode avalanche detectors**

a.k.a. Single-Photon Avalanche Diodes (SPADs), SiPM cell

# **Geiger-mode avalanche detectors**

di Fisica Nucleare

# **CMOS SPAD characteristics**

#### **Features:**

- Single-photon sensitivity  $\rightarrow$  shot noise limited

- Excellent timing resolution: ~100 ps FWHM

### **Outline**

#### Introduction

- CMOS-integrated single-photon detectors: an overview

- APiX: Geiger-mode avalanche pixel detectors for ionizing particles

- Conclusion and future perspectives

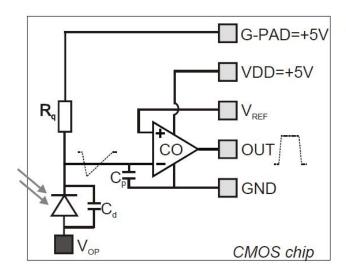

# **CMOS SPADs: early example at EPFL**

#### Process: **CMOS 0.8µm** Area: 30µm<sup>2</sup> Peak PDE: 20% DCR: 300 Hz Timing resolution: 50 ps FWHM

9

A. Rochas et al., Proc. SPIE 2003

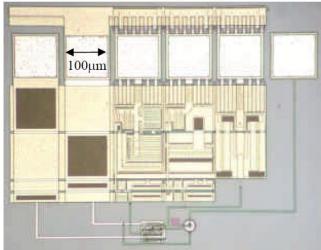

# **CMOS SPADs: deep submicron**

10

Istituto Nazionale di Fisica Nucleare

J. Richardson et al., IEEE Trans. Electron Dev. 2011

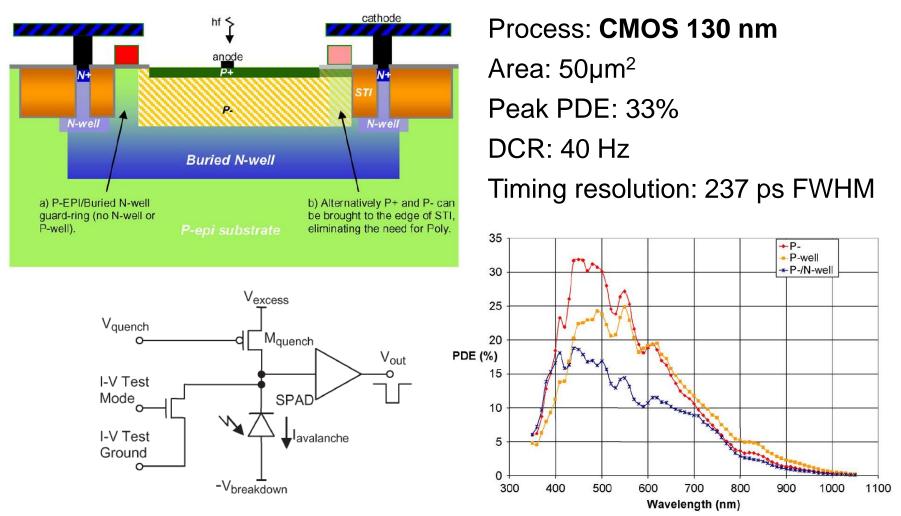

# **CMOS SPADs:** high efficiency

Process: CMOS 350nm Imaging with custom implantation Area: 700µm<sup>2</sup> Peak PDE: > 50% DCR: 50 Hz

Timing resolution: 142 ps FWHM

D. Bronzi et al., Proc. IEEE ESSDERC 2012

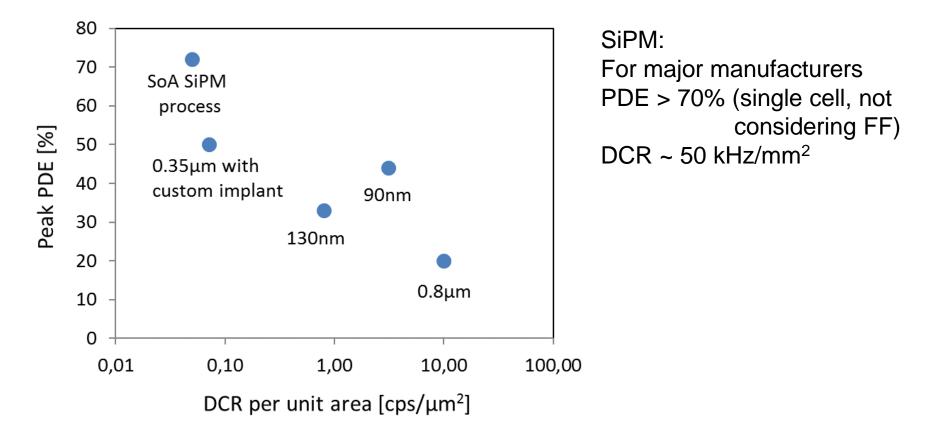

# Summary and comparison with SiPM

With customization, CMOS can approach SiPM performance

For a complete overview, see D. Bronzi, et al., IEEE Sensors J. 2016

# **SPAD** array applications

- Time-Of-Flight optical ranging, LIDAR

- Fluorescence spectroscopy

- Raman spectroscopy

- Gamma ray detection (PET)

- Quantum cryptography

# **Time-of-Flight optical ranging**

Automotive LIDAR developed by Toyota

- 180nm CMOS

- SPAD array with integrated TDCs

- 70% array Fill Factor

- Distance range: 100 m

C. Niclass et al., IEEE J. Solid-State Circuits, 2013

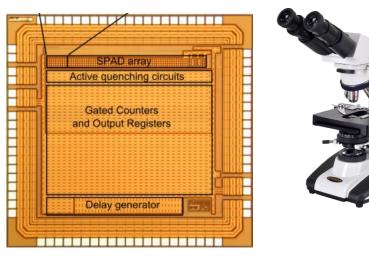

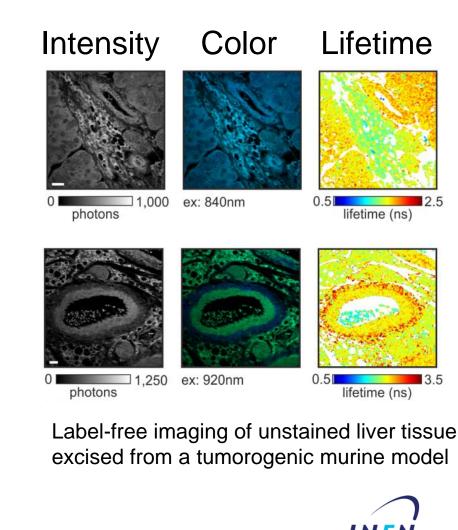

#### Multi-parametric fluorescence imaging

- 350nm CMOS (AMS)

- 4-line SPAD array

- Sub-ns gated counters

- 36% Fill Factor

M. Popleteeva et al., Opt. Expr, 2015

15

di Fisica Nucleare

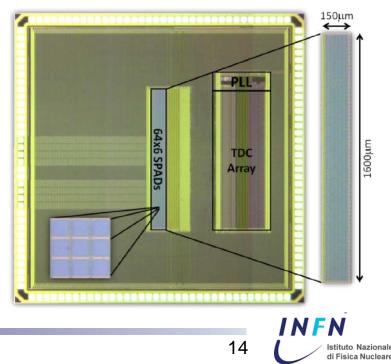

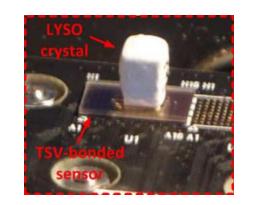

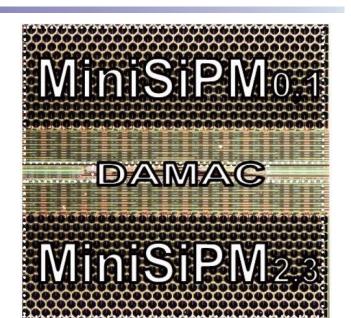

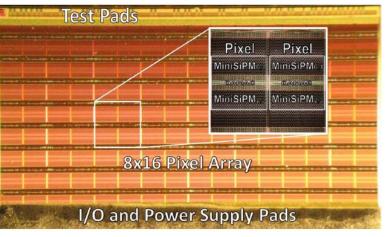

# **Digital SiPMs for PET**

SPADNET project (EU FP7)

- 130nm CMOS process

- Large pixels including 180 SPADs (Mini-SiPM)

- integrated TDCs

- 42.6 % pixel Fill Factor

16

L. Braga et al., IEEE J. Solid-State Circuits, 2014

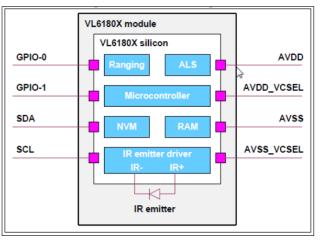

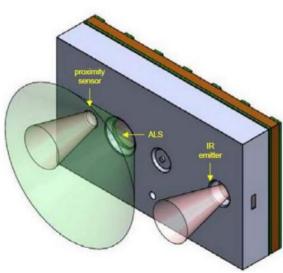

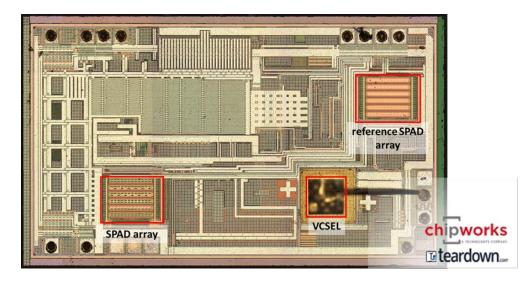

### First consumer products: ST ToF sensor

#### Proximity sensor based on SPAD array and pulsed VCSEL

- Presented in **2014**

- Mobile applications (mounted on iPhone7)

- Low power

- Short range (15 cm)

# **SPAD** image sensor

| I/O Serializer<br>I/O Serializer<br>I60x128 pixel<br>Array |  |

|------------------------------------------------------------|--|

| I/O Serializer                                             |  |

C. Veerappan et al., ISSCC 2011

MegaFrame EU project (FP6)

- 160 x 128 pixel array

- Technology: 130nm CMOS

- In-pixel Time-to-Digital Conv.

- 140ps timing resolution

- Pixel pitch: 50um

- Fill factor: 1%

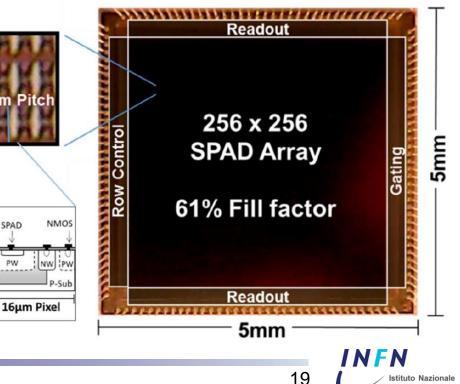

# Improving the Fill Factor

- 16µm x 16µm pixel

- 65nm CMOS

- binary pixel (7 transistors)

- SPAD deep nwell sharing

- Improved SPAD GR

IIM

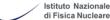

### **Deep APD**

#### Panasonic project

- 110nm CMOS

- Backside illumination

- Avalanche multiplication region below electronics

- Pixel pitch 3.8µm

- 4 transistors / pixel

- Linear and binary mode

#### M. Mori et al., ISSCC 2016

20

I N F N

Istituto Nazionale di Fisica Nucleare

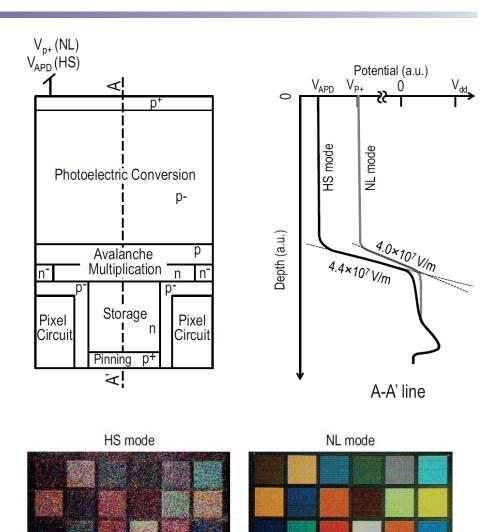

## **3D integration**

High density interconnections successfully demonstrated for image sensors

21

CERN, January 20, 2017

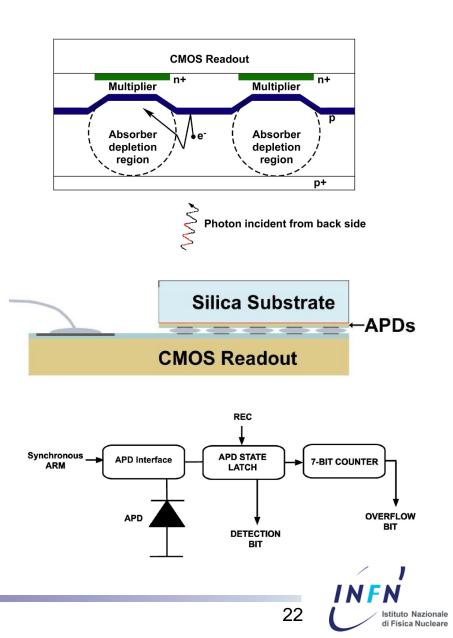

# **3D-integrated SPAD image sensor 1**

**MIT Lincoln Laboratory**

- 25µm pitch

- 180nm CMOS + custom (APDs)

- 7-bit counter/pixel

- Backside illumination

**10 - 20% detection efficiency** (limited by optical cross-talk)

B. Aull et al., IEEE Sensors J., 2015

# **3D-integrated SPAD image sensor 2**

- 7.83µm pitch

- 65nm CMOS (top) + 40nm CMOS (bottom)

- 2 6-bit counters/pixel

- Backside illumination

Backside N N N ΡΔΠ P-Substrate 7.83 µm Deep NW NW EP PW FPINM P-plus ┍╨ Top Tier HB-Top HB-Bot **Bot Tier Pixel Electronics** P-Substrate SPAD Top Tier Bottom Tier C1 Pulse Gating vo Logic C2 Exposure G1 G2 G3 GND **Thick Oxide** Ripple Counter **Ripple Counter** Pulse 6-bit 6-bit C1 T-Gate T-Gate RowSEL RowSEL Column Parallel Bus 23 Istituto Nazionale

di Fisica Nucleare

45% Fill Factor

### Outline

- Introduction

- CMOS-integrated single-photon detectors: an overview

- APiX: Geiger-mode avalanche pixel detectors for ionizing particles

- Conclusion and future perspectives

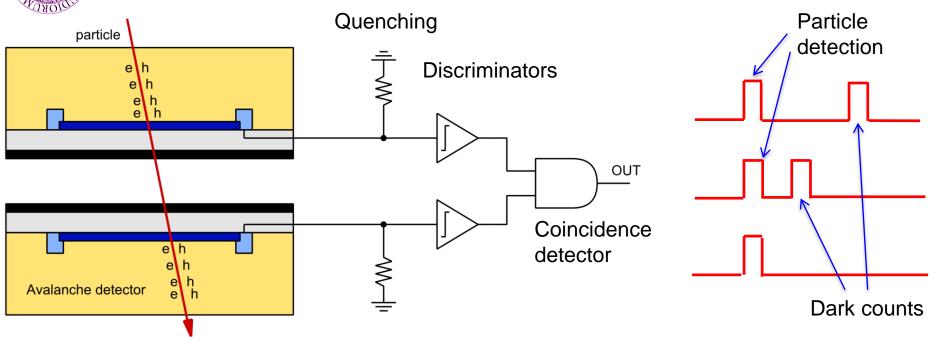

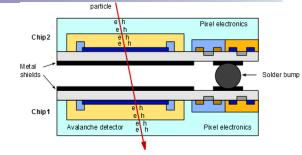

# **APiX particle detector concept**

Two Geiger-mode avalanche detectors in coincidence:

$DCR = DCR_1 \times DCR_2 \times 2\Delta T$

In-pixel coincidence: integrated electronics is needed:

CMOS avalanche detectors

V. Saveliev, US Patent. 8,269,181, 2012

N. D'Ascenzo et al., JINST 2014

25

CERN, January 20, 2017

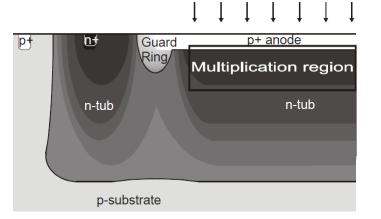

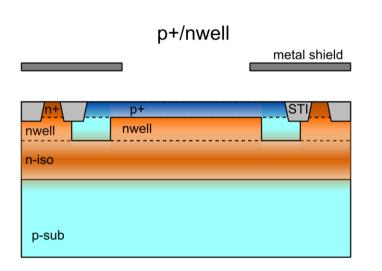

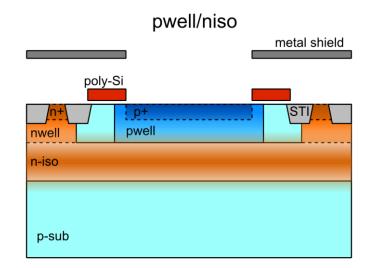

# SPADs in 150nm CMOS process

- Standard CMOS process no modifications

- Avalanche diodes in deep nwell: isolated from substrate

#### Type 1:

- Shallow step junction

- Active thickness ~ 1µm

#### Type2:

- Deep graded junction

- Active thickness ~ 1.5µm

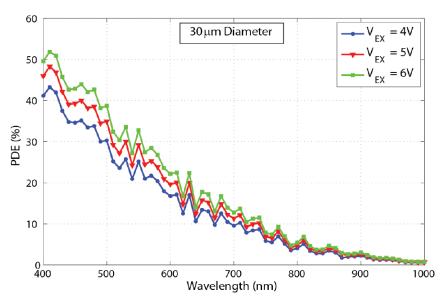

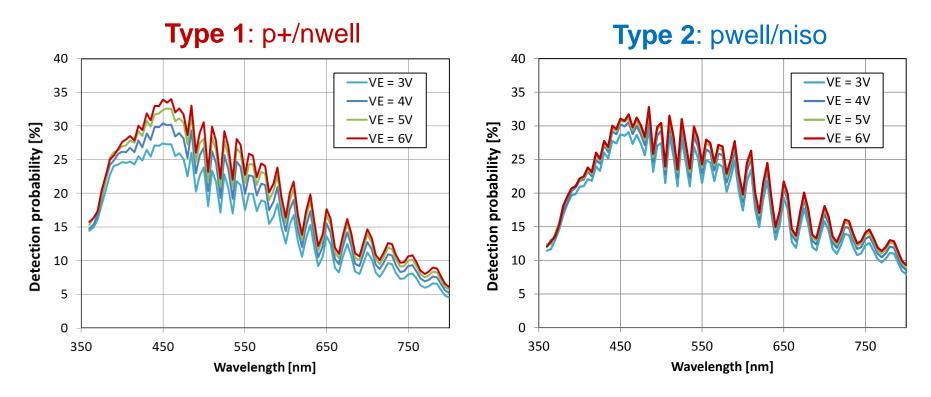

### **Photo-Detection Efficiency**

Shallower junction: better NUV – Blue efficiency

Wider depletion region: Better red-IR efficiency

L. Pancheri et al., J. Selected Topics in Quantum Electron, 2015

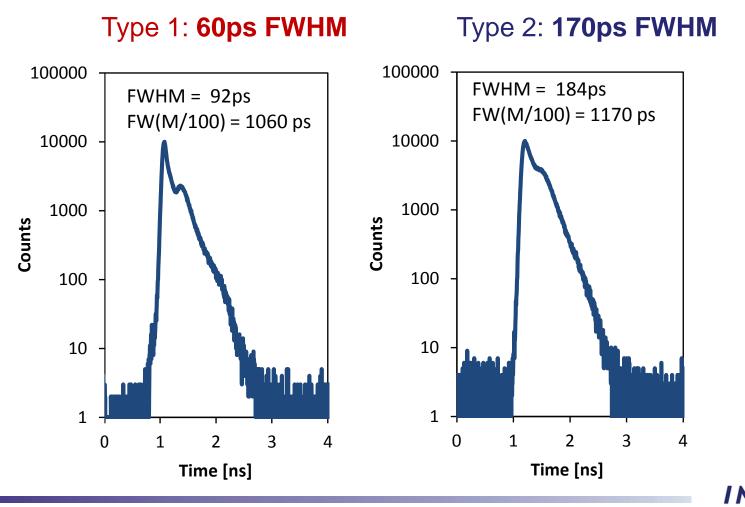

# **Single-photon timing resolution**

Measured on 10-µm devices, with blue laser (470nm), 70ps FWHM

28

Istituto Nazionale di Fisica Nucleare

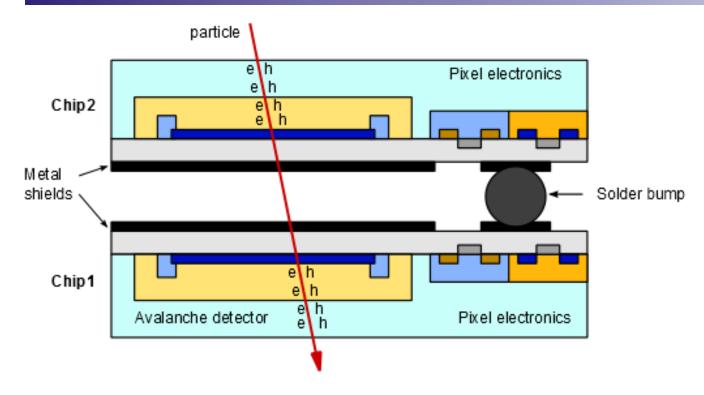

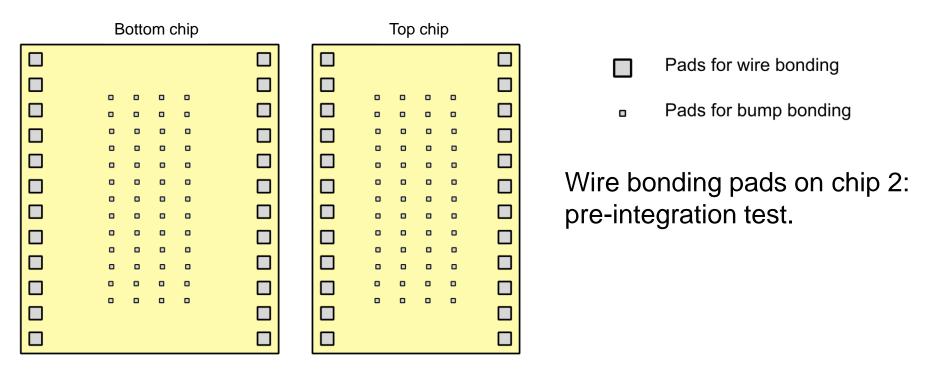

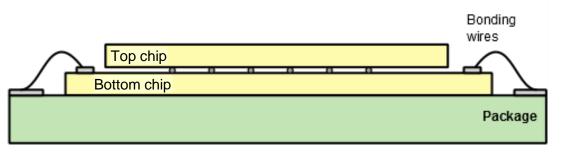

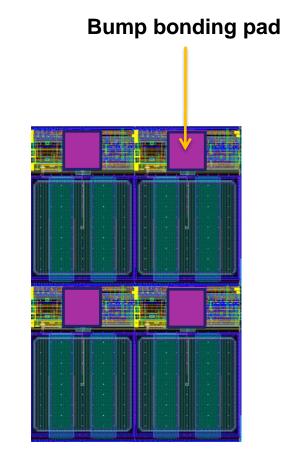

# **Proof-of-concept demonstrator**

2-layer pixel cross section:

- Electronic readout on both layers

- Metal shielding from optical cross-talk

- Vertical interconnection by **bump bonding**

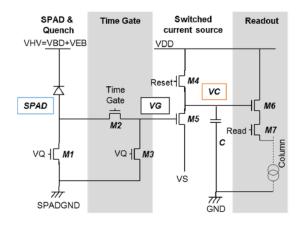

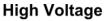

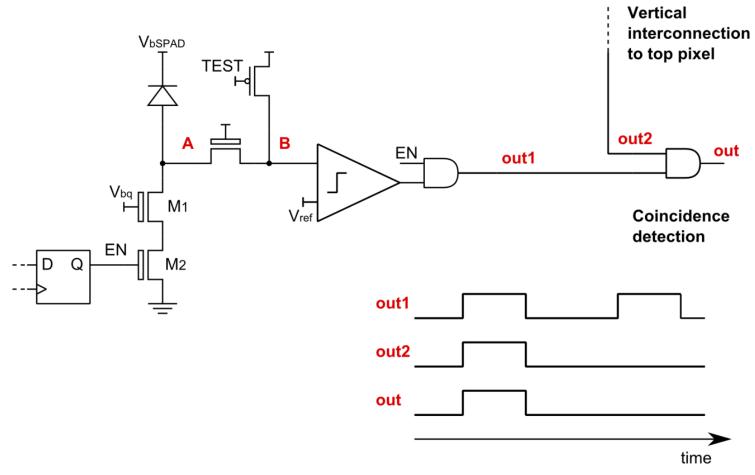

### **Pixel architecture**

- High voltage V<sub>bSPAD</sub> applied at nwell

- Maximum voltage at node A:  $V_{ov} = V_{bSPAD} V_{BD}$

- Small capacitance at node A

- Passive quenching with constant current recharge

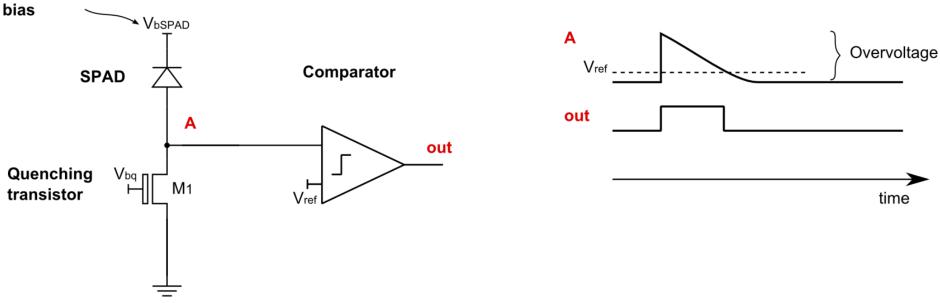

### **Pixel architecture**

- Front-end transistors: 3.3V → Maximum overvoltage 3.3V

- Digital circuitry: 1.8V compact fast low-power

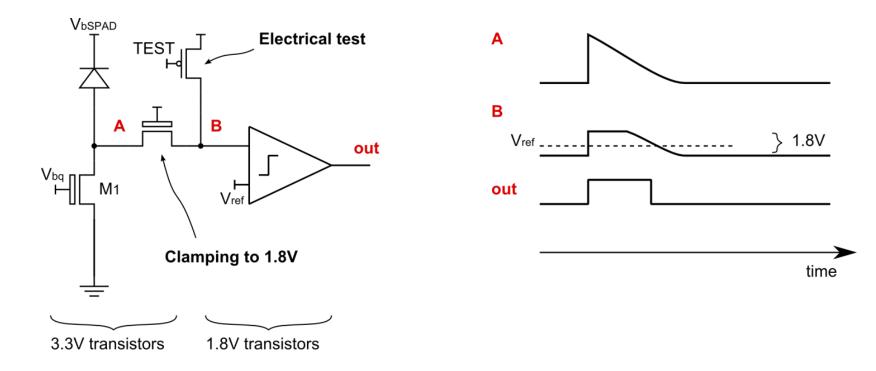

# **Pixel architecture: enable register**

#### Pixels can be **individually disabled**:

- M<sub>2</sub> disables recharge

- Output and gate blocks output pulses

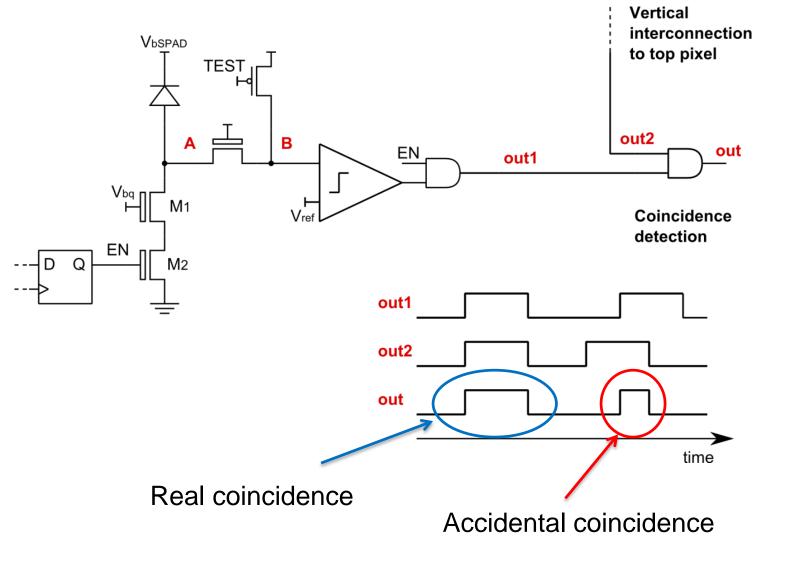

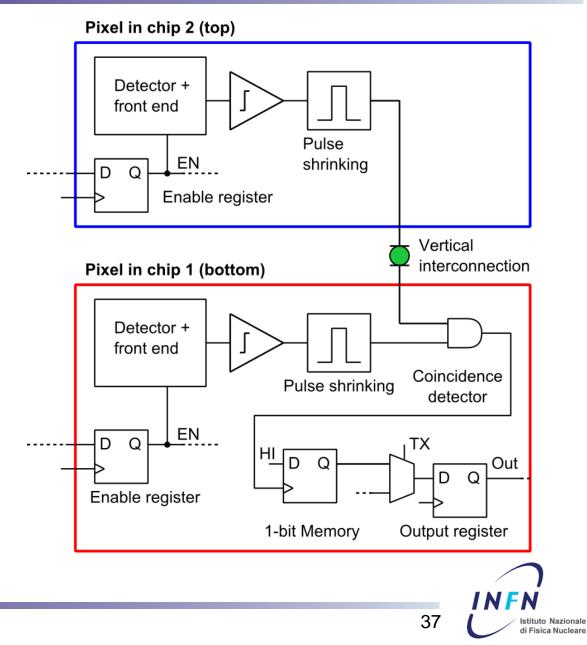

# **Pixel architecture: coincidence**

Coincidence with top-layer pixel

### **Pixel architecture: coincidence**

' N F N

Istituto Nazionale di Fisica Nucleare

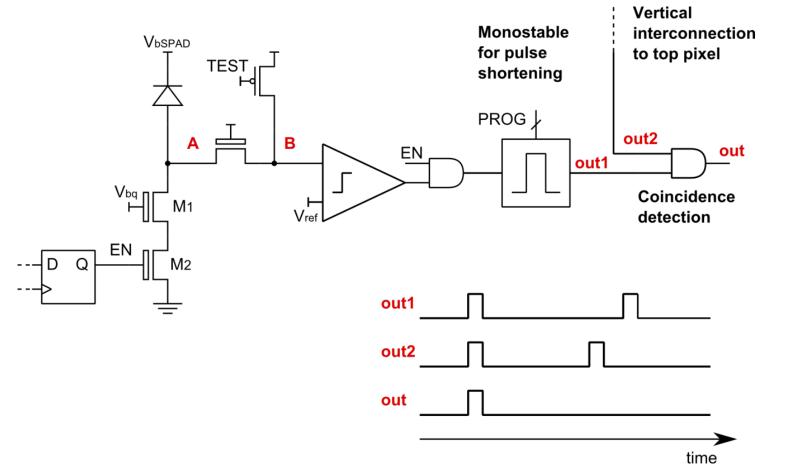

# **Pixel architecture: monostable**

- Pulse shortening: reduces the rate of accidental coincidence

- Programmable pulse width: 750ps, 1.5ns, 10ns

NFN

Istituto Nazionale

di Fisica Nucleare

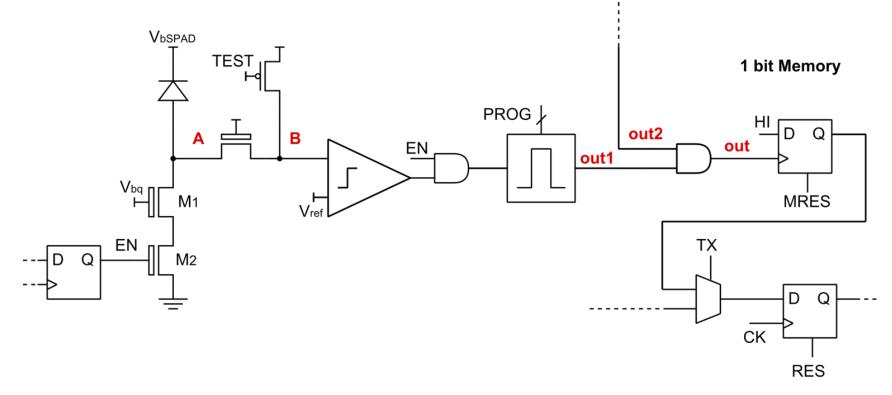

### **Pixel architecture: storage**

**Output Register**

- **Global shutter** operation:

- Fast transfer from memory to output register

- Simultaneous accumulation and data output

### **2-level pixel schematic**

**Top pixel**: subset of bottom pixel

**CERN, January 20, 2017**

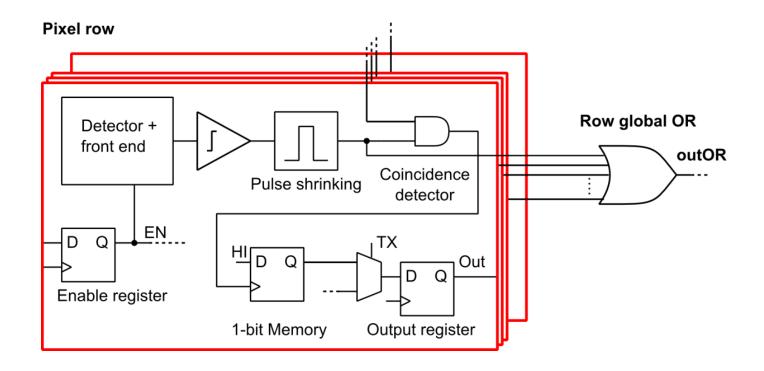

### Sensor architecture: row-wise OR

**Test output** outOR: combination of all the active (enabled) pixels in the row

**CERN, January 20, 2017**

- 38

Istituto Nazionale di Fisica Nucleare

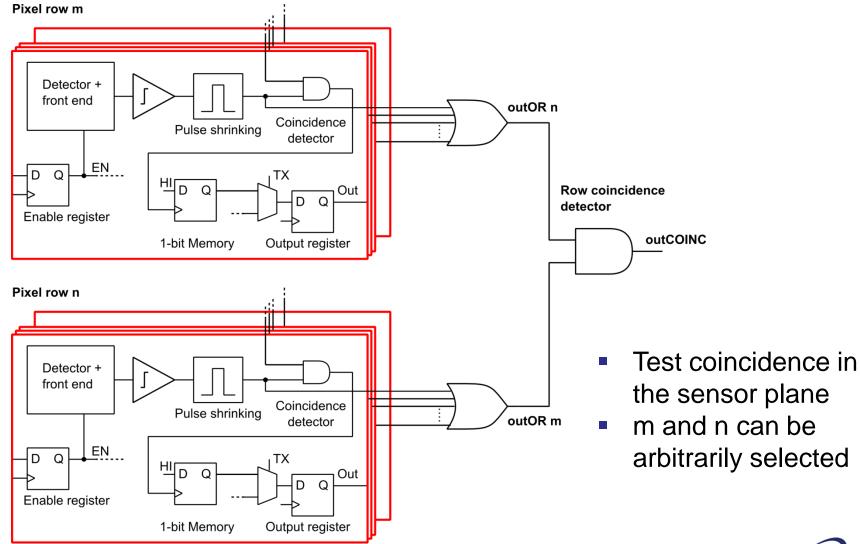

#### **Row-wise coincidence circuit**

39

Istituto Nazionale di Fisica Nucleare

#### Sensor floorplan

Final assembly

40

**CERN, January 20, 2017**

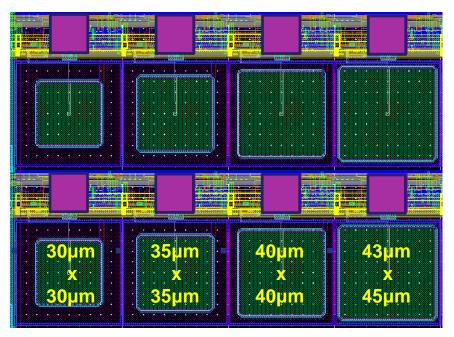

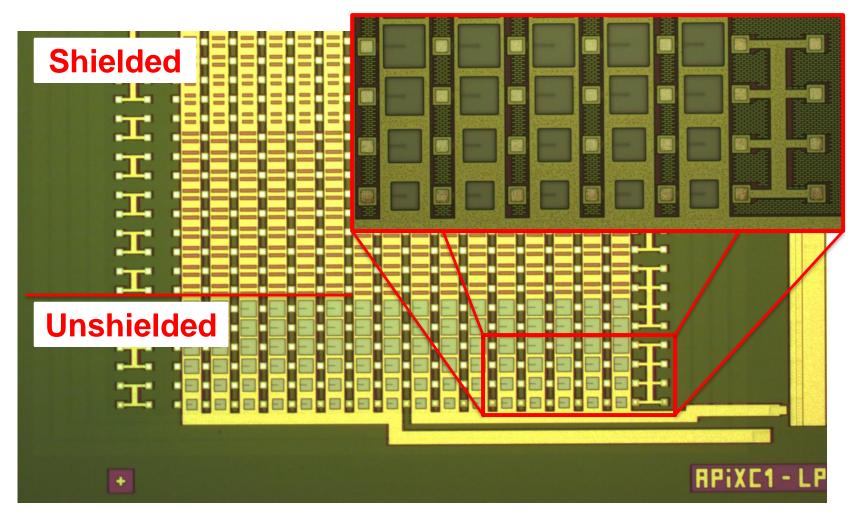

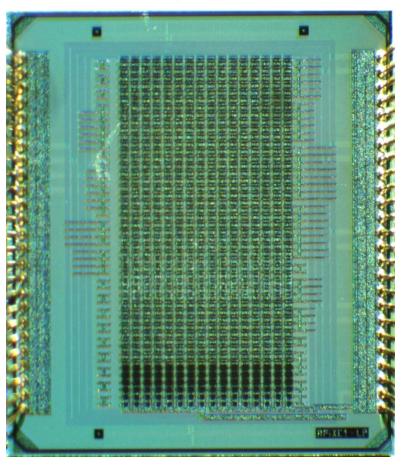

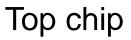

#### **Pixel array**

- 16 x 48 pixel array

- Pixel size: 50µm x 75µm

- Splittings in detector type and area

# Pixels with different detector area (unshielded)

Pixels with shielded detectors

### **Bottom chip - Micrographs**

## Sensor micrographs

#### Bottom chip

#### **Experimental results - summary**

Characterization of **single-layer sensors**:

- Core supply current (at 1.8V): 8mA

- Breakdown voltage uniformity

- Dark count rate

- In-plane coincidence

- Timing resolution

- Cross-talk

#### Vertically integrated sensors with bump bonding (IZM):

- Coincidence dark counts

- Test with beta source

- Test beam

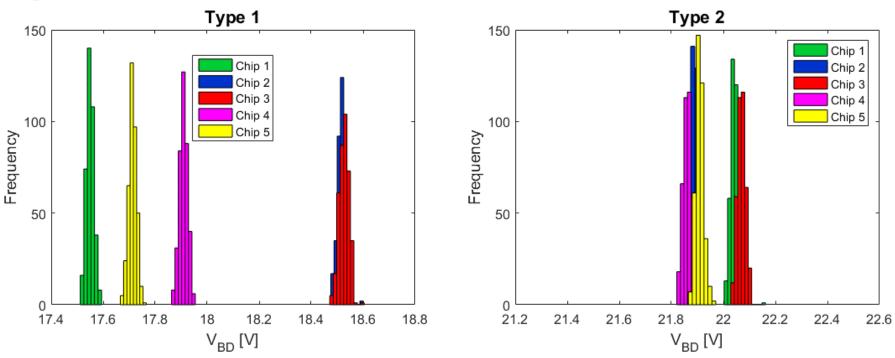

# **Breakdown voltage uniformity**

- Measurements on

5 sample chips x 2 types x 196 devices per chip

- Very good uniformity on-chip ( $\sigma < 20mV$ )

- Large difference (1V) between different chips for type 1

di Fisica Nucleare

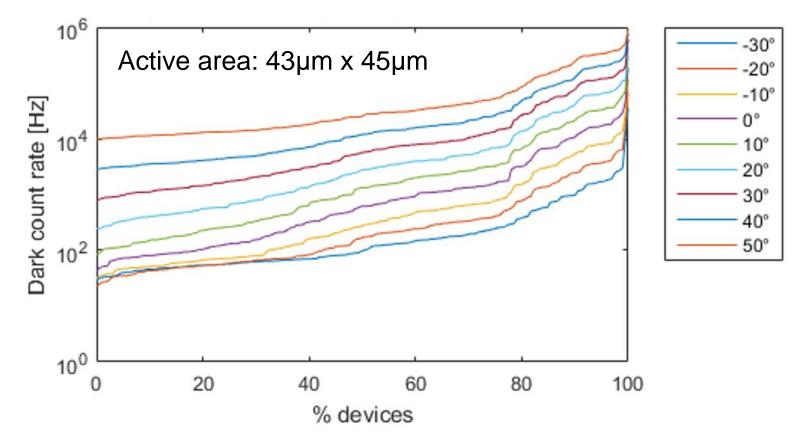

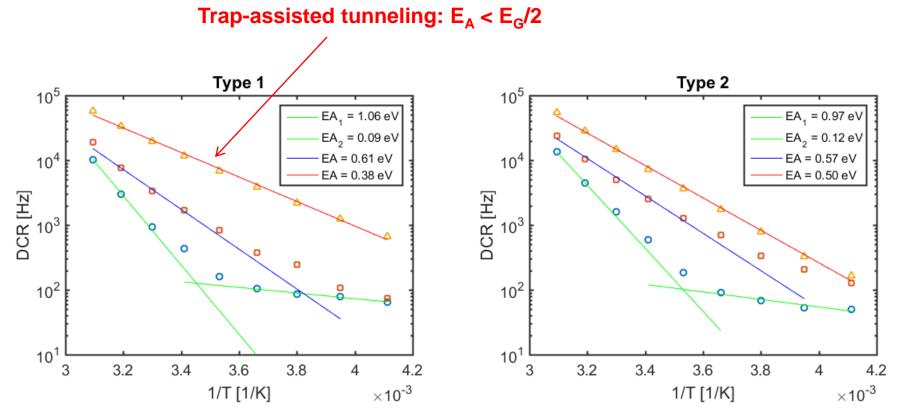

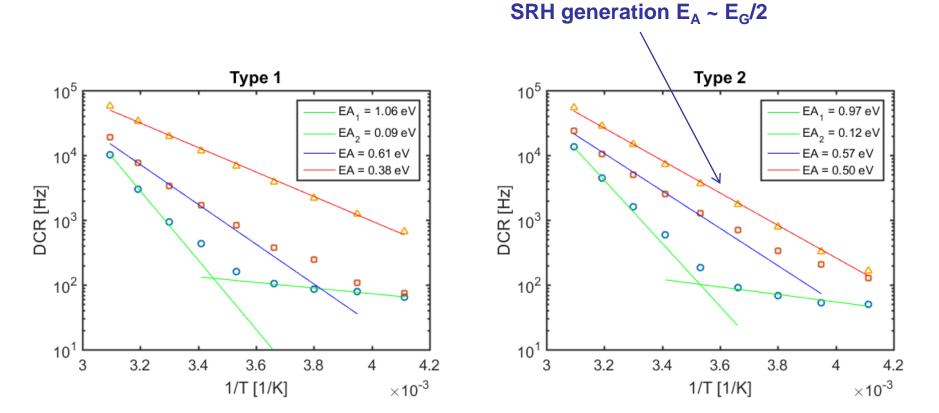

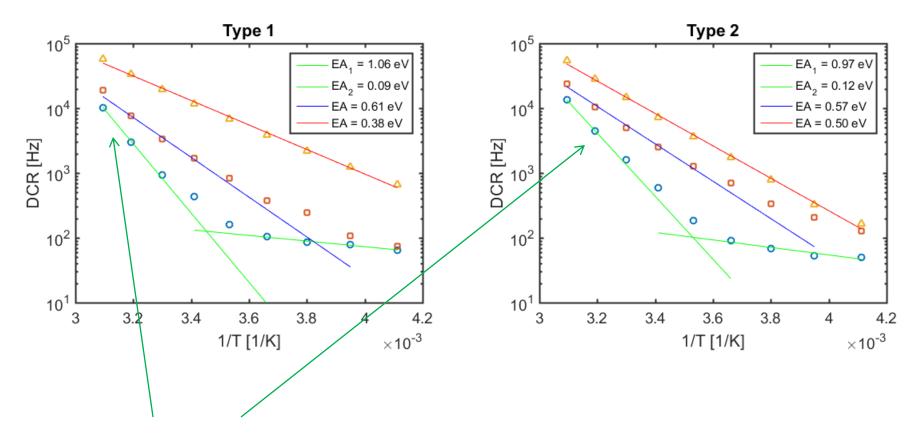

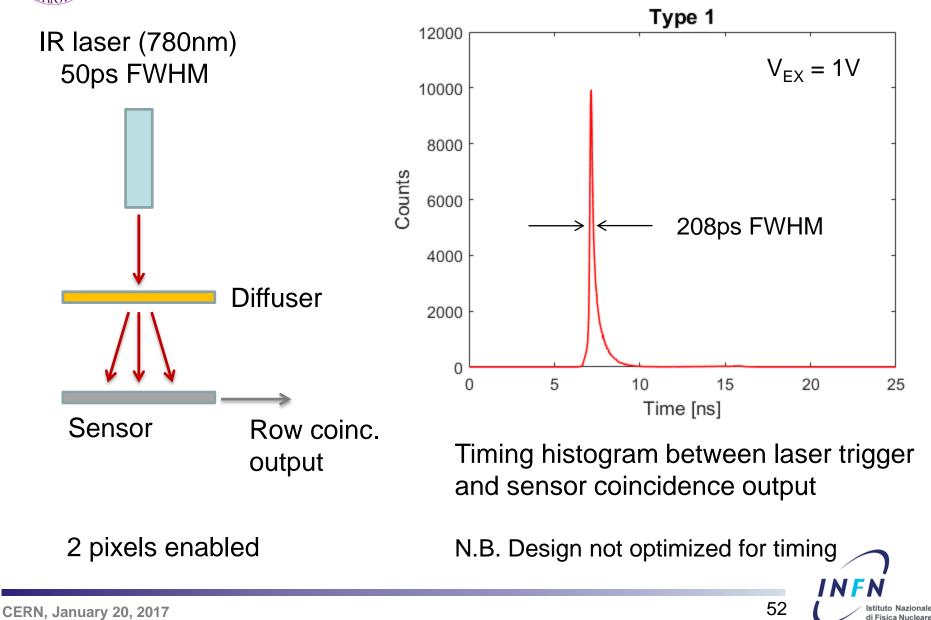

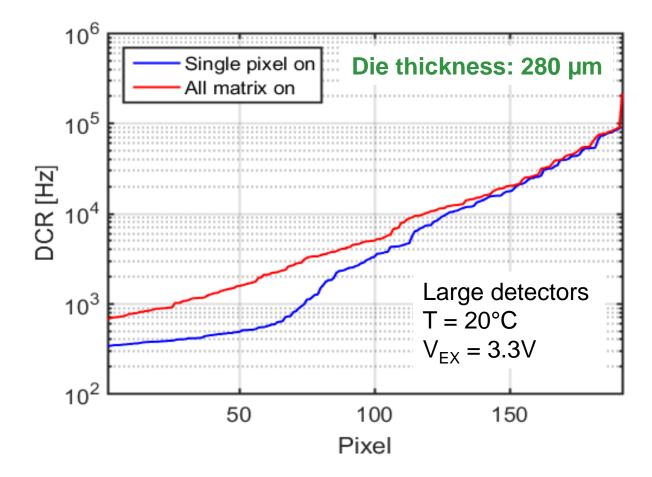

#### **DCR distribution**

- DCR distribution spans 2 orders of magnitude at RT

- Median value at 20°C: 2.8kHz MHz/mm<sup>2</sup>

- Devices with 43µm x 45µm active area, but different DCR

- Measurements from -30°C to 50°C with 10°C steps

- Overvoltage:  $V_{OV} = 3.3V$

INFN Istituto Nazionale di Fisica Nucleare

Injection from neutral regions:  $E_A \sim E_G$

di Fisica Nucleare

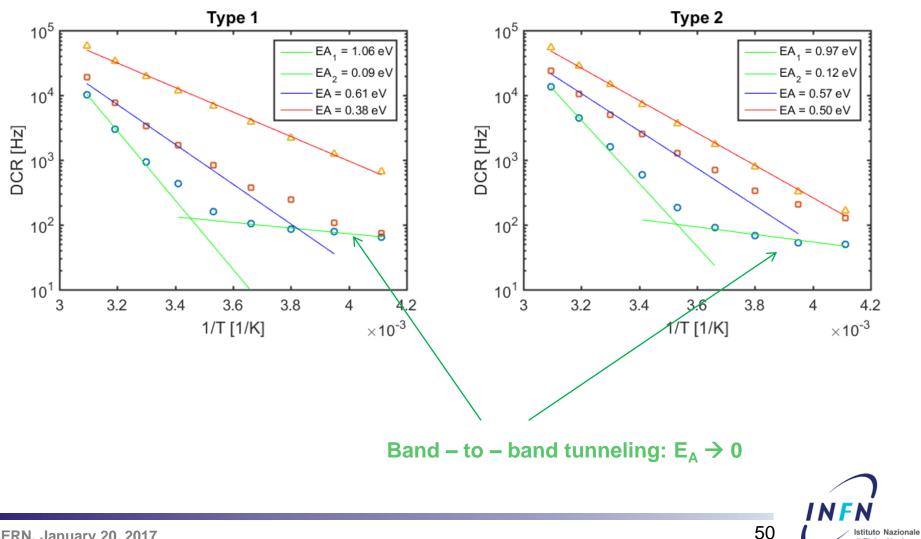

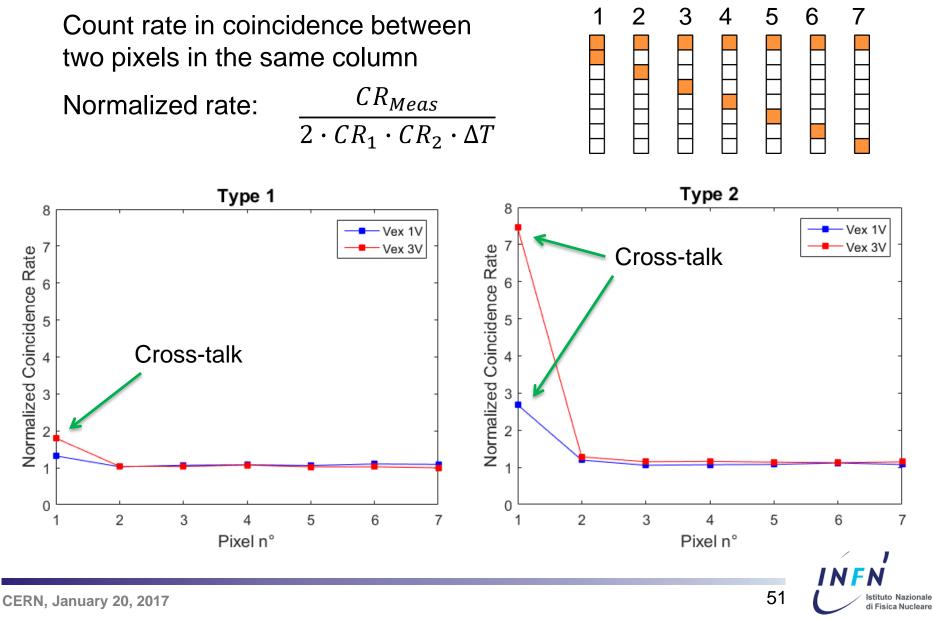

#### **Coincidence detection**

### **Timing resolution**

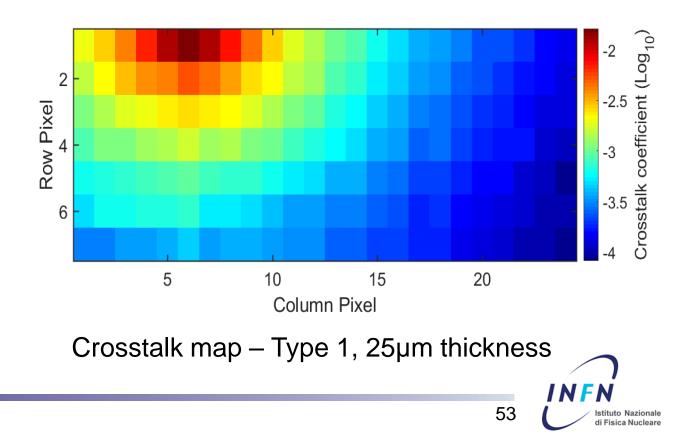

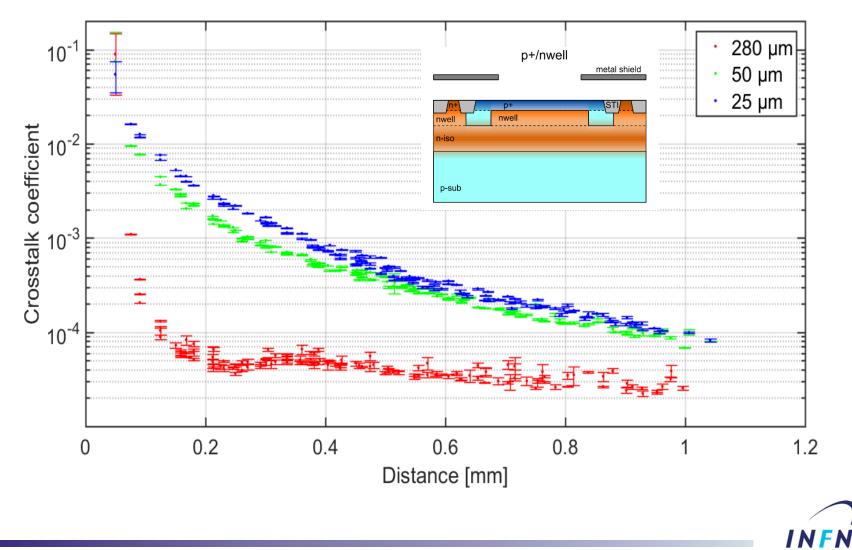

### **Crosstalk characterization**

• Crosstalk coefficient  $CRm = DCRe \cdot DCRd \cdot 2\Delta T + K \cdot (DCRe + DCRd)$

Emitter (fixed)

Detector

(scan)

#### **Crosstalk vs substrate thickness**

Istituto Nazionale di Fisica Nucleare

### **Dark Count Rate and cross-talk**

# **Median DCR** increase of 70% due to cross-talk: from 2.8kHz to 4.8kHz

A. Ficorella, et a., Proc. IEEE ESSDERC, 2016

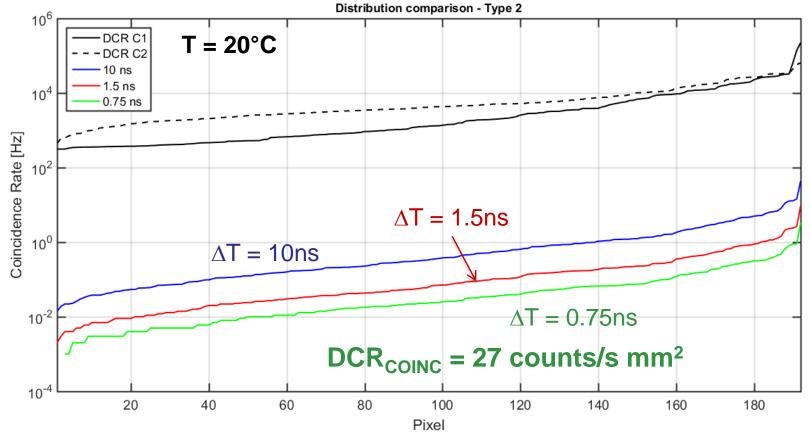

# **Vertically-integrated assembly**

Dark Count Rate vs. coincidence time  $\Delta T$

$DCR_{COINC} = DCR_1 \times DCR_2 \times 2\Delta T$

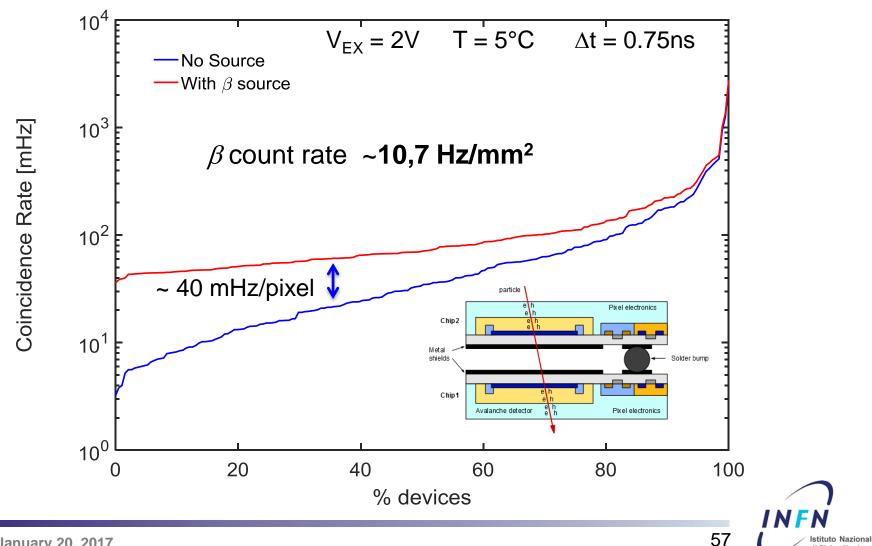

#### **β-source measurements**

<sup>90</sup>Sr  $\beta$  source – 37kBq at 2mm distance from sensor

di Fisica Nucleare

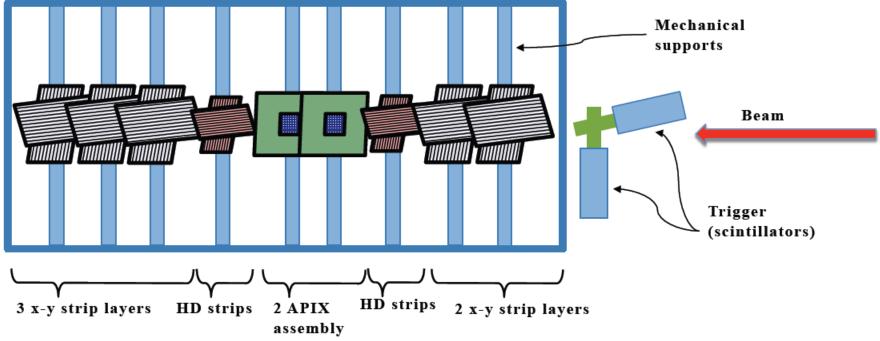

#### **Test beam at CERN**

Metal box shielding

- Test at CERN SPS north area facility (H4 beam line)

- Two APIX under test + auxiliary Beam Tracker detector

- Positrons and  $\pi^+$  beams at 50, 100, 150, 200 and 300 GeV

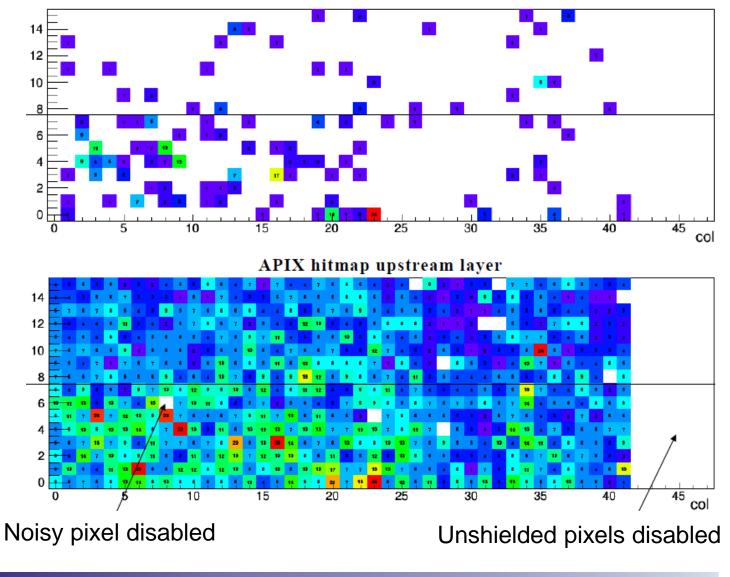

### Test beam – hit maps

APIX random trigger upstream layer

INFN Istituto Nazionale di Fisica Nucleare

# **APiX - Summary**

#### Strengths:

- Can be thinned to a **few microns**: low material budget

- Timing resolution

- Low power consumption

- Early signal digitization

#### Weaknesses:

- Radiation tolerance (still to be assessed)

- Efficiency: guard ring and in-pixel electronics

- Cost and availability of 3D integration technologies

- Current prototype:

- Test beam data analysis (in progress)

- Radiation hardness studies

- Design of new prototype:

- Improved fill factor

- Larger array

- Optimized timing

- Optimized power consumption

#### Summary

- Higly parallel SPAD systems require high-density digital circuit for high efficiency

- SPAD technology in **deep sub-micron** processes is evolving driven by consumer applications: investments

- Maximum efficiency: **3D integration.** Optical cross-talk is still an issue in systems with very high FF

- Concept of charged-particles direct detection with Geiger-mode detectors in coincidence is feasible

- Efficiency is still an issue, but **timing** can be very good

- Development in deep-submicron SPADs and 3D integration can the key for a full exploitation of this concept

#### Acknowledgements

#### **APiX2 project**

"Development of an Avalanche Pixel Sensor for tracking applications"

Funded by INFN – CSN5

Project coordinator: Pier Simone Marrocchesi, INFN Pisa and University of Siena

Partners:

- TIFPA and University of Trento,

- INFN Pavia and University Pavia,

- INFN Padova and University of Padova,

- Laboratoire APC, Université Paris-Diderot/CNRS