## Adaptercard Ideas RD53A Testing Meeting - 27.01.17

Timon Heim - LBNL

UNIVERSITY O CALIFORNIA

1

## What comes from SCC?

- Hope this matches Marco's talk before me

- Only looking at digital connection, power/analog should come from somewhere else

- SCC will have

- 1 DP connector for 4x1.28Gbps

- 1 DP connector for 1x5Gbps

- 1 RJ45 connector for HitOr

- Local monitoring for serial powering scenario? I2C?

- FMC most commonly used standard with FPGA boards

- FMC-LPC = Low Pin Count version

- 34 LVDS pairs (can also be used single-ended)

- 1 MGT, 1 I2C, 2 Clks, 12V/3.3V/Vadj (low power)

- FMC-HPC = High Pin Count version

- 80 LVDS pairs (can also be used single-ended)

- 10 MGT, 1 I2C, 4 Clks, 12V/3.3V/Vadj (low power)

- LPC and HPC are compatible, but of course only enable their respective connections

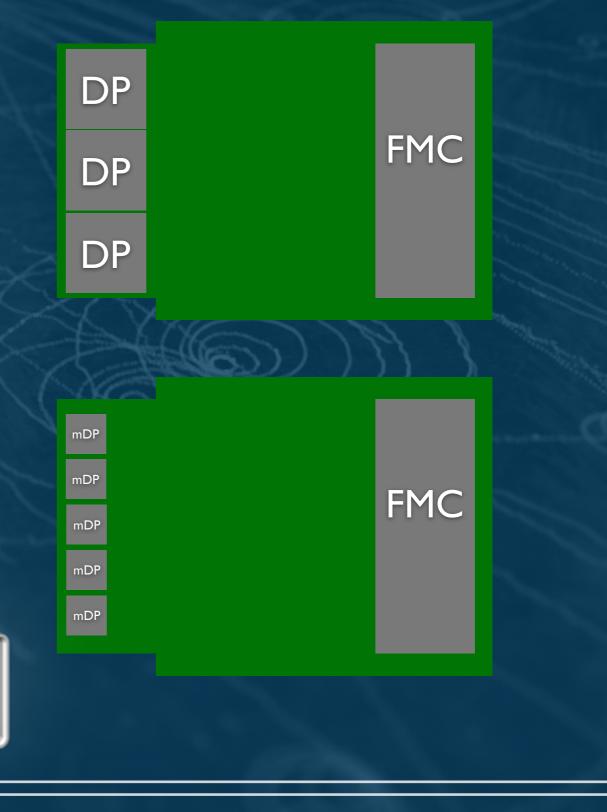

## Adapter card:

- FMC standard gives ~65mm faceplate space

- Fits 3xDP connector or 5-6x Mini DP

- Two connection options:

- 1 x 5Gbps

- 4 x 1.28Gbps

- Not possible on the same connector!

- Most likely one transmission will dominate during common usage.

## DP vs mDP:

- DP has better locking mechanism

- mDP gives better utilisation of faceplate space

- Adapters from mDP to DP available

- Found a "vertical" mDP, which would allow even more connections

- Initially don't need very high number of chips to be connected

- One 5Gbps DP + one 4x1.28Gbps DP enables testing of each interface and should be simple to design

- If 5Gbps transmission is better, adapter card design will get more complex when scaling up to more chips

- 4x1.28 Gbps transmission should still be possible even with a LPC FMC enabling higher compatibility, but might set more requirements in terms of timing in the FPGA

- RJ45 for HitOr is convenient but connected takes up a lot of space

- Can use chip internal coincidence function and only use a single LVDS pair

- Having an I2C connection to the SCC might come in handy for monitoring, e.g. SCC could have ADC mounted to measure voltage, current or temp.

- DP connector has 5 spare signals we can use, but need to make sure that signal can be AC coupled (serial powering!)

- An extra I2C (or similar com bus) for external devices might come in handy in the future, need lightweight con/cable