# FELIX: the New Detector Readout System for the ATLAS Experiment

Frans Schreuder

Nikhef, The Netherlands

f.schreuder@nikhef.nl

On behalf of the ATLAS TDAQ Collaboration

#### **Outline**

- ATLAS DAQ Today, Phase I upgrade and HL-LHC

- FELIX Hardware

- FELIX Firmware: 2 modes of operation

- System integration and testing

- Integration with different ATLAS and non-ATLAS subdetectors

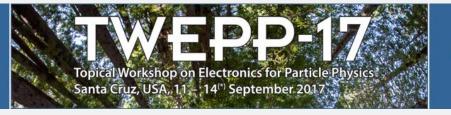

## ATLAS DAQ Today

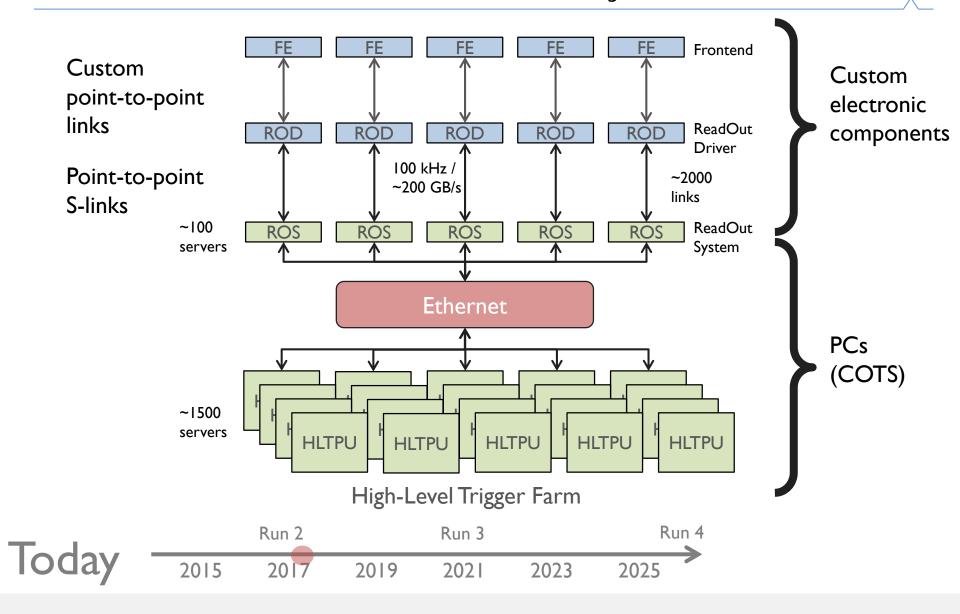

## Upgrade for Phase-I

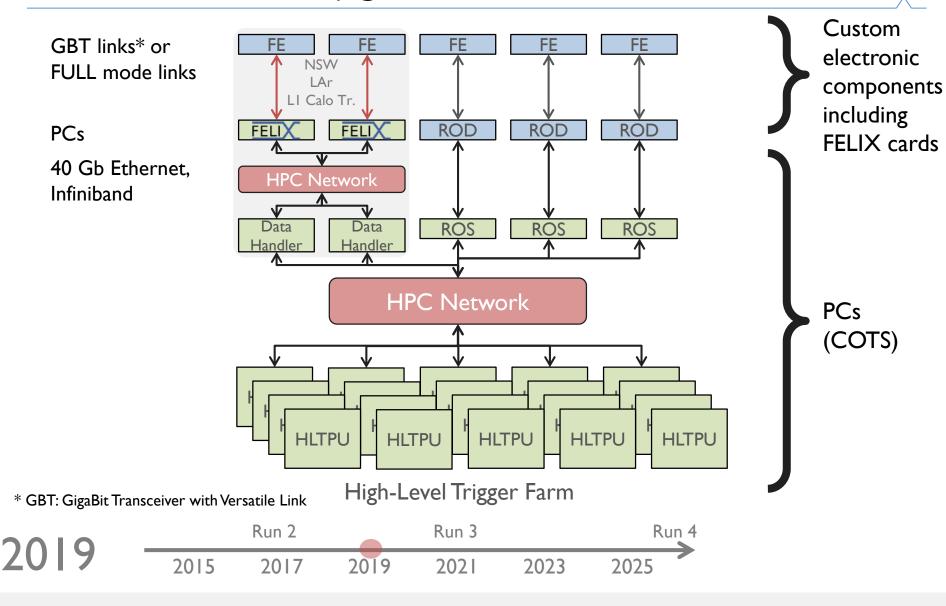

## Upgrade for HL-LHC

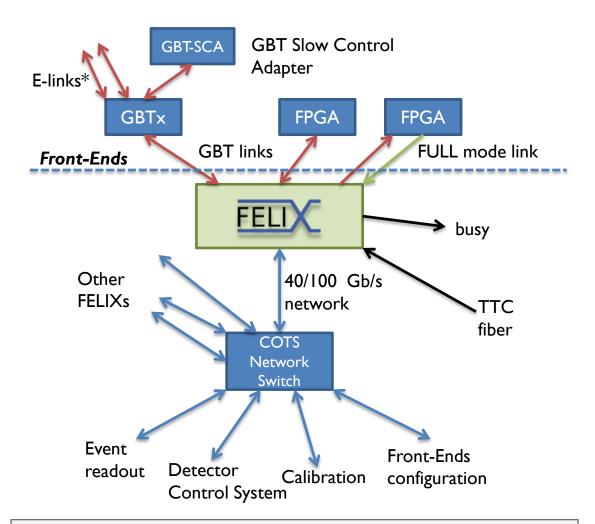

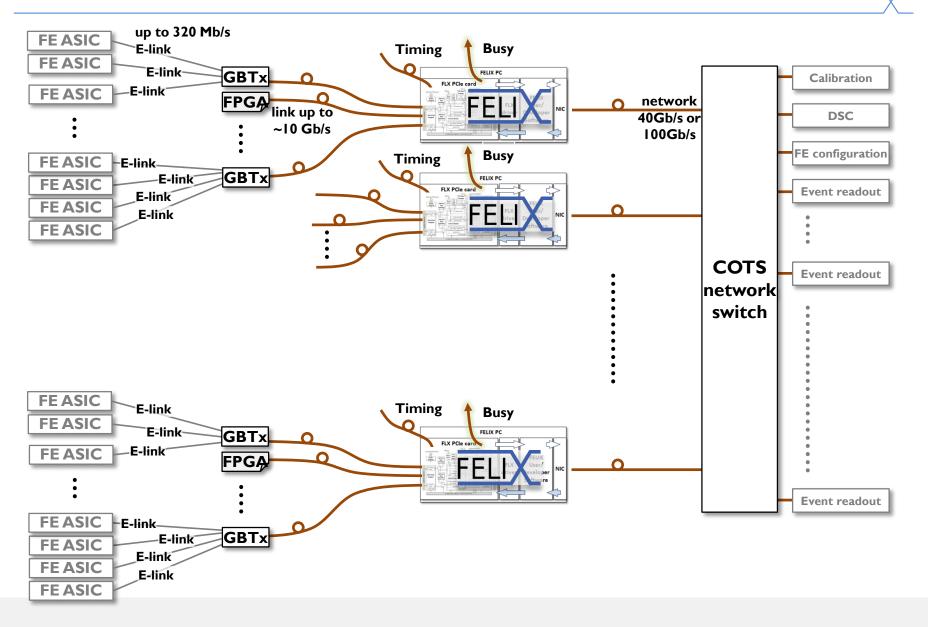

## FELIX functionality

\* E-link: variable-width logical link on top of the GBT protocol. Can be used to logically separate different streams on a single physical link.

- Scalable architecture

- Routing of event data, detector control, configuration, calibration, monitoring

- Connect the ATLAS

detector Front-Ends to the

DAQ system, for both the

to and from FE directions

- Configurable E-links in GBT Mode

- Detector independent

- TTC (Timing, Trigger and Control) distribution integrated

## FELIX server PC components

#### VC-709 from Xilinx

- Virtex7 X690T FPGA

- FLX-709 or miniFelix

- 4 optical links (SFP+)

- Intended for FE development support

- PCle Gen3 x8

#### TTCfx (v3) mezzanine card

- TTC input

- ADN2814 for TTC clock-data recovery

- Si5345 jitter cleaner

# oment support

## SuperMicro X10SRA-F used for development

- Broadwell CPU, e.g. E5-1650V4, 3.6GHz

- PCle Gen3 slots

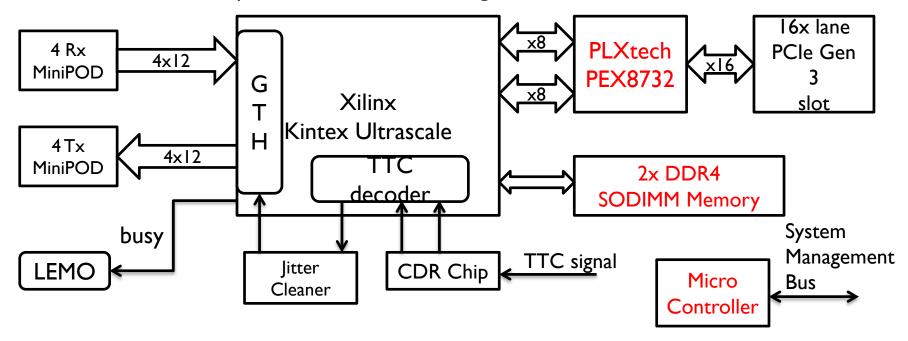

#### o BNL-711 from BNL

- Xilinx Kintex Ultrascale XCKU115

- 48 optical links (MiniPODs)

- FELIX Phase-I prototype

- TTC input ADN2814

- SI5345 jitter cleaner

- PCle Gen3 x16 (2x8 with bridge)

- Version 2.0 currently tested

#### Mellanox ConnectX-3

- 2x FDR/QDR Infiniband

- 2x 10/40 GbE

## FELIX: modes of operation

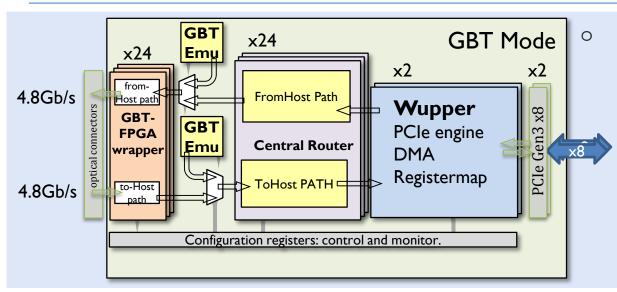

#### **GBT** mode

- Line rate: 4.8 Gb/s

- Up to 24 bidirectional optical links

- 3.2 Gb/s payload with FEC or

4.48 Gb/s payload

- Routes TTC information

- Optical link divided in E-Links

- Communicate with GBTx & GBT-SCA

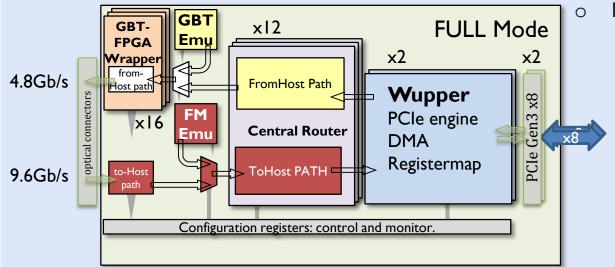

#### **FULL** mode

- Line rate: 9.6 Gb/s

- Up to 12 bidirectional optical links

- Routes TTC information

- 7.68 Gb/s payload:8B/10B encoding

- CRC

- BUSY-ON and OFF

- 4.8 Gb/s GBT links to FE

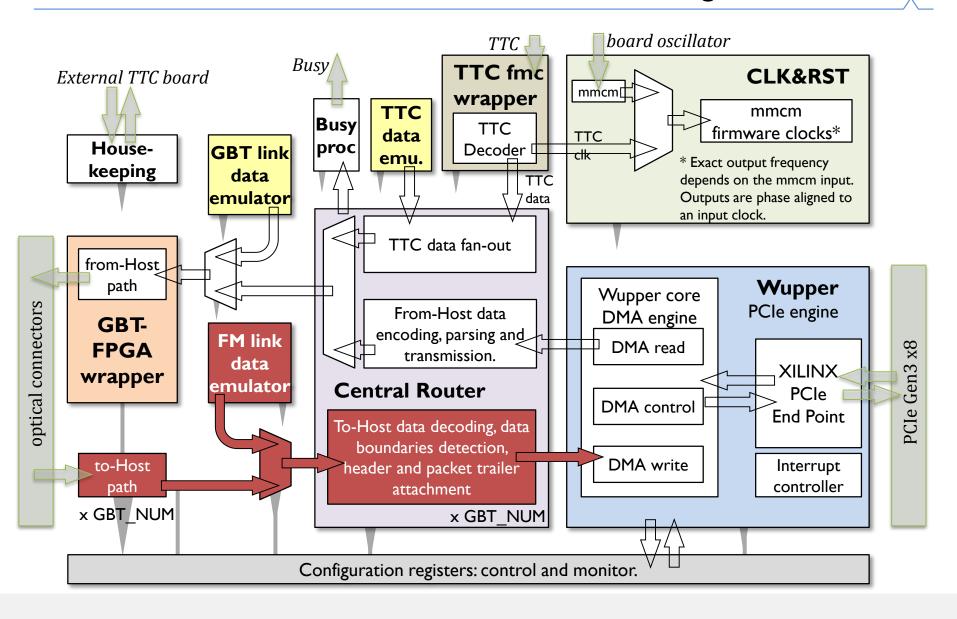

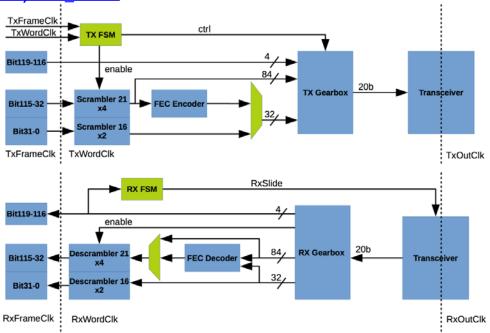

## FELIX GBT firmware block diagram

9

## FELIX FULL mode firmware block diagram

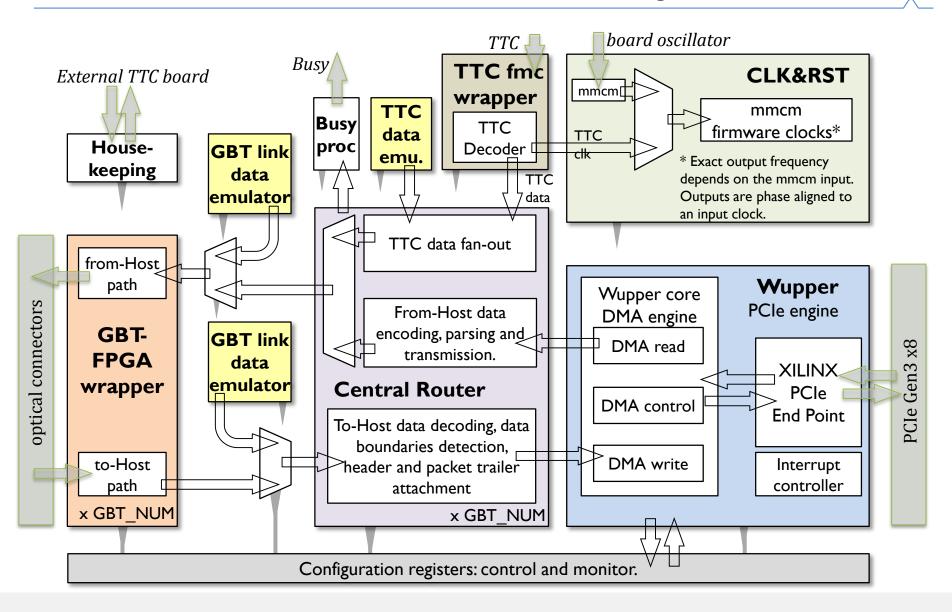

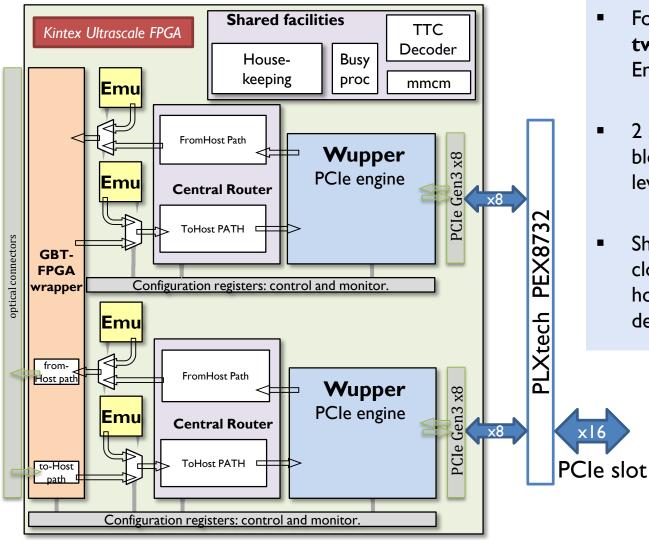

## FELIX firmware on PCIe x16

- For BNL-711: the PC will see

two independent Gen3 x8 lanes

EndPoints, as Xilinx PCIe devices.

- 2 sets of an identical firmware block are instantiated in the top level design.

- Shared facilities in grey (include clock resources, the housekeeping module,TTC decoder and busy logic).

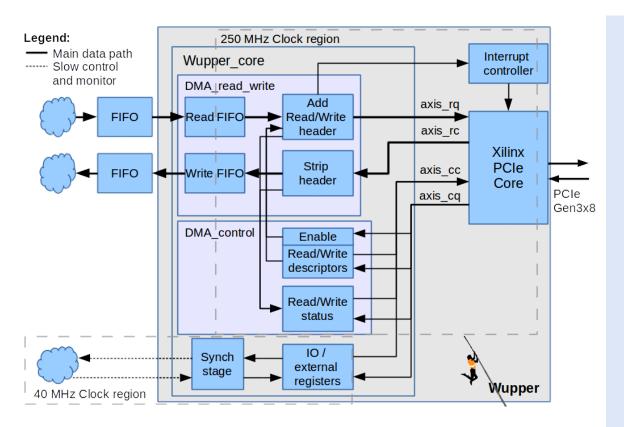

## Wupper: PCIe engine for FELIX

- Developed for use in FELIX

- Published as Open Source (LGPL) on OpenCores http://opencores.org/project,virtex7 pcie dma

- Core matured to maintenance only phase

- Positive feedback from the community

- PCle Engine with DMA interface to the Xilinx Virtex-7 (Kintex Ultrascale) PCle Gen3 Integrated Block for PCl Express

- Xilinx AXI (ARM AMBA)

Stream Interface (UG761)

- MSI-X compatible interrupt controller

- Applications access the engine via simple FIFOs

- Register map for programmed I/O synchronized to a lower clock speed

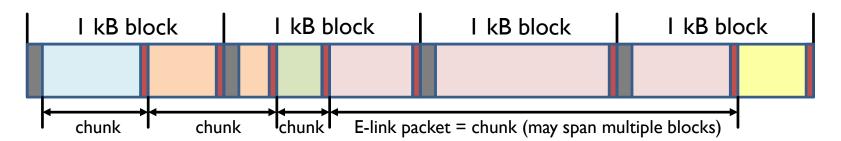

#### Data format

- Data buffered in the FPGA per E-link or per FULL mode link and transferred under DMA control

- Fixed block size of I kB

- The blocks are transferred into a contiguous area, functioning as a circular buffer, in the main memory of the PC.

- The DMA runs continuously, thereby eliminating DMA setup overheads and achieving high throughput (about 12 GB/s for the 16-lane interface of the FLX-711).

- Event fragments or other types of data arriving via the FE links are referred to as "chunks" and can have an arbitrary size.

- I kB blocks of E-links or FULL mode links are multiplexed into a single stream.

- Block header: (32 bits)

- E-link ID

- Block sequence

- Start of block symbol

- Fragment trailer (16 bits)

- Fragment type

- First, last, both, middle, null

- Flags

- Error, truncation, timeout, CRC error

- Fragment length

- 10 bits

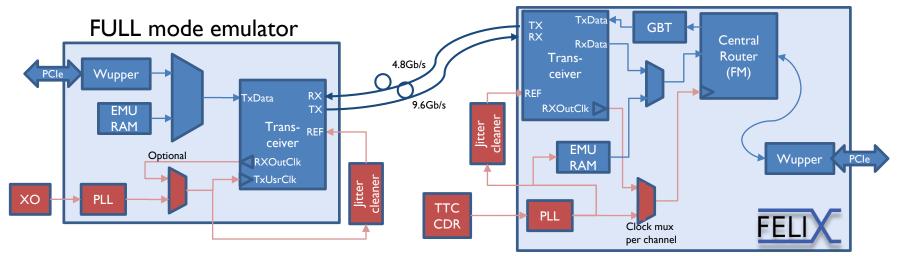

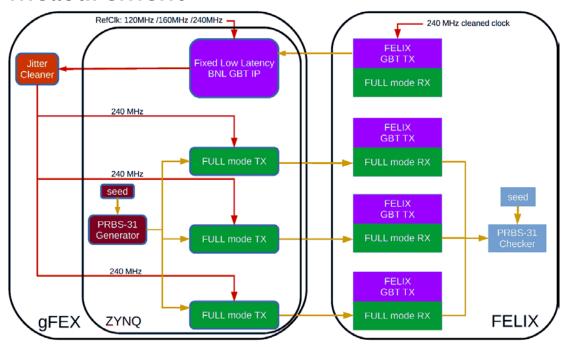

## FULL mode chain and clocking

FELIX FULL mode

14

- 9.6Gb/s Link tested with 32-bit PRBS3 I generator and checker.

- No error occurred for ~72 hours run. **BER < IE-I5**.

- Complete design tested with different FPGA based emulated data generators (gFEX,VC709,VC707)

- No errors occurred for several TB of data transmitted

- Optional RX clock recovery for TX in emulator

- Clock recovery in FELIX, or local clock for internal emulator

### FELIX data flow overview

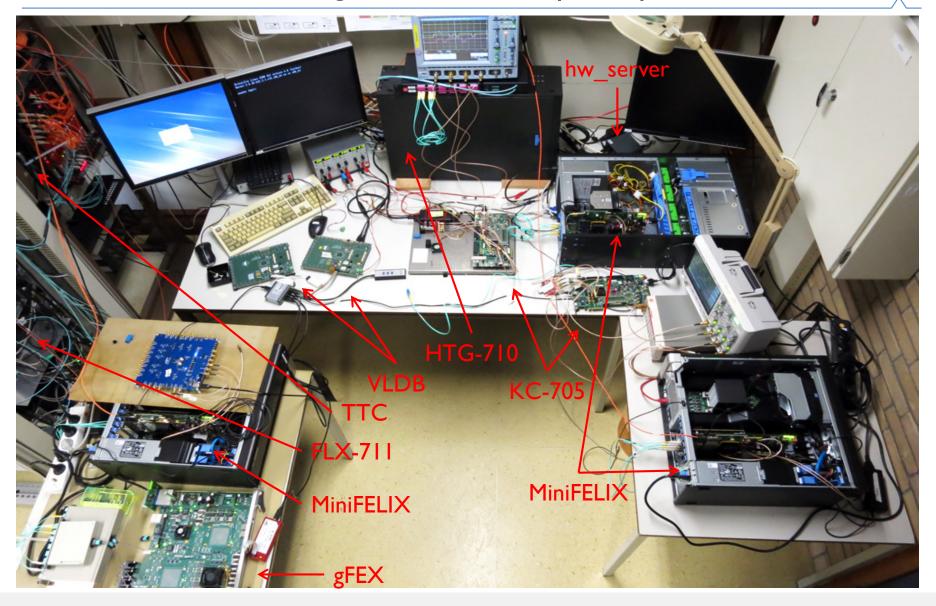

## Integration workshop setup

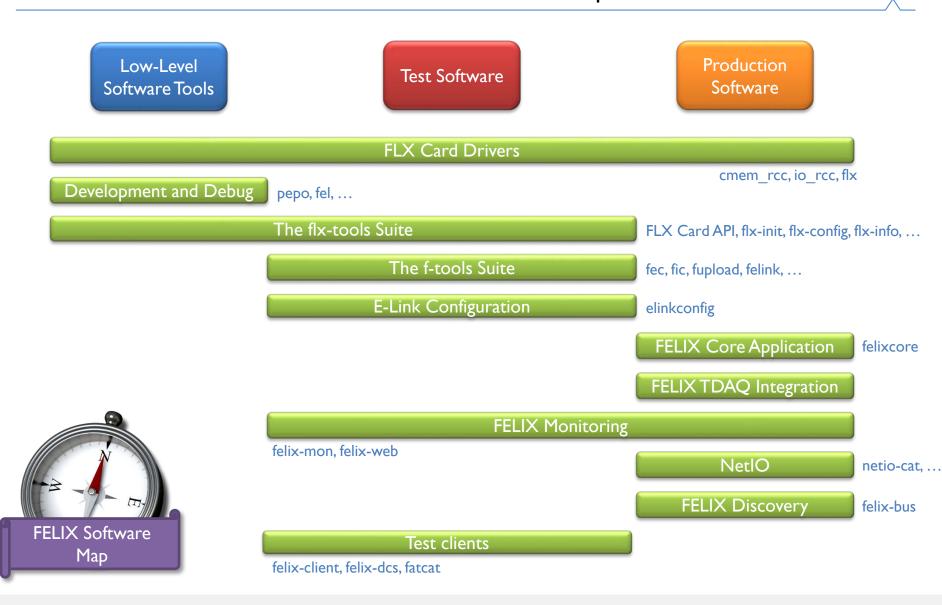

## FELIX software: status update

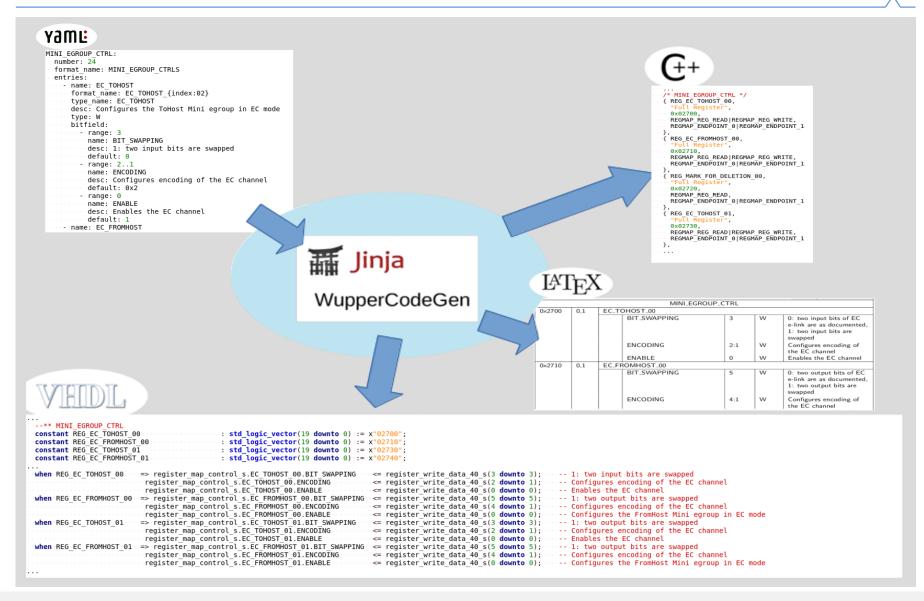

## Register map automation - Jinja 2

## Integration test with front-ends

#### ATLAS sub-detector test setups, currently implementing FELIX

- Liquid Argon Calorimeter

- LTDB (LAr Trigger Digitizer Board): integration testing ongoing with 40+ channels to monitor the FE and operate the TTC distribution

- LDPB (LAr Digital Processing Blade): integration testing ongoing with MiniFELIX in FULL mode

- Level-1 calorimeter trigger

- gFEX (Global Feature Extractor): connection established for 12 FULL mode links, long term stability ongoing

- ROD, Hub for eFEX (Electron Feature Extractor) and jFEX (Jet Feature Extractor): users in the process of setting up their test facilities

- TREX (Tile Rear Extension) modules: users in the process of setting up their test facilities

- Muon spectrometer

- New Small Wheels (NSW): sTGC (Small-strip Thin Gap Chamber) and MicroMegas (Micro Mesh Gaseous Structure) detector for muon tracking: integration of the FELIX system in the NSW Vertical Slice including the complete DCS (Detector Control System) chain, now targeting performance and long term stability

- BIS78 (Barrel Inner Small MDT (sector 7/8) ): users in the process of setting up their test facilities with FELIX

- Tile Calorimeter

- Test system for Phase-II readout

- Initial communication established with the Tile PPr board in GBT mode

- Stepping toward FULL mode communication

- Pixel sensors readout (for the Control and Readout ITk Inner Tracker)

- Test system for Phase-II ITk HV-CMOS pixel sensor R&D and Pixel demonstrator readout

- A FELIX system has been used to readout a telescope during recent HV-CMOS beam tests at CERN

- A vertical slice test stand for Pixel demonstrator readout with FELIX has been set up at CERN

19

## Integration test with front-ends

#### Non-ATLAS detectors connected to FELIX

- Several experiments outside the ATLAS collaboration expressed interest in the FELIX system to control and readout their detectors

- A number of them is actively evaluating FELIX as a possible readout solution

- The current most noticeable group is the ProtoDUNE collaboration (vertical slice):

- **FELIX Emulator**: software development ongoing using the FULL mode complete chain kit provided by the FELIX team (FULL Mode Generator + FULL Mode FELIX)

- WIB (Warm Interface Board): is being correctly readout by a FELIX system and long term stability testing is now being target

### Summary

- FELIX is a router between custom serial links and a commodity network, which separates data transport from data processing.

- In LHC Run-3 (2021-2023) FELIX will be used by some detectors and trigger systems to interface the data acquisition, detector TTC systems.

- In LHC Run-4 this is planned for all ATLAS detectors.

- Status:

- FELIX GBT Mode: the firmware and the software reached a development status sufficient to be distributed to ATLAS Sub-Detectors Front End developers.

- FELIX FULL Mode reached a development status sufficient to be distributed to the Front End developers.

- Supported hardware platforms for both modes: FLX-709 (Xilinx VC-709) and FLX-711 (BNL 16 lane card)

#### Ongoing efforts

- Increase overall system reliability.

- Increase the number of input channels supported to 24 for GBT mode

- Extend the system testing and integration: firmware to control of GBTx ASIC via its IC port, GBT-SCA ASIC via EC port.

- A C++ API and an OPC server and client are in progress to fully support the GBT-SCA ASIC.

- Procurement in 2018, installation in 2019

## Features of BNL-711

FELIX base line hardware platform: PCle FPGA board gen3 x16, "BNL-711"

- Developed at BNL also as the DAQ platform for the LTDB (Liquid Argon Trigger Digitizer Board)

production test platform

- PLXtech PEX8732 to handle PCle Gen3 x16 lanes (max 128 Gbps) interface to host

- 48-ch MiniPOD TX & RX, up to 14Gb/s per link

- 2x SODIMM DDR4 interfaces (not used in FELIX, removed in v2.0)

- Integrated TTC interface, busy output, and on-board jitter cleaner

- Micro-Controller (Atmega 324A) for FPGA firmware update and version control

## Transceiver wrapper for FELIX

- □ Supports 4.8 Gb/s **GBT mode**, and 9.6 Gb/s **FULL mode** defined for FELIX.

- ☐ FELIX **GBT Wrapper** is based on CERN GBT-FPGA, with some improvements:

- Separated GBT firmware from transceiver block.

- Run-time choice of GBT mode : Normal (FEC) mode or Wide-Bus mode.

- Lower fixed latency (Tx: 27.8~32 ns; Rx: FEC mode 56.4ns; Rx: Wide mode 43.9 ns).

- The GBT encoding/decoding are in the 240 MHz domain.

- Some blocks like Rx side frame alignment, Tx side time domain crossing are redesigned.

- The single channel example design for KC705/VC709 can be found at https://github.com/simpway/GBT KC705

## Integration test: Clock stability

Goal: asses the quality of the clock distributed by FELIX with an indirect measurement

- Use a BERT (Bit Error Rate Tester) at 9.6 Gbps (bit time 100 ps) as an indirect measurement of the clock stability (overall clock has to cope with that)

- Measurement done with both local and TTC clock

- No errors occurred for ~72 hours run. BER < IE-I5.</li>

## Register map automation - Jinja 2

```

2791

---- ## GENERATED code BEGIN #4 ----

2792

2793

when REG STATUS LEDS

=> register map control s.STATUS LEDS

<= register write data 40 s(7 downto 0); -- Board GPIO Leds

=> register map control_s.CR_TH_UPDATE_CTRL

2794

when REG CR TH UPDATE CTRL

<= "1":

-- See Central Router Doc

2795

when REG CR FH UPDATE CTRL

=> register map control s.CR FH UPDATE CTRL

--- See Central Router Doc

2796

when REG FH IC PACKET RDY

=> register map control s.FH IC PACKET RDY

<= register write data 40 s(23 downto 0); --- Rising edge indicates the complete packet can be

2797

when REG TIMEOUT CTRL => register map control s.TIMEOUT CTRL.ENABLE

<= register write data 40 s(32 downto 32); --- 1 enables the timout trailer generation for</pre>

ToHost mode

2798

register map control s.TIMEOUT CTRL.TIMEOUT

<= register write data 40 s(31 downto 0); --- Number

```

```

--- ## GENERATED code BEGIN #4

1154

{% for register in registers if register is in group('Bar2') %}

1156

{% for bf in register.bitfield if bf.is_write or bf.

is_trigger %}

1157

{% if loop.first %}

1158

when {{"%-34s"|format(register.prefix_name|

prepend('REG '))}} => register map control s.{{

%-30s"|format(bf.dot_name)}} <= {{\underset{\underset} \underset \undered \underset \underset \underset \underset \underset \underset \u

(bf|vhdl value('register write data 40 s')|semi

)}} {{bf.desc|vhdl_comment(153)}}

1159

{% else %}

{{"%-37s"|format(" ")}}

register_map_control_s.{{"%-30s"|format(bf.

dot name)}} <= {{"%-40s"|format(bf|</pre>

vhdl value('register write data 40 s')|semi

)}} {{bf.desc|vhdl comment(153)}}

{% endif %}

{% endfor %}

1162

1163

{% endfor %}

1164

1165

---- GENERATED code END #4 ## ----

```

## FELIX software: data path

#### FELIX application:

$\rightarrow$  DMA transfers and reads IKByte blocks of data, encoded Read blocks from file for the transfer over PCIe. Every block contains descriptors accumulated data from one E-link or FULL Mode link. → Decode into variable sized packets for transmission over Block decoding network.  $\rightarrow$  Count processed blocks, transfer rates, etc. **Statistics**  $\rightarrow$  Meta-information, for example event ID, is extracted and Extract Meta Information matched against a routing table. Route  $\rightarrow$  Route.  $\rightarrow$  Distribute load among multiple systems, handle automatic Load Balancing, Error Handling failover in case of system failures. → Asynchronous message service 'netio' for data exchange Send to network with network hosts.