BERGISCHE UNIVERSITÄT NUPPERTAL

Prototype chip for a control system in a serial powered pixel detector at the ATLAS Phase II upgrade **TWEPP 2017 Topical Workshop on Electronics for Particle Physics** Santa Cruz, CA

Niklaus Lehmann<sup>1\*</sup>, Rizwan Ahmad<sup>2</sup>, Philip Bergmann<sup>1</sup>, Tobias Fröse<sup>2</sup>, Michael Karagounis<sup>2</sup>, Susanne Kersten<sup>1</sup>, Peter Kind<sup>1</sup>, Yann Narbutt<sup>1</sup>, Jakob Schick<sup>1</sup>, Christian Zeitnitz<sup>1</sup>

<sup>1</sup>University of Wuppertal, <sup>2</sup>FH Dortmund

X ALAS

**Abstract:** A new inner tracking detector (ITk) for the Phase-II upgrade of the ATLAS experiment is in development. A serial power scheme is foreseen for the pixel detector. This requires a new detector control system (DCS) to monitor and control the pixel modules in the serial power chain. The Pixel Serial Power Protection (PSPP) chip is an ASIC for this purpose. It operates parallel to the modules and contains an ADC and bypass transistor. This poster presents test results for the DCS chip and all its prototyped components. It includes irradiation up to 600 Mrad and stability measurements.

Serial Consta Individ • Single

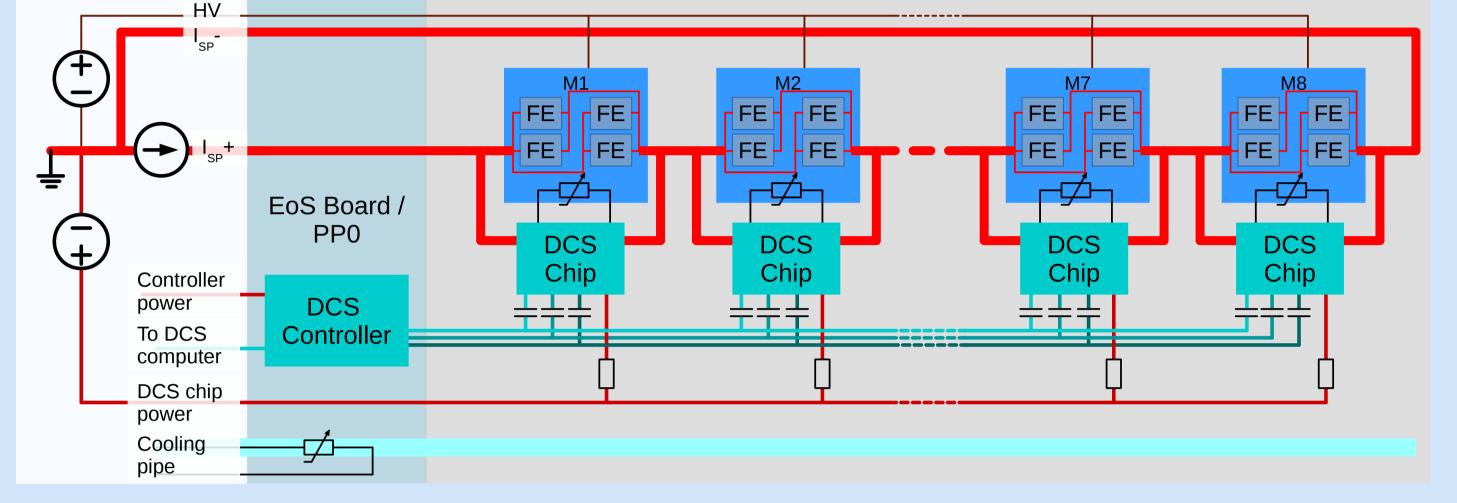

| Serial Power Chain                                                                                                                                                                                                                                                                                    | Detector Control System                                                |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|--|--|--|--|--|

| <ul> <li>power chain to reduce cables<br/>ant current through all modules<br/>ual reference voltage for modules<br/>module failure affects whole chain</li> <li>DCS chip parallel to each module</li> <li>Constant monitoring of module</li> <li>Independent operation of DCS<br/>elements</li> </ul> | Permanently running     Off Detector     Control path     Off Detector |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                       | Independent communication                                              |  |  |  |  |  |

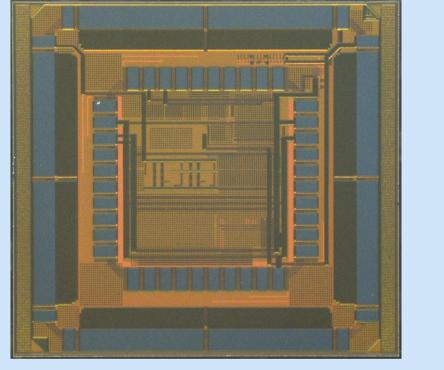

# DCS Chip Prototype: PSPP and PARC

**Pixel Serial Power Protection chip**

#### (PSPP)

PSPPv3

- Radiation hard bypass transistor for 8 A

- Automated bypass activation

- Operation in serial power chain

- Serial Control Bus (SCB): dedicated communication over single ended AC coupled lines

- Logic with triple modular redundancy

PARC

voltage Power Shunt Regulator input outputs external reference voltage .Generic ADC input AC coupling to bus lines Threshold adjust Logic resistors Local GND JJ of chip

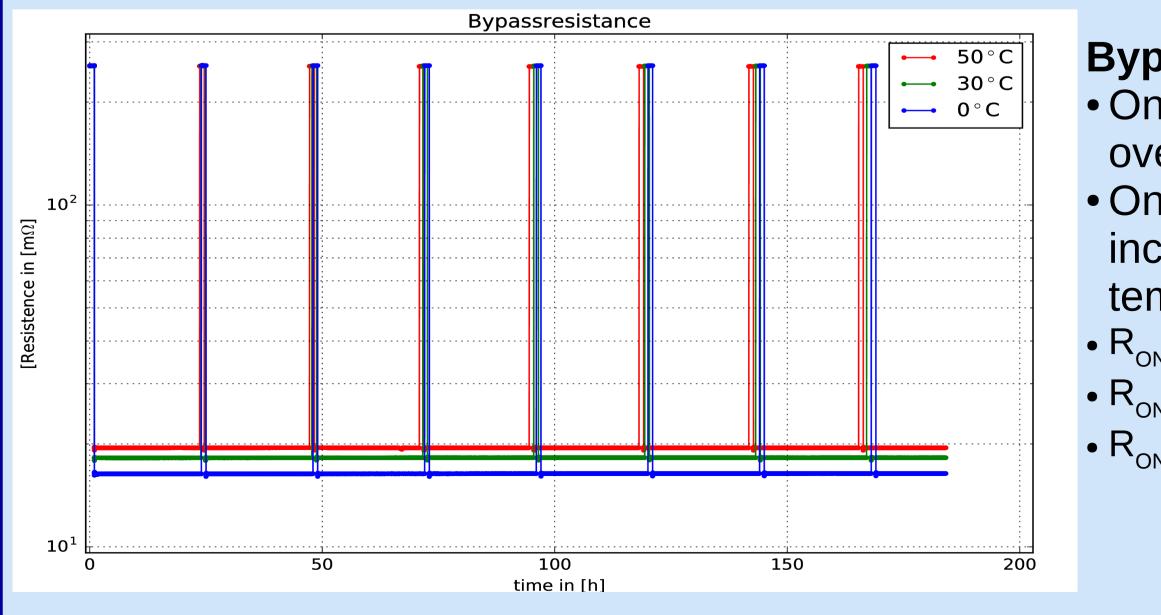

Bypass

Module

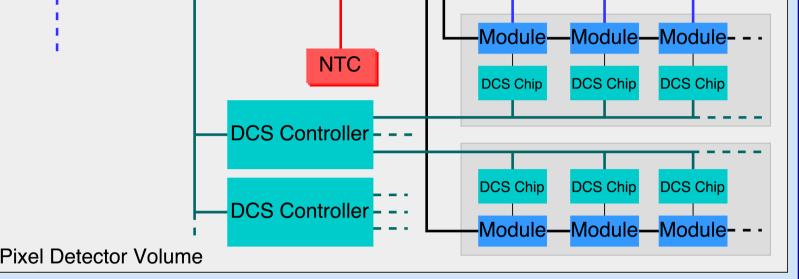

#### Monitor and control on module level **Diagnostics path**

- Through readout

- Front End (FE) information

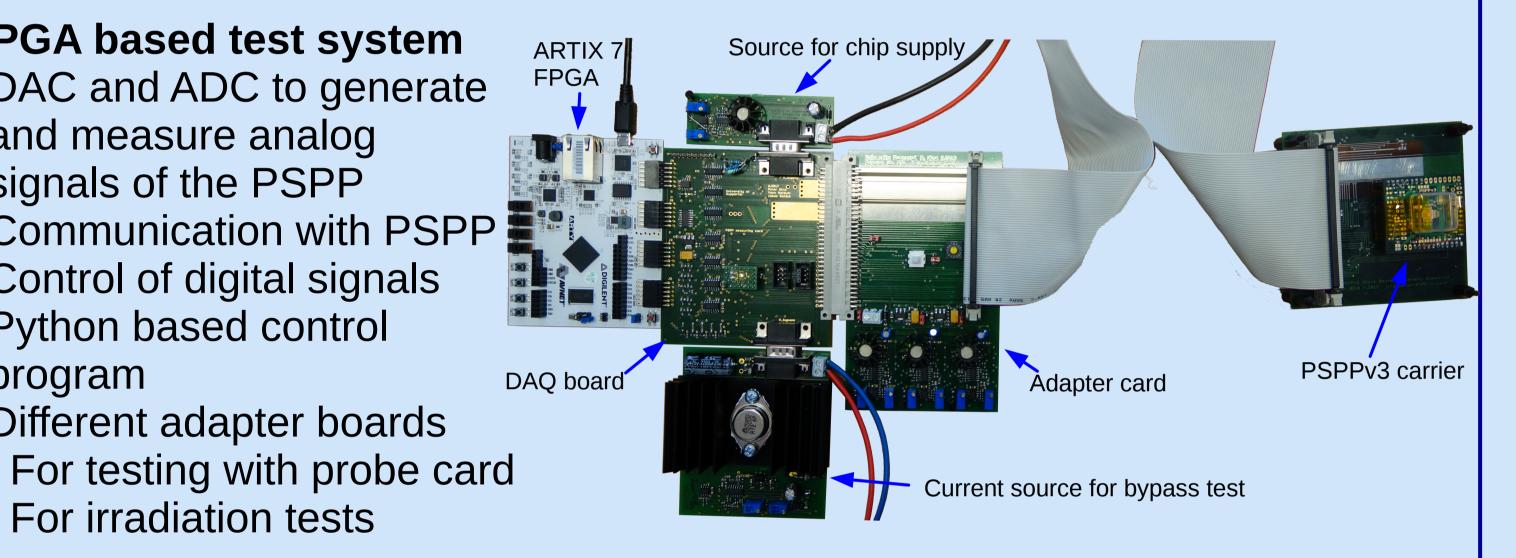

**FPGA** based test system

and measure analog

signals of the PSPP

Python based control

program

Regulated

SP

• DAC and ADC to generate

Communication with PSPP

Control of digital signals

• Different adapter boards

For irradiation tests

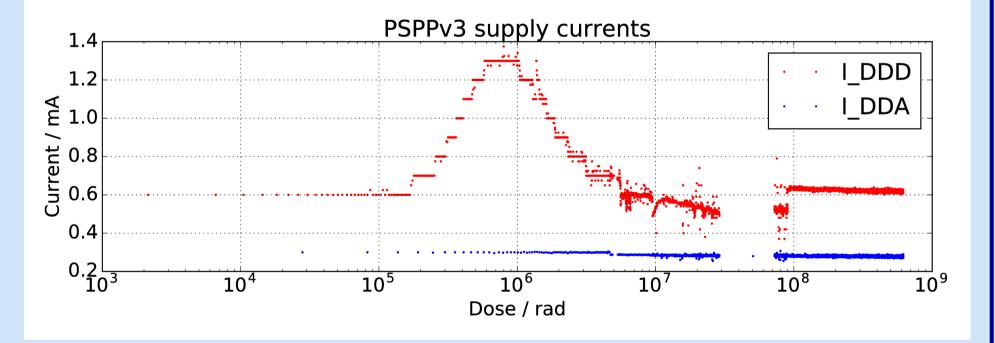

### Irradiation Tests

The PSPPv3 and PARC chips were irradiated with a X-Ray machine up to a total ionizing dose (TID) of 600 Mrad

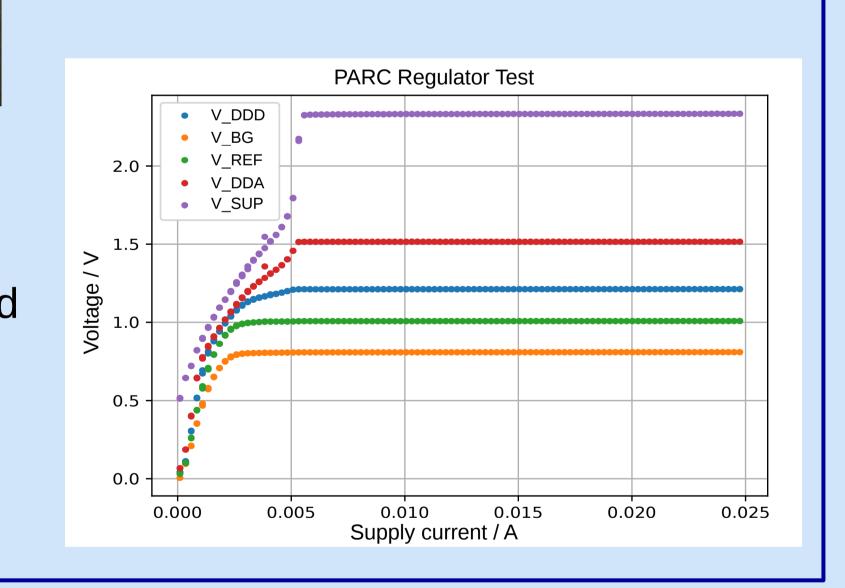

## **PSPP Add-on Regulator Comparator chip (PARC)**

- Add-on chip with remaining rad-hard elements of the DCS chip

- Radiation hard shunt regulator and LDO regulators

- Radiation hard comparator

- Test logic for SEU measurements

# Longterm Tests

- A single PSPPv3 was tested in a climate chamber at different temperatures, each for 7 days of continuous operation

- Operated at 0 °C, 30 °C and 50 °C

- Bypass activated for 23 h and deactivated for 1 h

- 3 A serial current applied during the whole time

#### • First 10 Mrad with lower dose rate of 235 krad/h • Afterwards with 3.2 Mrad/h up to the full TID

- **PSPPv3** irradiation • Observed expected rise in digital current at 1 Mrad for used technology

- Stable communication during the test

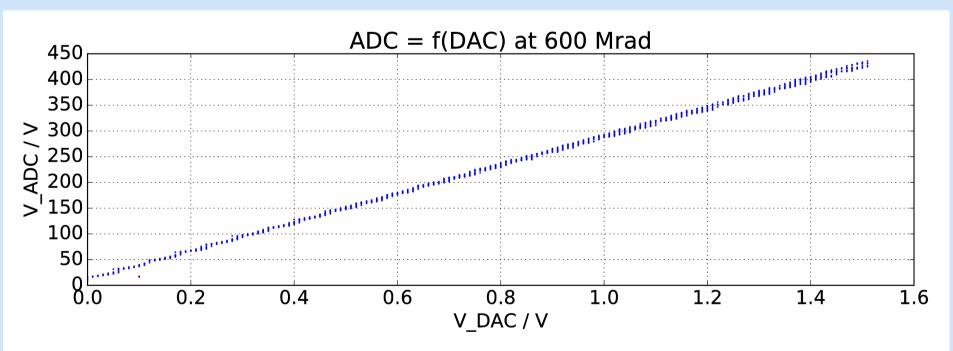

- ADC working and stable readout for the entire TID

- Bypass operational after irradiation

- $R_{ON}$  increased by 6 m $\Omega$

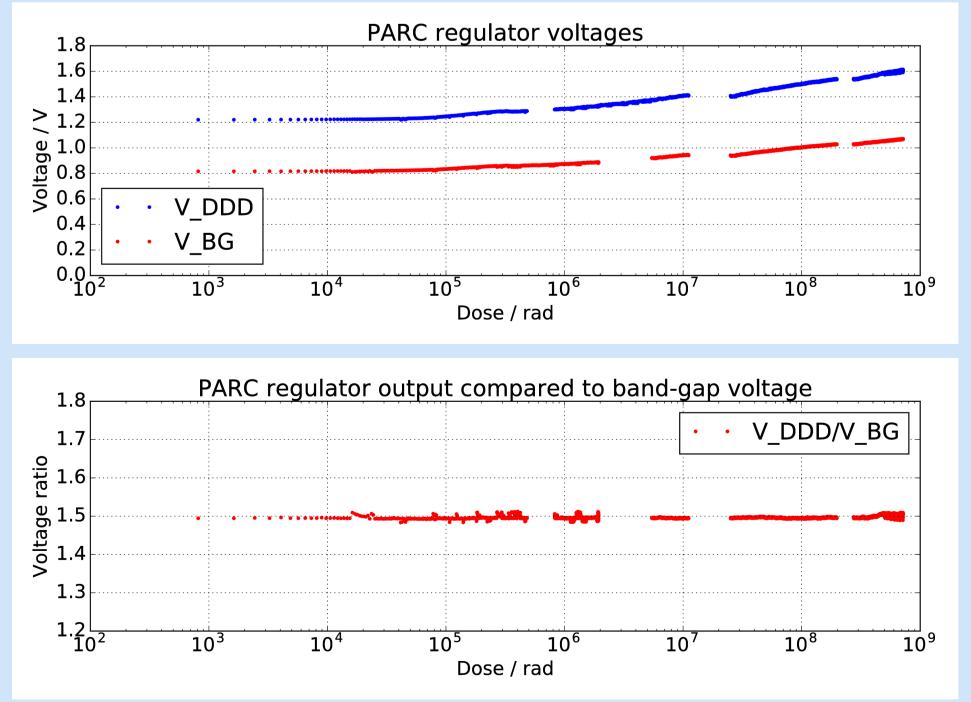

#### **PARC** irradiation

- Drift in the band-gap observed

- Comparator working during entire irradiation

Logic ADC • Stable communication during entire Constant value measured : 557 ± 3 mV test duration • Error smaller than 50 mV compared to • No error in registers detected volt meter

Oscillating behavior observed at a small input difference (< 50mV) • Regulators operating throughout full irradiation

### Outlook

Padframe proposal

for PSPPv4

- Additional characterization measurements of the PARC regulators are planned

- Next prototype v4 in development • Merge of PSPPv3 and PARC

- Fix of observed problems • Change from wirebonds to bump bonds Submission in Nov 2017

| Ŕ  | 161 | 161   | 1\$ | 16h | KA (       | H C        | Nøl. | KK (  | 1E  | 151        | /ø | 16 | 161 |                     |

|----|-----|-------|-----|-----|------------|------------|------|-------|-----|------------|----|----|-----|---------------------|

| Ì  | Ø   | Ø     | Ø   | Ø   | Ø          | )Q)        | ()E  | Ø     | Ø   | )S         | Ø  | Ø  | )Ø  |                     |

| ø  | Ø   | Ø     | Ø   | Ø   | Ø          | 13         | Ø    | Ø     | Ø   | Ø          | Ø  | Ø  | Ø   |                     |

| Ø  | Ø   | Ø     | Ø   | Ø   | Ø          | Ø          | Ø    | Ø     | Ø   | Ø          | Ø  | Ø  | Ø   |                     |

| ø  | Ø   | Ø     | Ø   | Ø   | Ø          | )S)        | Ø    | Ø     | Ø   | Ø          | Ø  | Ø  | Ø   | TAKARI CARARI DARAD |

| ø  | Ø   | Ø     | Ø   | Ø   | Ø          | )Ø         | Ø    | Ø     | Ø   | Ø          | Ø  | Ø  | Ø   |                     |

| Ø  | Ø   | Ø     | Ø   | Ø   | Ø          |            | Ø    | Ø     | B   | Ø          | Ø  | Ø  | Ø   |                     |

| Ì  | )ES | KS)   | Ø   | R   | )S         | )Q)        | )È   | ) (ST | Ø   | Ø          | Ø  | Ø  | )Q  |                     |

| Ø  | Ø   | Ø     | Ø   | Ø   | Ø          | ) <u>s</u> | Ø    | Ø     | Ø   | Ø          | Ø  | Ø  | Ø   |                     |

| Ì. | JØ  | Ø     | Ø   | )Ø  | Ø          | )Q)        | Ø    | \$    | S   | Ø          | Ø  | Ø  | Ø   |                     |

| Ì  | Ø   | JØ    | Ø   | Ø   | Ø          | )Q)        |      | Ø     | Ø   | )ø         | Ø  | Ø  | )Ø  | छान्ने छान्ना छ     |

| Ø  | Ø   | S     | Ø   | Ø   | Ø          |            | Ø    | Ø     | Ø   | Ø          | Ø  | Ø  | Ø   |                     |

| Ø) | E)  | Ø     | )S  | Ø   | Ø          | )Ø         | Ø    | Ø     | )Q  | Joj        | Ø  | Ø  | )Q) |                     |

| Ø  | E   | Ø     | Ø   | Ø   | )\$\$      | Ø          |      | Ø     | Ø   | ) <u>s</u> | Ø  | Ø  |     |                     |

| Ø  | Joj | )\$\$ | )   | Jø/ | J <u>S</u> |            | )ø   | )\$\$ | (B) | 101        | )æ | 13 | Sø  |                     |