# A 4-Channel Parallel 56 Gb/s CMOS Optical Receiver for VCSEL-Based Optical Links

Chaosong Gao<sup>a</sup>, Datao Gong<sup>b</sup>, Quan Sun<sup>b</sup>, Le Xiao<sup>a</sup>, Di Guo<sup>b</sup>, Dongxu Yang<sup>b</sup>, Wei Zhou<sup>a</sup>, Jingbo Ye<sup>b</sup>, Huili Kang<sup>a</sup>, Xiangming Sun<sup>a,1</sup>

<sup>a</sup>Department of Physics, Central China Normal University, Wuhan, Hubei 430079, P.R. China

<sup>b</sup>Department of Physics, Southern Methodist University, Dallas, TX 75275, USA

<sup>1</sup>sphy2007@126.com

## **Abstract**

A 4-channel 14 Gb/s CMOS optical receiver for VCSEL-based optical links is presented. The receiver has been manufactured in a 65 nm CMOS process. Simulation results under extracted layout parasitics and a model of a wire-bonded photo diode demonstrate the receiver has a bandwidth of 10.2 GHz, an input sensitivity of better than 20  $\mu$ A<sub>pp</sub>, an input-referred noise of 2.3  $\mu$ A<sub>rms</sub> and a differential output amplitude across an external 50 ohm load of larger than 400 mV<sub>pp</sub>. The power consumption is 84 mW/channel for a power supply of 1.2 V.

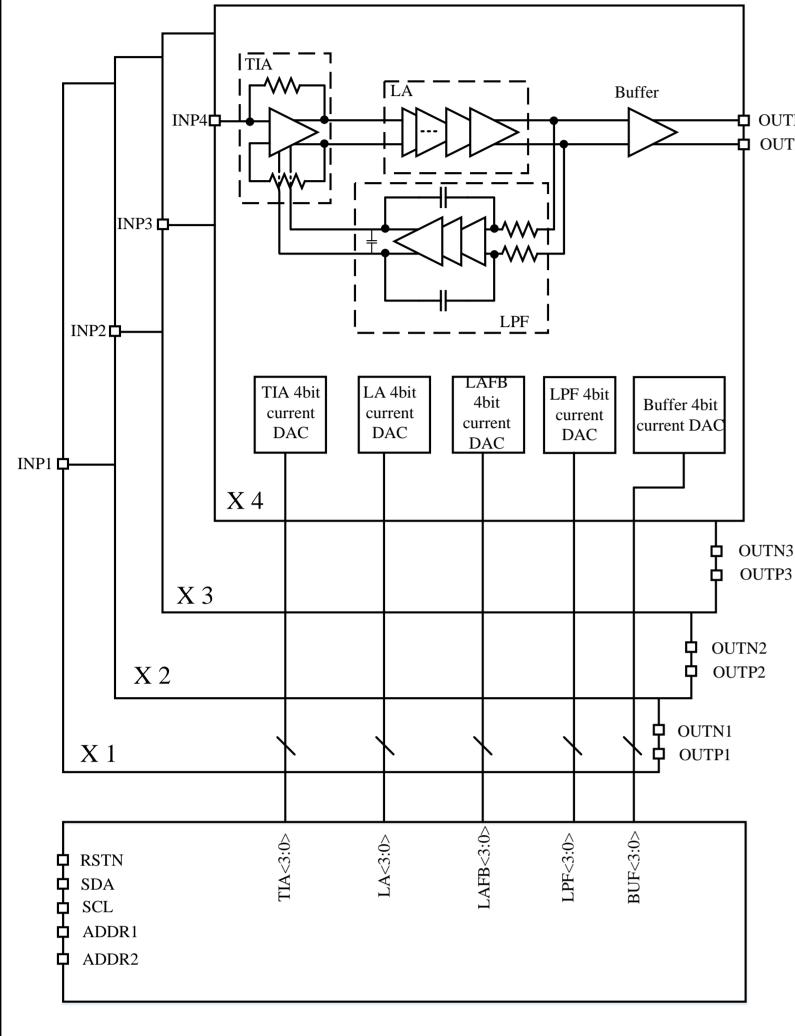

# The system-level block diagram

The receiver is a four-channel array, each channel is up to 14 Gbps. Each channel consists of a pseudo-Transimpedance differential Limiting Amplifier (TIA), Amplifier (LA) with interleaving active feedback and an output buffer. A 250 μm pitch between channels is designed with the same as the offchip photo diode array. The receiver do out no modulation de la out no modulation current  $I^2C$ programmable through an controller. The I<sup>2</sup>C controller is designed with Triple Modular Redundancy (TMR) to increase the Single Event Upset (SEU) effect immunity.

The LA of the first and the second channels are different from the one of the third and the fourth channels.

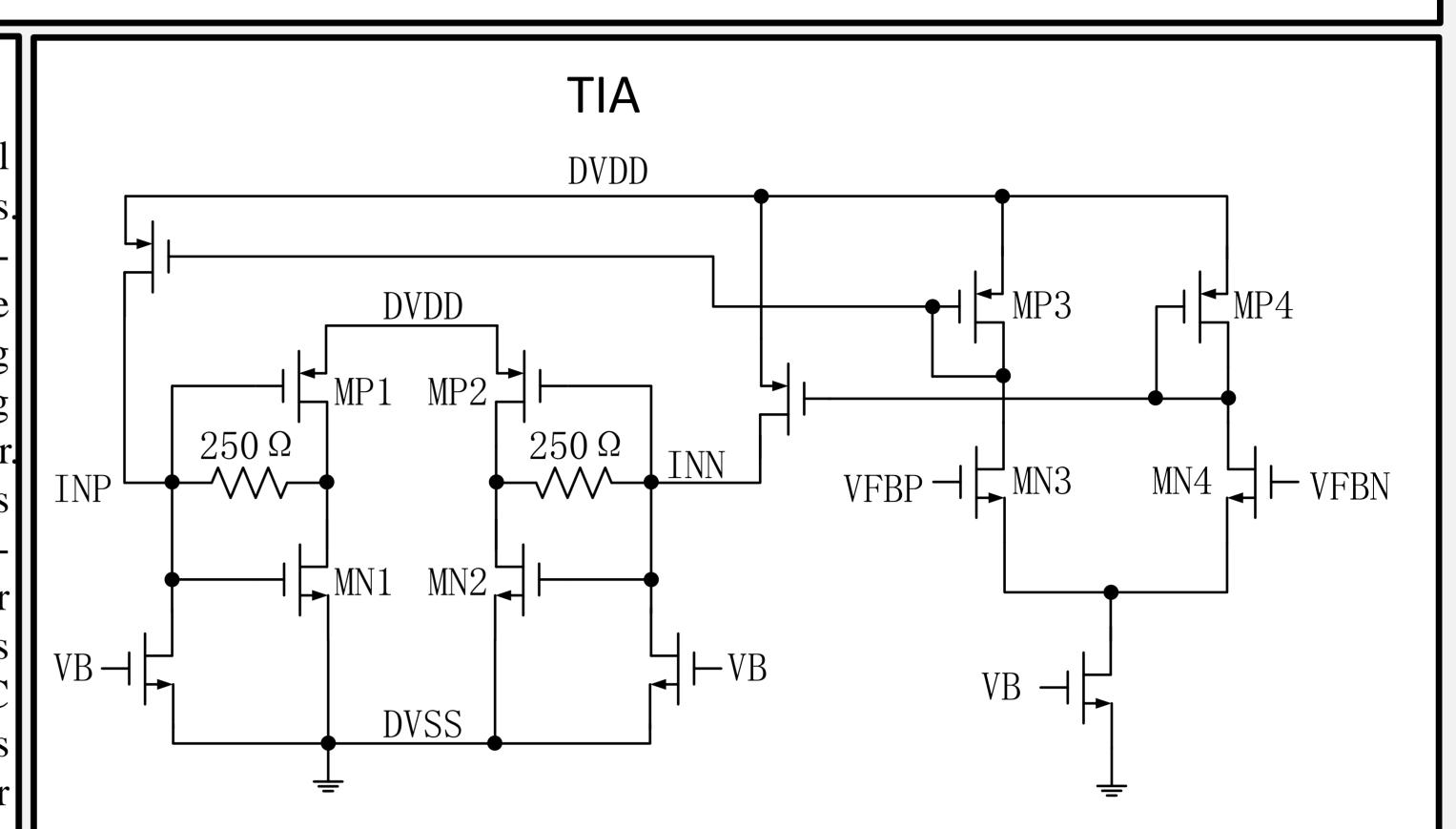

The TIA adopts a pseudo-differential structure to improve the power supply rejection ratio and common mode rejection ratio. A pair of CMOS inverters with resistive feedback, one active and one a replica, are used in the TIA. The simulation results show that the TIA gain is 200 ohm. With a photo diode DC coupled to the TIA, a 2.47  $\mu$ A<sub>rms</sub> input-referred noise and a 25 GHz bandwidth is measured in the post-layout simulations. The power consumption of the TIA is around 7.2 mW for a power supply of 1.2 V.

9 inductors are used in channel 1 and channel 2, respectively.

3 inductors are used in channel 3 and channel 4, respectively.

Two ground PADs are inserted between adjacent channels in order to reduce the crosstalk from the adjacent input signal bonding wires.

# Output Buffer $60 \Omega \geqslant 60 \Omega$ $INP \rightarrow INN$ $VB \rightarrow INN$

The output buffer driving off-chip transmission line is a differential amplifier with a load resistance of 60 ohm. The bandwidth of the output buffer is 17 GHz with a power consumption of 14.4 mW for a power supply of 1.2 V.

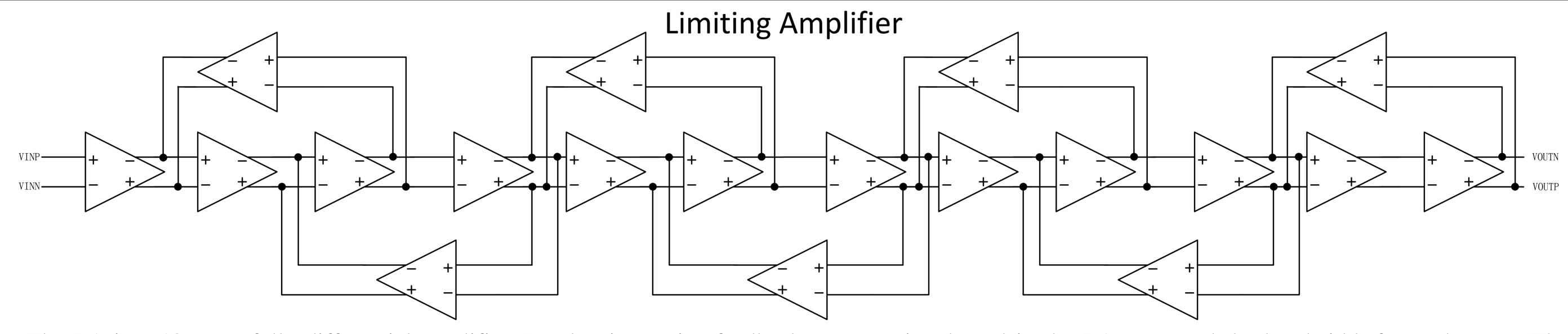

The LA is a 12-stage fully differential amplifier. Interleaving active-feedback structure is adopted in the LA to extend the bandwidth for each stage. The shunt inductive peaking technique is used to extend bandwidth in the last three-stage differential amplifiers of LA at the expense of area. The simulation demonstrates that the LA has a gain of 51 dB and a bandwidth of 13.3 GHz. The LA consumes 57 mW in total for a power supply of 1.2 V.

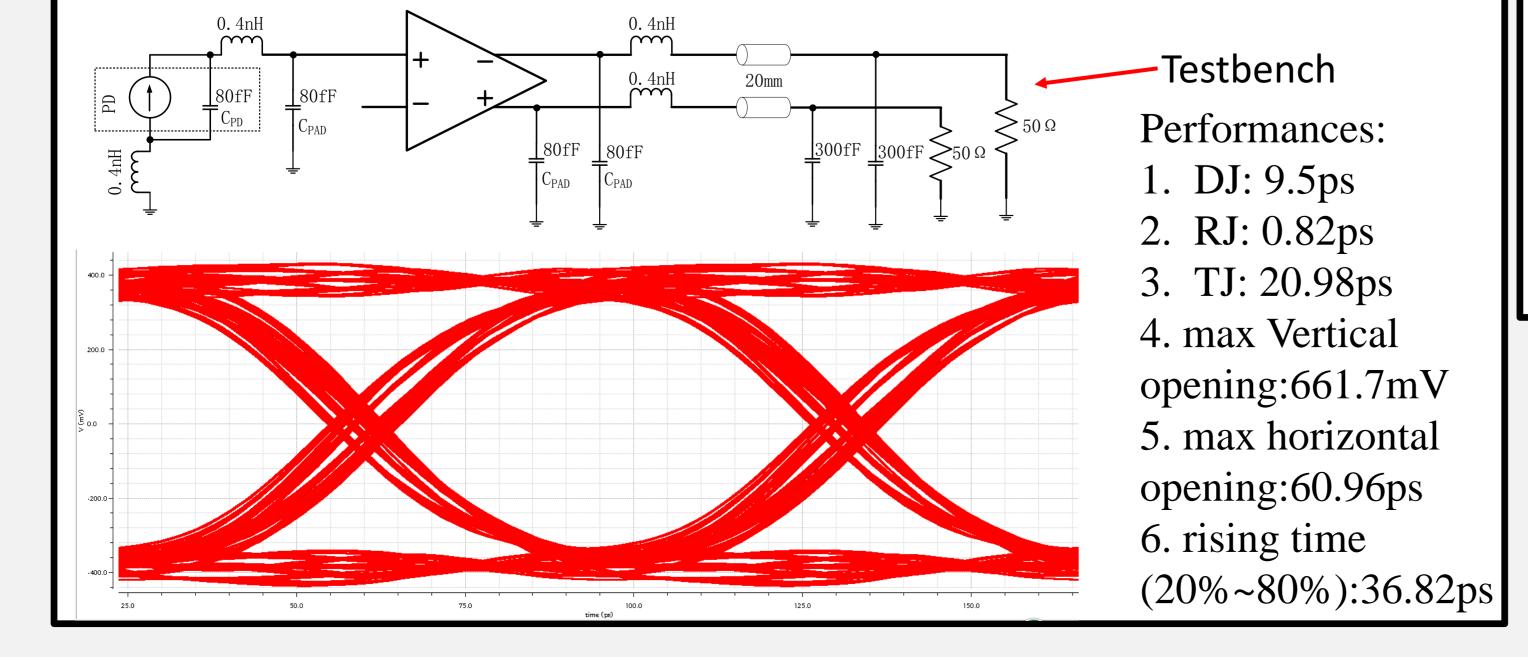

### Simulation results

Setup: 14-Gbps PhotoDiode (PD) model, Input single-end current peak-to-peak 20 µApp 14-Gbps PRBS-7 signals, using channel 3 for the post-layout simulations.

# **Conclusions**

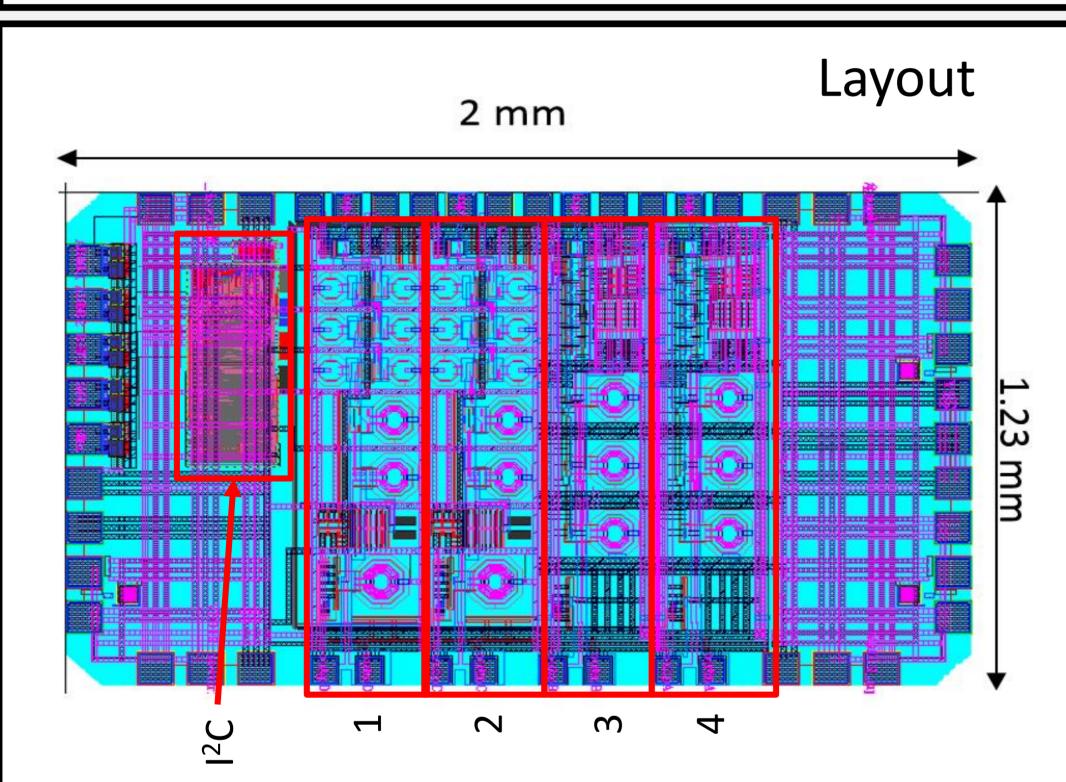

The 4-channel parallel 56 Gbit/s optical receiver for VCSEL-based optical links has been manufactured in a 65 nm CMOS process in April 2017. The dimension of the whole chip is 1.23 mm  $\times$  2 mm. The simulation demonstrates that the receiver has a bandwidth of 10.2 GHz, an input sensitivity of better than 20  $\mu$ A $_{pp}$ , an input-referred noise of 2.3  $\mu$ A $_{rms}$  and a differential output amplitude across an external 50 ohm load of larger than 400 mV $_{pp}$ , and consumes 84 mW/channel for a power supply of 1.2 V. The receiver is just under the test and we will get the results soon.

Topical Workshop on Electronics for Particle Physics (TWEPP 2017), Santa Cruz, USA, 11-15 September 2017