## MATISSE: a low power front-end electronics for MAPS characterization

J. Olave<sup>1,2</sup>, A. Rivetti<sup>2</sup>, L. Pancheri<sup>4,6</sup>, S. Panati<sup>1,2</sup>, F. Cossio<sup>1,2</sup>, S. Mattiazzo<sup>5</sup>, M. Da Rocha Rolo<sup>2</sup>, N. Demaria<sup>2</sup>, P. Giubilato<sup>3,5</sup>, D. Pantano<sup>3,5</sup>

## Abstract

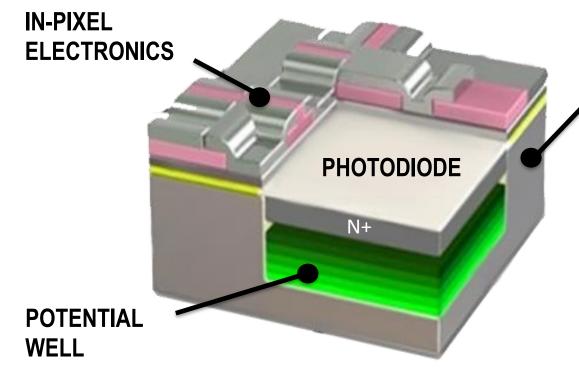

□ The future generation of **HEP experiments** must deal with unique requirements, encouraging the development of novel radiation silicon sensors technologies suitable for extreme radiation environments. In recent years monolithic pixel sensors (MAPS) are becoming increasingly attractive thanks to their good properties. Here are proposed the first results of a flexible front-end electronics developed into an R&D program of monolithic sensors.

- SILICON **SUBSTRATE**

- □ Cost

- High granularity

- □ No bump bonding required

### CONs

- □ Low flexibility

- Small area for the electronics

- Sensor only partially depleted

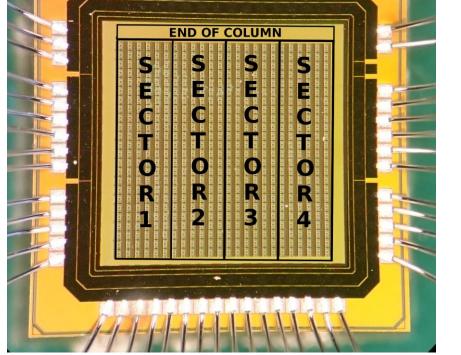

- □ First prototype developed in 0.11 µm CMOS VLSI technology with a die area of 2×2 mm<sup>2</sup>

- □ The chip has been received from the foundry in April 2017

- □ It consists of 24×24 pixel matrix organized in 4 independent sectors (6×24) and an End of Column logic (EoC)

- □ The analog data is sent off-chip through two independent data buses shared between the pixels of each sector

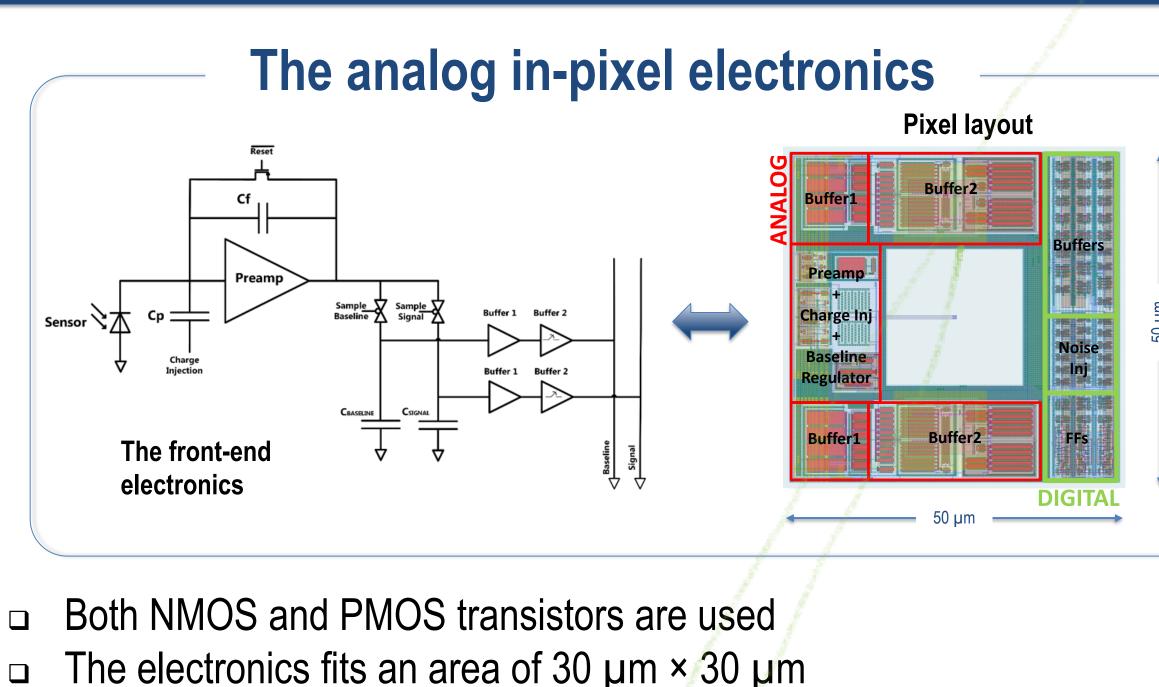

## The pixel unit

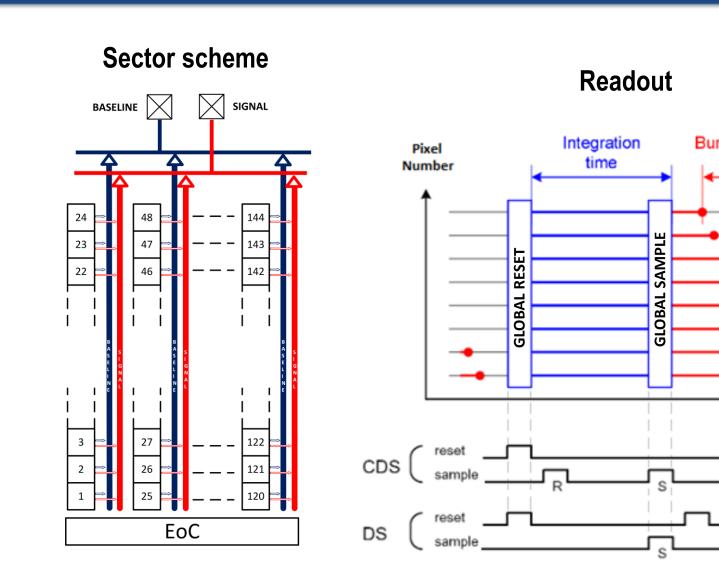

## The readout operation

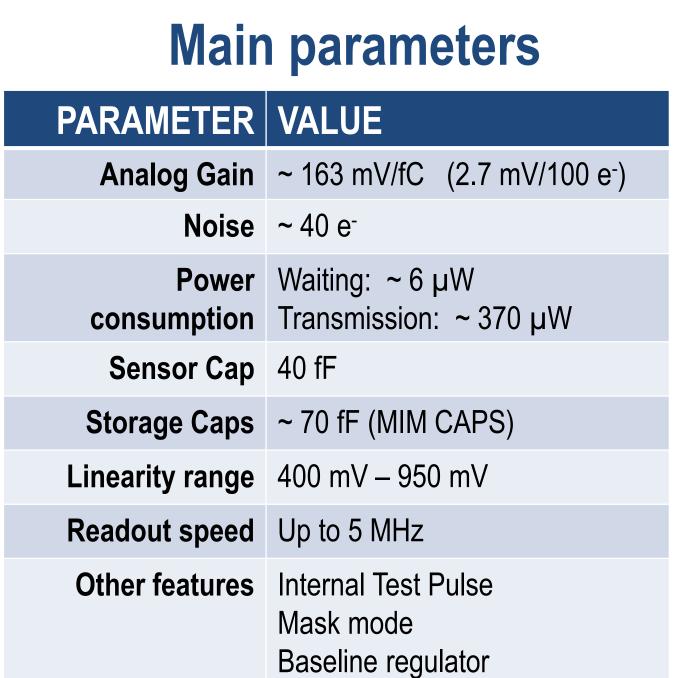

□ MATISSE supports snapshot shutter operation □ The integration time can be as short as 100 ns

**Shutter type** Snapshot shutter

**Readout type** Correlated Double Sampling

- Digital in-pixel logic manages:

- - The baseline voltage - The mask mode

- The test pulse injection

- The regeneration of digital signals

□ The logic sequentially addresses the pixels of the sector

- □ The four sectors are readout in parallel

- □ Two analog outputs are sent off-chip

## The full readout chain

# MATISSE CHIP MEZZANINE **MOTHER BOARD** DAQ BOX

□ ASIC and mezzanine connected through wire bonding □ The mother board contains most part of the electronics The DAQ box is based on:

### **NOISE DISTRIBUTION**

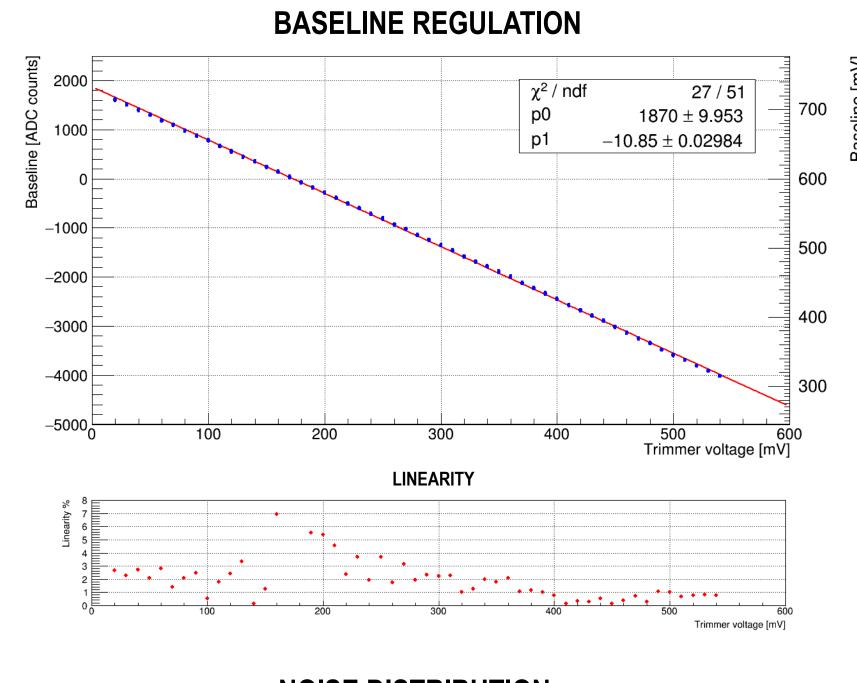

#### The baseline can be tuned as desired up to 300 mV with a good linearity in the full range

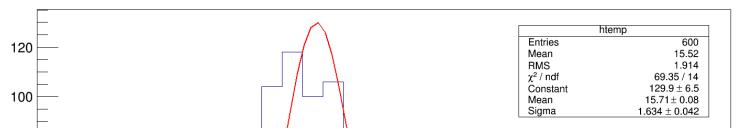

The measured noise is 15 ADC counts (1mV). It is measured as the fluctuation of the baseline of each pixel after the regulation

### LASER PULSE RECONSTRUCTION

**Experimental results**

- custom analog board 5 CHs, 14 bit, 100 MHz - commercial FPGA board

### **NOISE IN THE FULL CHAIN**

| DEVICE                 | NOISE [ADC] | NOISE [mV] |

|------------------------|-------------|------------|

| DAQ                    | 0.2         | 0.02       |

| DAQ + MB               | 0.2         | 0.02       |

| DAQ + MB + MEZZ        | 1.6         | 0.11       |

| DAQ + MB + MEZZ + ASIC | 15          | 1          |

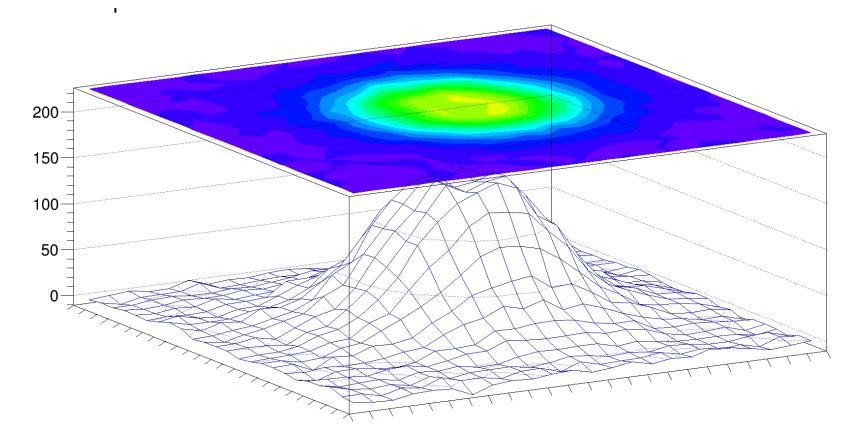

- □ The analog input sent to the DAQ box allows the reconstruction of laser pulses

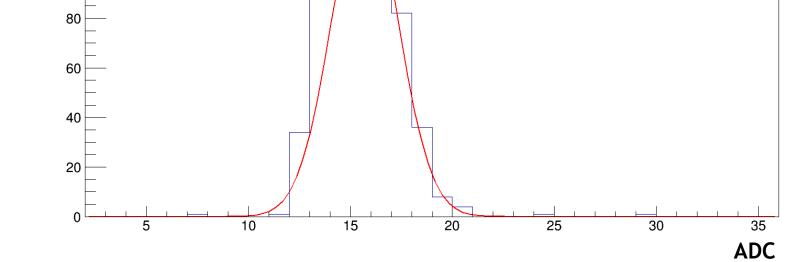

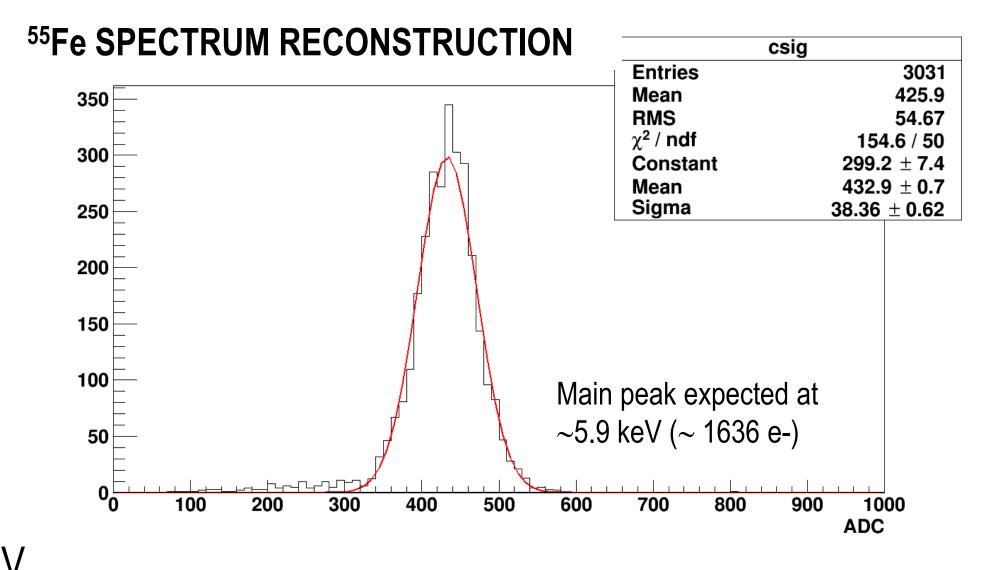

- □ The full system has been used also with an active source (<sup>55</sup>Fe). The reconstructed spectrum allows to clearly distinguish the main peak expected at  $\sim 5.9$  keV

Contacts: olave@to.infn.it

POLITECNICO DI TORINO

Istituto Nazionale di Fisica Nucleare **SEZIONE DI TORINO**

1 – Politecnico di Torino 2 – INFN sezione di Torino 3 – INFN sezione di Padova 4 – Università di Trento 5 – Università di Padova 6 - TIFPA