# ATLAS Phase-II Upgrade Pixel Data Transmission Development

## Jason Nielsen, on behalf of the ATLAS ITk project

Santa Cruz Institute for Particle Physics, University of California, Santa Cruz jnielsen@ucsc.edu

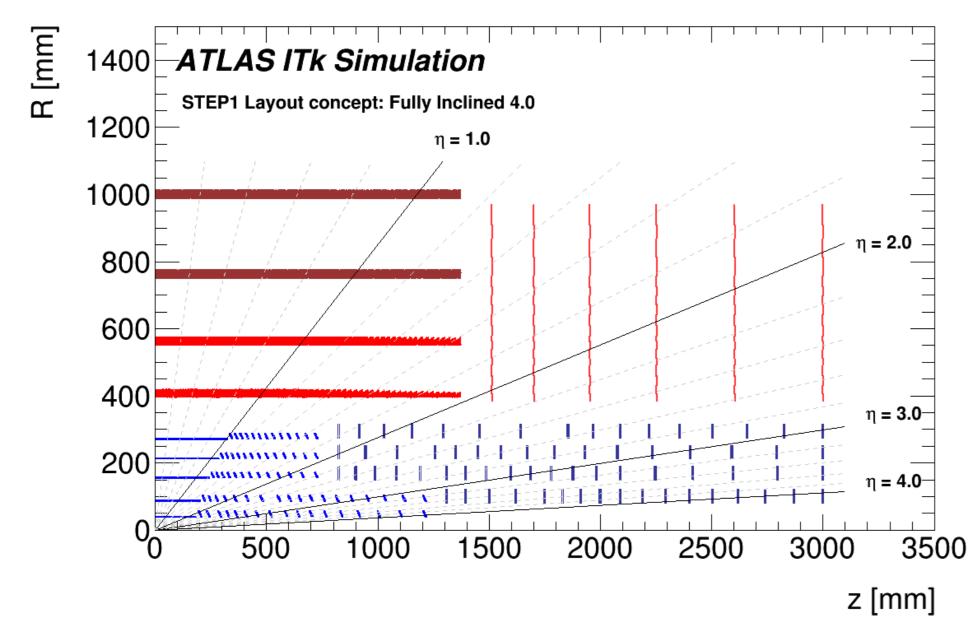

### Pixel system of ATLAS ITk project for HL-LHC

Proposed pixel system (in blue), consists of 5 barrel layers with flat and inclined sensors, plus endcap rings.

Several meters of electrical links run through the high-radiation environment of the pixel volume to the optical transceivers.

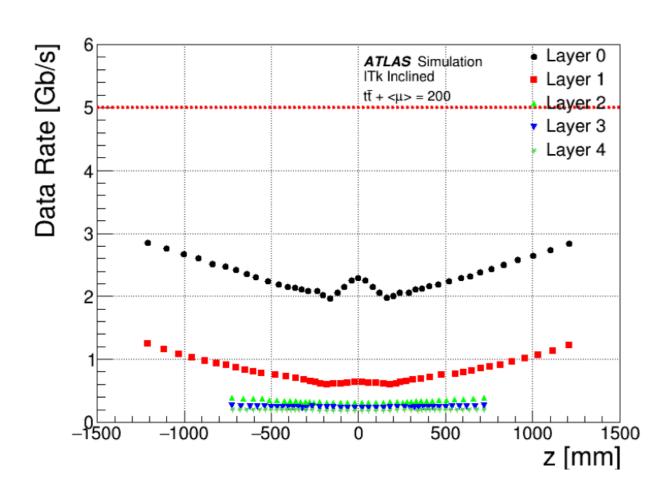

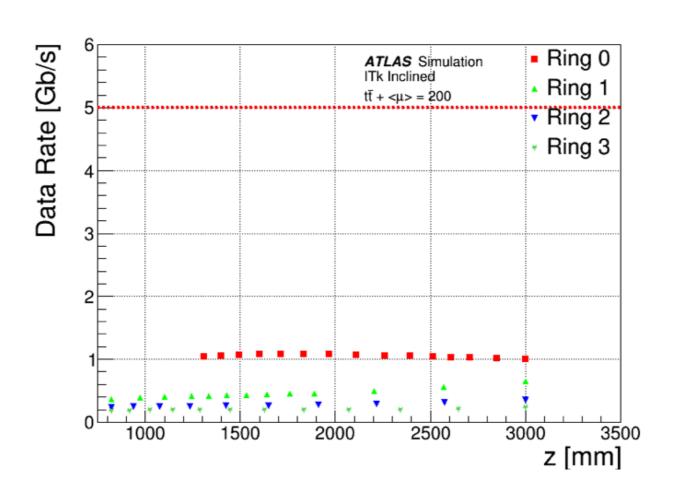

Simulated data rates [below] fit within the 5.12 Gb/s bandwidth requirement, assuming  $\langle \mu \rangle = 200$  and full read-out at Level-0 trigger rate of 1 MHz (baseline). Outer layers are fully read out at backup mode of operation (Level-0 rate of 4 MHz).

### 5.12 Gb/s Electrical Data Transmission System Design Goals

- Differential signaling with 100 or  $70\Omega$  impedance, using balanced signal coding (64B/66B) and AC-coupling.

- Attenuation less than 20 dB end-to-end at 3.0 GHz (safely above Nyquist frequency), including connectors. This leads to open eye diagrams with conventional signal conditioning implementations.

- Bit-Error Rates < 10<sup>-12</sup> with standard pseudo-random data

- Electrical and mechanical tolerance to 10 MGray expected radiation dose in innermost layers.

### **Physical Layer Prototypes**

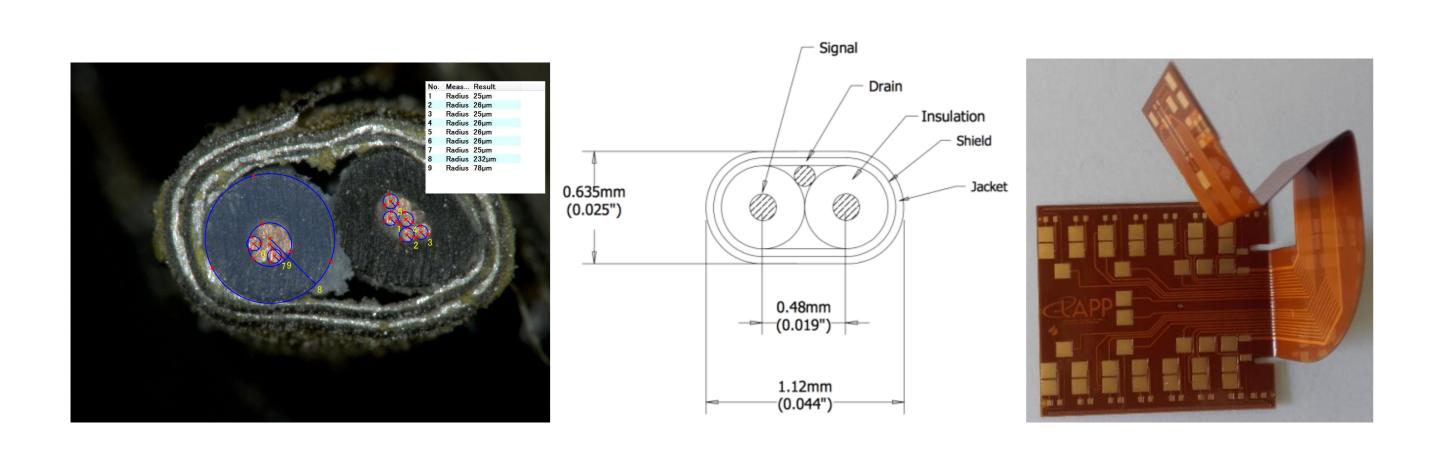

Several low-mass physical implementations are being characterized for use in different parts of pixel detector system:

- Small-gauge shielded twisted wire pairs (TWP) [below left]

- Shielded twin-axial cable (TA) of various gauges [below center]

- Low-mass flexible circuits (flex) [below right]

#### **Preliminary Measurements**

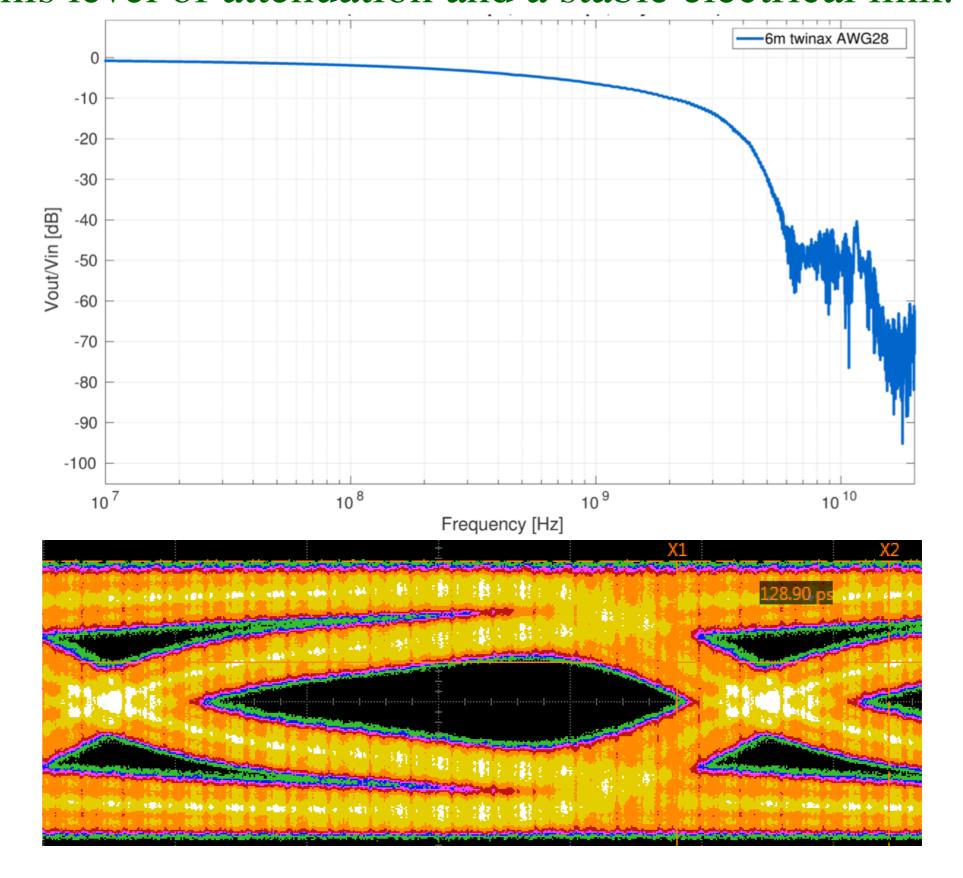

Differential S-parameters and voltage transfer function measured with 4-port vector network analyzer. Transfer function plot [below], for TA 28 AWG, shows attenuation of approximately 20 dB at 4 GHz. The corresponding open eye diagram at 2.56 GHz shows the relationship between this level of attenuation and a stable electrical link.

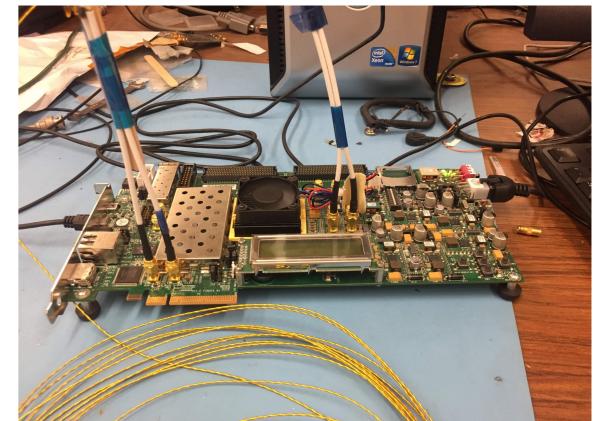

Bit-Error Rate (BER) tests use Xilinx FPGA boards [right] with multi-gigabit transceivers. Tests verify maximum transmission rates that satisfy stricter BER < 10<sup>-14</sup>.

| Device     | Length | Attenuation @ 3 GHz | Max Rate (DC bal.) |

|------------|--------|---------------------|--------------------|

| TA 28 AWG  | 6 m    | 14 dB               | 8.000 Gb/s         |

| TA 30 AWG  | 6 m    | 17 dB               | 6.220 Gb/s         |

| TA 34 AWG  | 4 m    | 20 dB               | 6.220 Gb/s         |

| TWP 36 AWG | 1 m    | 5 dB                | 4.976 Gb/s         |

### **Signal Conditioning Development**

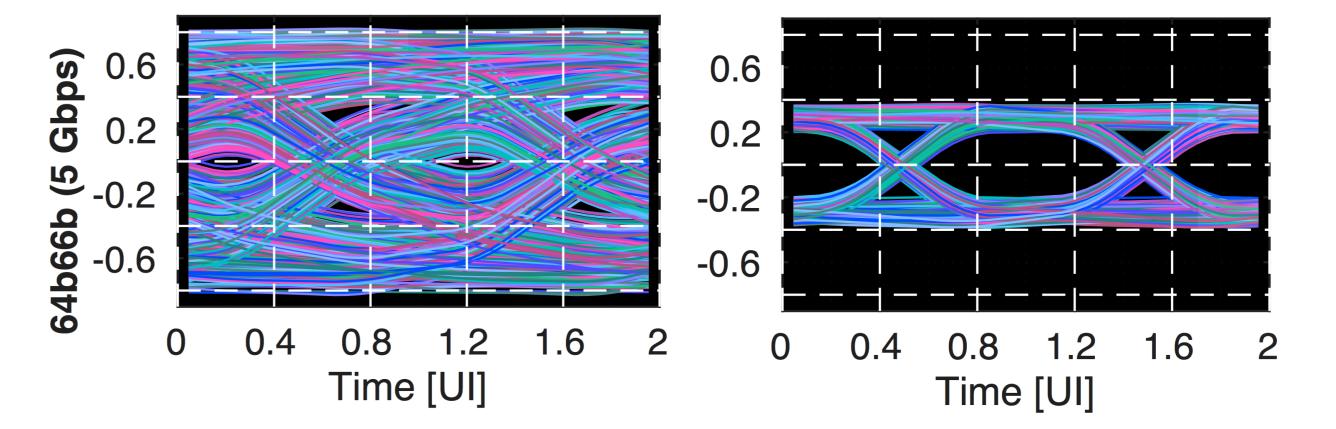

High-frequency roll-off in system requires active compensation:

- Pre-emphasis boosts the high-frequency components of the waveform, compensating for the specific properties of a chosen system.

- Receiver equalization acts as a high-pass filter, either fixed or based on dynamic feedback to optimize signals (before/after shown below).

### **Conclusions**

- Some prototypes achieve design goals for 5.12 Gb/s transmission over distances up to 6 m; others for shorter total distance.

- Aggressive signal conditioning is a necessity for the final system.