# **TWEPP Poster Session - UCSC, 13th September 2017 DEVELOPMENT OF THE NEW TRIGGER PROCESSOR BOARD** FOR THE ATLAS LEVEL-1 ENDCAP MUON TRIGGER FOR RUN-3

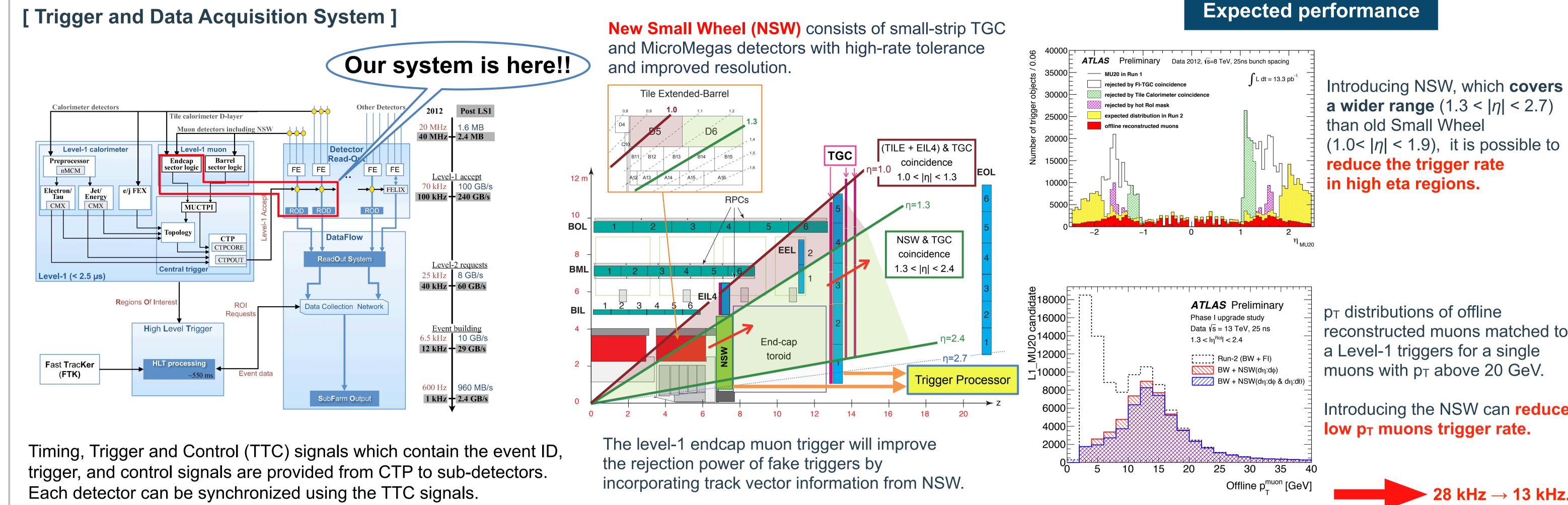

### ATLAS Muon Trigger System

With the current system, the trigger rate above a p<sub>T</sub> threshold of 20 GeV would be an unacceptable rate (~28 kHz) of the Level-1 system at an instantaneous luminosity of 3 × 10<sup>34</sup> cm<sup>-2</sup>s<sup>-1</sup>.

**Introduce the new trigger**

reconstructed muons matched to

Introducing the NSW can reduce

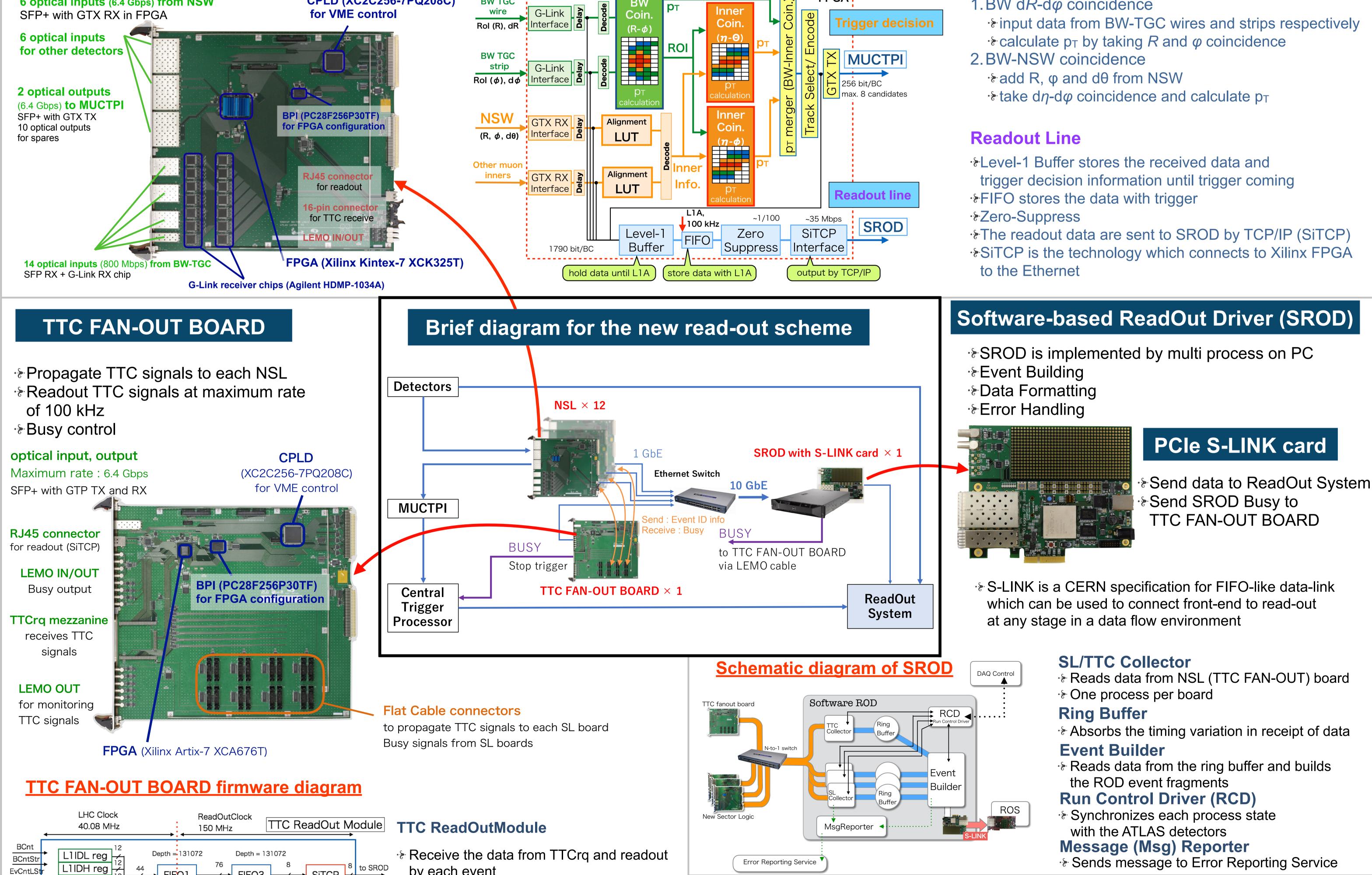

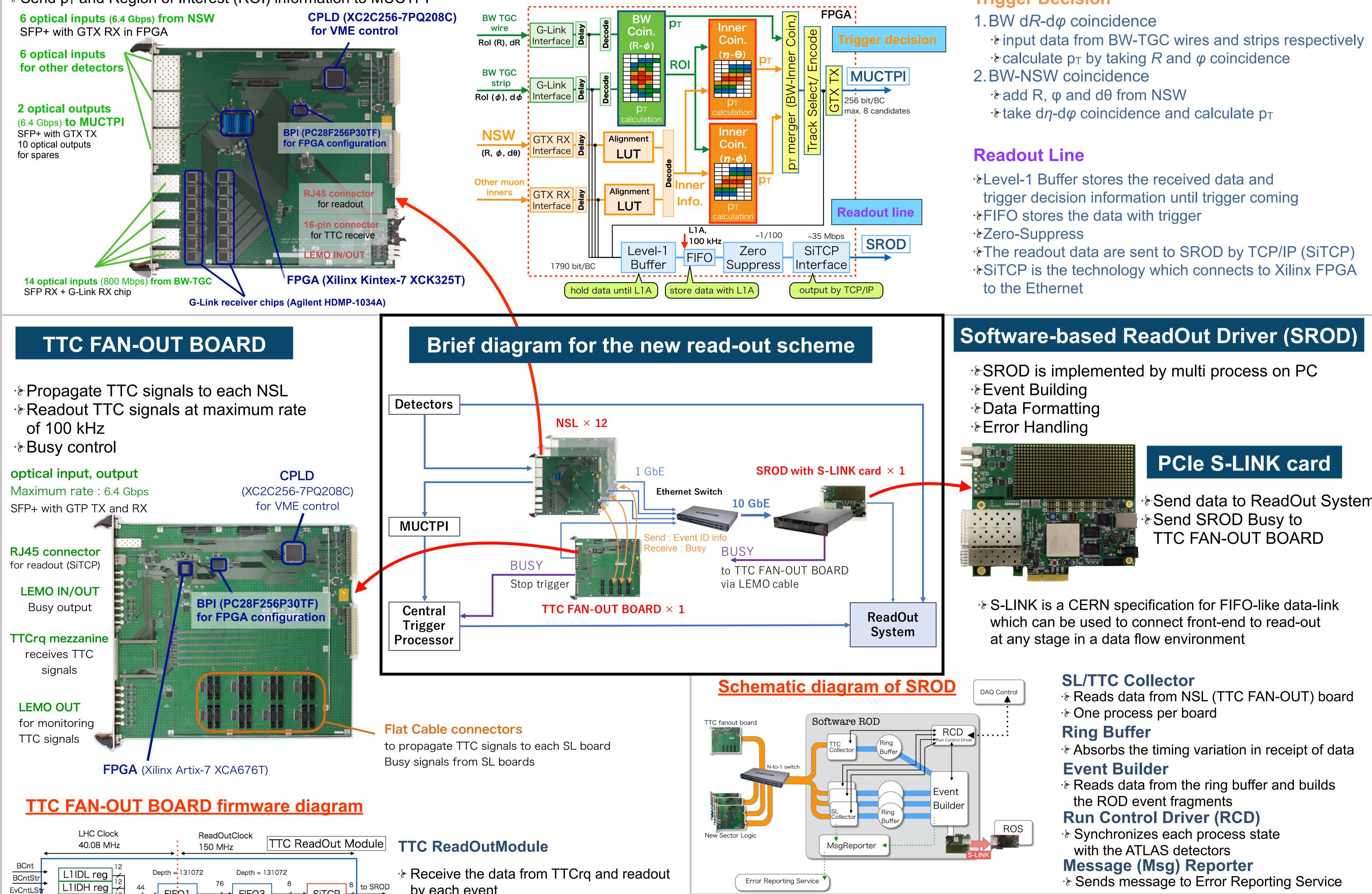

### **Trigger Processor (New Sector Logic)**

$\Rightarrow$  Calculate the muon p<sub>T</sub> for each trigger sector and make trigger decision Send p<sub>T</sub> and Region of Interest (ROI) information to MUCTPI

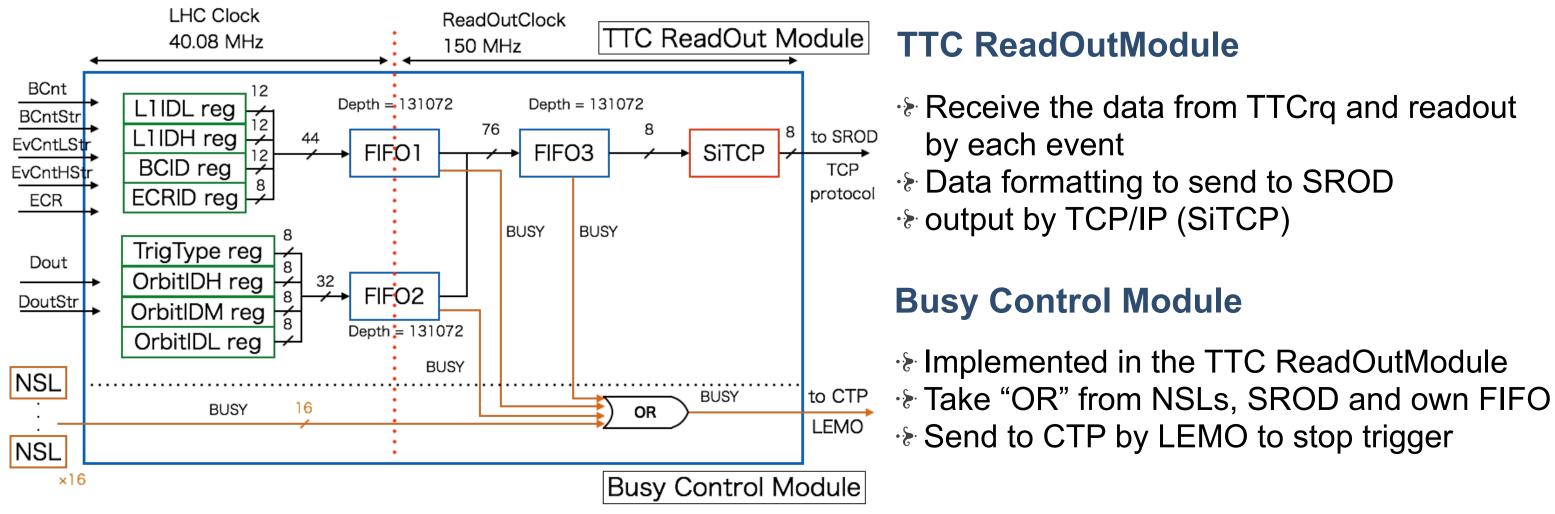

### New Sector Logic firmware diagram

### **Trigger Decision**

### **Current Achievement**

Prototype of NSL and TTC FAN-OUT BOARD were made and its design was verified ✤ A beam test was done using CERN SPS Beam Facility and checked whole phase-1 system (NSL, TTC FAN-OUT BOARD and SROD) is working

### **Future Plan**

✤ Test for actual setup which uses 12 NSL, 1 TTC FAN-OUT BOARD and 1 SROD will be performed. Connection test with MUCTPI will be performed

Mass-production of NSL and TTC FAN-OUT BOARD in 2018

## Atsushi Mizukami (KEK), on behalf of the ATLAS Collaboration