## Intel HPC environment for Silicon Design and Key Learnings

Shesha Krishnapura Senior Principal Engineer 2009

Authors & Contributors:

Raju Nallapa, Doug Austin, Ananth Sankaranarayanan, Shaji Achuthan, Vipul Lal, Ty Tang, Shesha Krishnapura, Elwood Coslett

## Legal Disclaimer

- Performance tests and ratings are measured using specific computer systems and/or components and reflect the approximate performance of Intel products as measured by those tests. Any difference in system hardware or software design or configuration may affect actual performance. Buyers should consult other sources of information to evaluate the performance of systems or components they are considering purchasing. For more information on performance tests and on the performance of Intel products, reference <u>www.intel.com/performance/resources/benchmark\_limitations</u> or call (U.S.)1-800-628-8686 or 1-916-356-3104.

- This document is for informational purposes only. THIS DOCUMENT IS PROVIDED "AS IS" WITH NO WARRANTIES WHATSOEVER, INCLUDING ANY WARRANTY OF MERCHANTABILITY, NONINFRINGEMENT, FITNESS FOR ANY PARTICULAR PURPOSE, OR ANY WARRANTY OTHERWISE ARISING OUT OF ANY PROPOSAL, SPECIFICATION OR SAMPLE. Intel disclaims all liability, including liability for infringement of any proprietary rights, relating to use of information in this specification. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted herein.

- Intel, the Intel logo, and Xeon are trademarks of Intel Corporation in the U.S. and other countries.

- \*Other names and brands may be claimed as the property of others.

- Copyright © 2009 Intel Corporation. All rights reserved.

#### Abstract

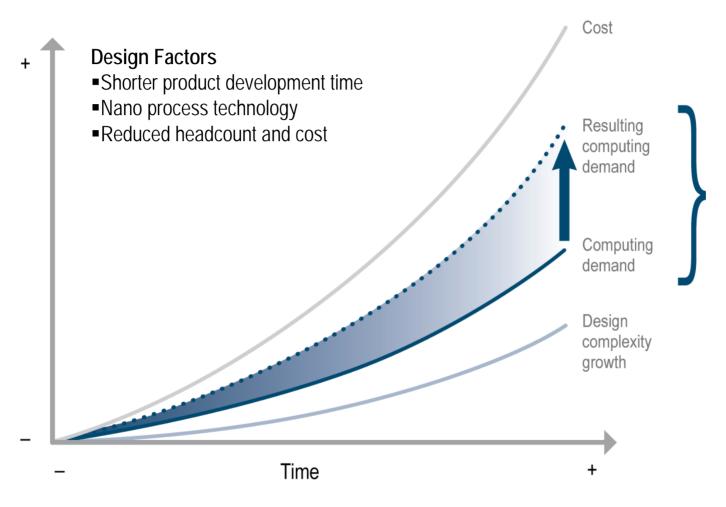

Silicon design technical complexity is increasing every year due to several new features and process technology shrinks. Additionally, the business drivers such as shorter product development time, reduced headcount, and lower cost is increasing pre-silicon verification, high degree of design automation, and global multi-site design teams. These two factors (technological and business) are astronomically increasing demand on computing and storage driving design computing to be engineered as an HPC environment.

This presentation will cover Intel HPC design compute environment, generational improvements, and realized value in the areas of compute clusters, very high large memory servers, optimal network, and parallel storage.

#### Intel Computing Environment and Computing Demand

## Design Team Challenges

- Increased pre-silicon verification

- High degree of design automation

- Global design team and collaboration

#### Intel Data Center Profile

- Intel has four major groups currently driving individual data center requirements (DOME):

- (Design) Design Computing: Support the chip design community and they have most of the servers within Intel

- (Office) General Purpose: Supporting typical IT and customer services

- (Manufacturing) FAB/ATM: Manufacturing computing supporting fabrication and assembly

- (Enterprise) Enterprise applications supporting eBiz

80% of servers in Intel are in "D" 20% of servers are in "OME"

### Design Computing Env Overview

- Classification by server type in "D" environment

- 64,000 Servers running Linux

- 55% Blades (Xeon 2S) All multi-core servers are at 4GB-8GB per core

- 40% 1U (Xeon 2S) Multi-core servers are at 8GB per core

- 5% Rest (Xeon MP) 128GB to 1TB per server

- Classification by use model in "D" environment

- Batch servers (70%)

- Interactive & large memory batch servers (30%)

- High Performance Mega Data Centers:

- Each data center has multiple modules design to handle over 500+ watts/SF

- 6000 sq ft/ per module with ~3MW of useable power

- 200 cabinets/racks per module

- 15-22KW power allocation per rack (48-64 blades per rack)

- Some data centers support 30KW (Up to 84 blades per rack)

#### **Compute Demand Drivers inside Intel**

- Pre-Silicon Design Computing

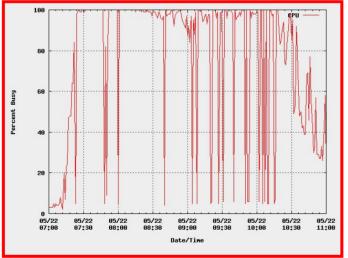

- More than 100,000 simulation jobs per chip design each week for several quarters till tape-in

- Small, Medium, Large memory workloads

- Many chip designs in flight at a given time

- Primarily CPU, and Physical Memory Bound Lately Storage is of concern

- Tape-out Computing

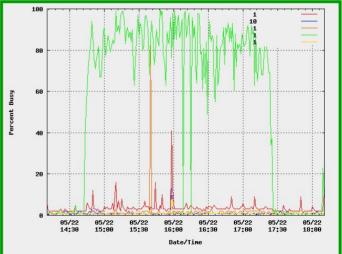

- 16,000 to 23,000 Optical Proximity Correction (OPC) jobs for each of the complex silicon layer

- Small, Large, Very Large memory workloads

- CPU, Network, and Storage Bound

#### Intel HPC Environment

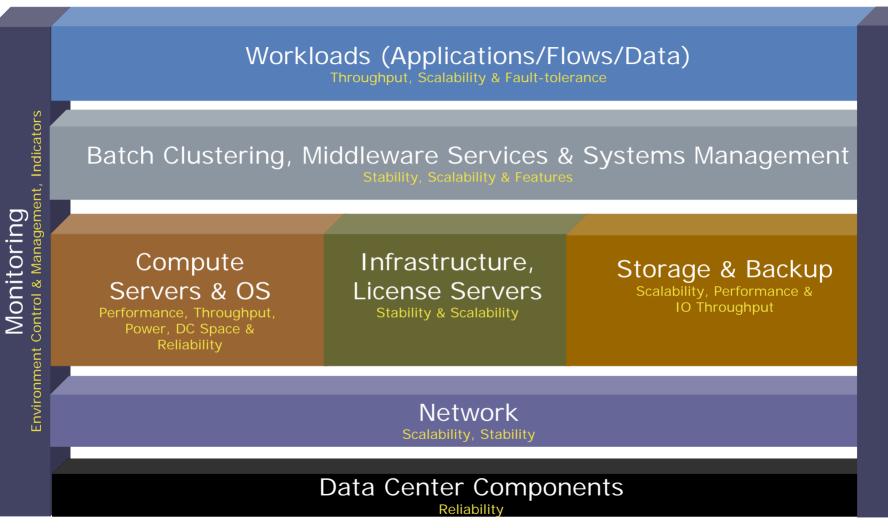

#### **HPC Solution Stack**

#### HPC Capability and Target Use Roadmap

|                                                                                         | 2006 2007                                                                          | 2008                                                          | 2009 2010                                                              |  |

|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|---------------------------------------------------------------|------------------------------------------------------------------------|--|

| HPC Technology Areas                                                                    | HPC-1<br>Optimize for 45nm, Support >=65nm                                         | HPC-2<br>Optimize for 32nm, Support >=45nm                    | HPC-3 Target Additions<br>Optimize for 22nm, Support >=32nm            |  |

| Batch Clustering                                                                        | Systems/Pool: 8.5K (1.3x)                                                          | 11K ( <b>1.3x</b> )                                           | 11K ( <b>1</b> x)                                                      |  |

| Stability, Scalability,                                                                 | Jobs/Pool: 20K+ ( <b>1.5x</b> )                                                    | 30K+ ( <b>1.5x</b> )                                          | 60K+ ( <b>2x</b> )                                                     |  |

| Features                                                                                | Scheduling: Preferential                                                           | Smart Class                                                   | Support for Virtualization                                             |  |

| IO Spec TP#: 5,120 (10x)*Storage & BackupCouldbillte DeformanceVolume Size : 3.2TB (8x) |                                                                                    | 5,120<br>3,500+ MBps ( <b>1.1x</b> )<br>6.4TB ( <b>2x</b> )   | 14,080 ( <b>2.75x</b> )<br>5,300+ MBps ( <b>1.5x</b> )<br>TBD          |  |

| IO Throughput                                                                           | Scalability, PerformanceIO ThroughputSingle-Stream Perf*: 70MBps (1x)              |                                                               | 240 MBps ( <b>1.5x</b> )                                               |  |

|                                                                                         | HW/SW: Parallel-Storage-Gen1 <sup>\$</sup>                                         |                                                               | Parallel-Storage/Open-Standard                                         |  |

|                                                                                         | Storage: 40Gbps (10x)                                                              | 40Gbps ( <b>1x</b> )                                          | 11x1x10Gbps (2.75x)                                                    |  |

| Network<br>Scalability, Stability                                                       | Master: 1Gbps (10x)                                                                | 2x1Gbps (1x, Redundancy)                                      | 10Gbps ( <b>5x</b> )                                                   |  |

|                                                                                         | Slave: 100Mbps (1x)                                                                | 100Mbps ( <b>1x</b> )                                         | 100Mbps/1Gbps (1x/10x)                                                 |  |

| Compute<br>Optimized for Perf,                                                          | Large RAM: 512GB (4x) (Based on Intel Architecture)<br>Perf. TP#: 1.6-5x           | 1TB (2x) (Based on Intel Architecture)<br>1.7x                | TBD                                                                    |  |

| Throughput, Capacity<br>Power & DC Space                                                | Batch Node: 2S/Dual-Core/16GB<br>Perf. TP: 2.1x (With Intel® Xeon® Processor 5150) | 2S/Quad-Core/32GB<br>2.3x (With Intel® Xeon® Processor E5450) | 2S/Quad-Core/48GB<br>1.74x (With Intel® Xeon® Processor X5570 – No HT) |  |

| <b>OS</b><br>New HW Feature Support,<br>Scalability, Stability, Perf.                   | Enterprise Feature: Stable,<br>Inter-System NUMA Support                           | Multi-Core Optimized                                          | Virtualization Optimized                                               |  |

| License Servers<br>Stability, Scalability                                               | Platform: IA Based (3x over RISC)                                                  | Latest IA based solution                                      | Latest IA based solution                                               |  |

| Apps Tuning<br>Throughput                                                               | Tuning: CPU Prefetch (1.2x)<br>Enablement: 512GB Support                           | SSE4                                                          | Hyper-Threading                                                        |  |

(10x)\* = 10x Spec Limit improvement over prior gen. solution (5120 MBps vs. 512MBps);

"Single-Stream Performance" is relevant for Backup & Vol. size; \* Proprietary Software

# TP – Throughput; HWA – Hardware Acceleration

#### HPC Demand & Benefits for Intel Tapeout

#### **Intel Tapeout Computing Metrics**

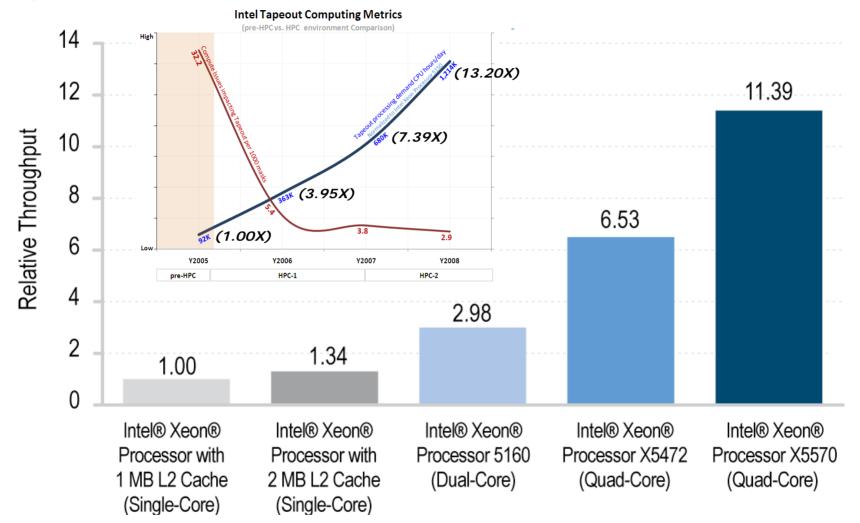

#### EDA Performance Improvement with Intel® Xeon® Processor Generations

#### Intel® Architecture Performance Improvement for OPC

Intel internal measurements May 2007, November 2007, and February 2009.

### **Runtime Performance for OPC Application**

| Processor                                                  | OPC Jobs§ | Runtime<br>(HH:MM:SS) | Relative<br>Throughput |

|------------------------------------------------------------|-----------|-----------------------|------------------------|

| 64-bit Intel® Xeon® Processor with 1 MB L2 Cache (3.6 GHz) | 2         | 10:40:12              | 1.00                   |

| 64-bit Intel® Xeon® Processor with 2 MB L2 Cache (3.8 GHz) | 2         | 07:58:31              | 1.34                   |

| Intel® Xeon® Processor 5160 (3.0 GHz)                      | 4         | 03:34:39              | 2.98                   |

| Intel® Xeon® Processor X5472 (3.0 GHz)                     | 8         | 01:37:58              | 6.53                   |

| Intel® Xeon® Processor X5570 (2.93 GHz)                    | 8         | 00:56:11              | 11.39                  |

§ One OPC job per core.

Intel internal measurements May 2007, November 2007, and February 2009.

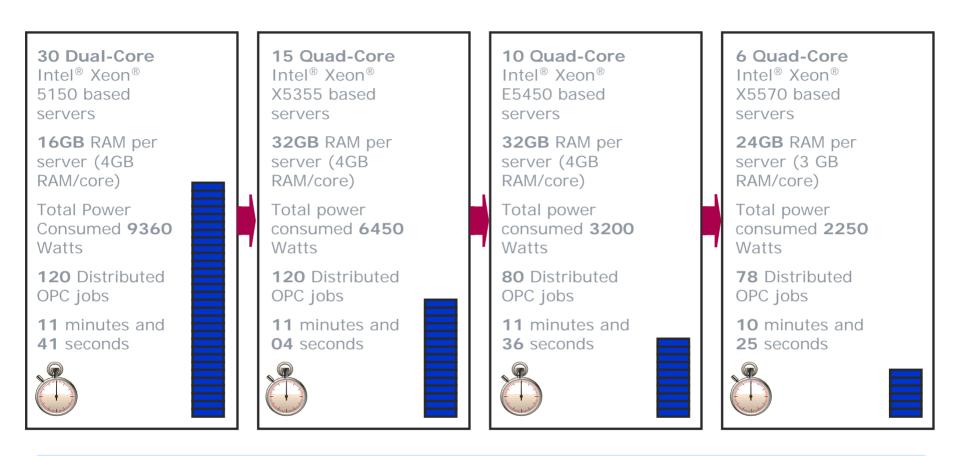

#### Intel Xeon processor 5500 series offers Higher Density, Superior Performance, and Lower Power for OPC

Intel quad-core server solution shows OPC throughput advantages

#### Profile: Intel<sup>®</sup> Xeon<sup>®</sup> Processor 5500 Series

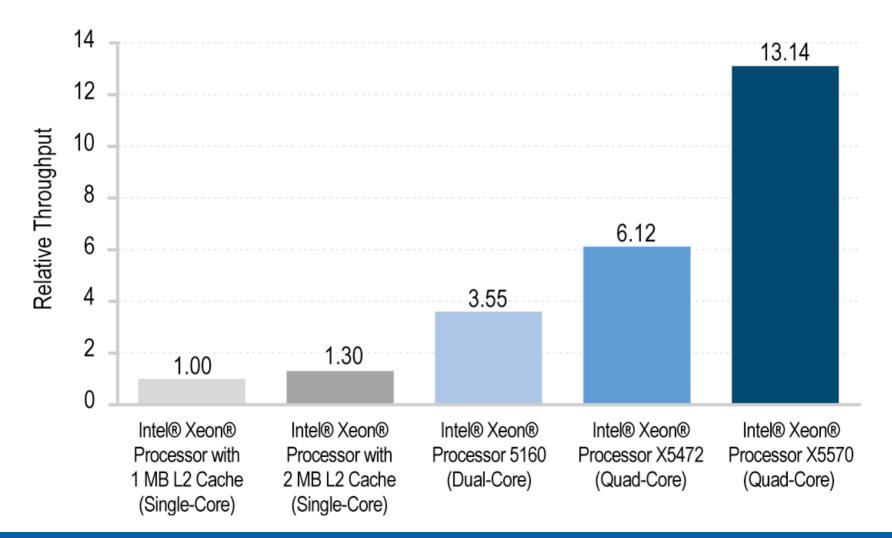

- Up to 13.14x improved performance over single-core processors for simulation workloads

- Up to 11.39x improved performance over single-core processors for OPC workloads

- Up to 13:1 server consolidation ratio for simulation workloads and 11:1 for OPC workloads

| IT@Intel Brief                                                                                                                                                                                                                     | Improving E<br>Performanc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                           | ch Application                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| Intel Weinh processor 3500<br>weies has demonstrand<br>a sobotential genationene<br>multiple when compand<br>to prinz generation innel<br>qualitation processors in<br>high-performance computing<br>applications.<br>Or Howard to | <ul> <li>Topher Humphportan - Searchettere</li> <li>Testere of process in searce to each of the searce of</li></ul> | epidous running<br>har and scape a<br>last toos on 1995,<br>ipaxes performance<br>effects and the Pesta<br>at 2000 and the Pesta<br>at 2000 as the too<br>exercises and scale<br>is a Work as the run<br>running of the<br>exercise and scale<br>in the run scale sources<br>of the exercise at a<br>last sector at a<br>last sector at a | dales of the one involved a lost versions as a super-             |

| Project 1. Service's based on link                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Piquing 2. Services                                                                                                                                                                                                                                                                                                                       | Arthlector Performance Improve ent<br>bot provide estimation      |

| series argeneed Synopsys VCS<br>for simulation,"                                                                                                                                                                                   | a bhacannan baugalarauca                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                           | propsys Protous* application parloneerce –<br>ty conscion (OPC).' |

IT@Intel

## Intel<sup>®</sup> Architecture Performance Improvement for Simulation

Intel internal measurements May 2007, November 2007, and February 2009.

# Runtime Performance for Simulation Application

| Processor                                                  | Simultaneous<br>Simulation Jobs | Runtime<br>(HH:MM:SS) | Relative<br>Throughput |

|------------------------------------------------------------|---------------------------------|-----------------------|------------------------|

| 64-bit Intel® Xeon® Processor with 1 MB L2 Cache (3.6 GHz) | 2                               | 93:51:07              | 1.00                   |

| 64-bit Intel® Xeon® Processor with 2 MB L2 Cache (3.8 GHz) | 2                               | 72:23:11              | 1.30                   |

| Intel® Xeon® Processor 5160 (3.0 GHz)                      | 4                               | 26:26:16              | 3.55                   |

| Intel® Xeon® Processor X5472 (3.0 GHz)                     | 8                               | 15:20:01              | 6.12                   |

| Intel® Xeon® Processor X5570 (2.93 GHz) $^{\!\!\!\Delta}$  | 16                              | 07:08:36              | 13.14                  |

<sup>△</sup> Tests run on Intel Xeon Processor X5570 series had Intel® Hyper-Threading Technology and Intel® Turbo Boost Technology enabled.

Intel internal measurements May 2007, November 2007, and February 2009.

#### Mainstream Intel<sup>®</sup> Xeon<sup>®</sup> Processor 5500 Series Segments

|                                  | Basic               | Standard             | Advanced             |

|----------------------------------|---------------------|----------------------|----------------------|

| CPU Frequency                    | 2.0 GHz to 2.13 GHz | 2.26 GHz to 2.53 GHz | 2.66 GHz to 2.93 GHz |

| CPU Power                        | 80 W                | 80 W                 | 95 W                 |

| QPI                              | 4.8 GT/S            | 5.86 GT/S            | 6.4 GT/S             |

| CPU Cache Size                   | 4 MB                | 8 MB                 | 8 MB                 |

| Memory Speed                     | 800 MHz             | 800/1066 MHz         | 800/1066/1333 MHz    |

| Intel® Turbo Boost Technology    | No                  | Yes                  | Yes                  |

| Intel <sup>®</sup> HT Technology | No                  | Yes                  | Yes                  |

GT/S – Gigatransfers/Second; Intel® HT – Intel® Hyper-Threading Technology; QPI – Intel® QuickPath Interconnect

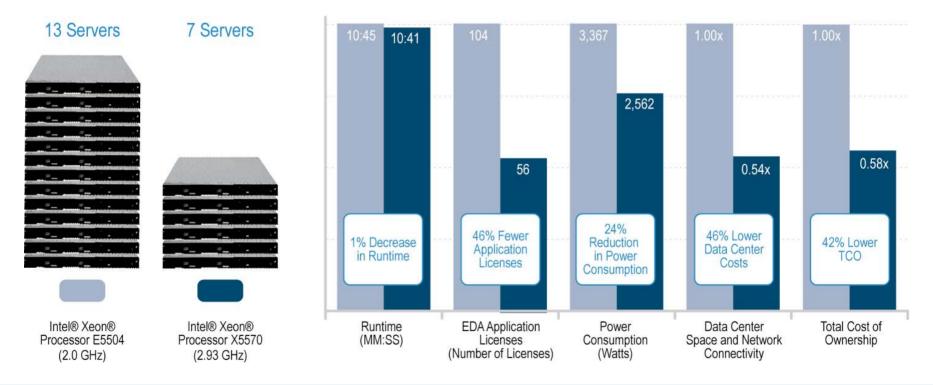

## EDA Throughput and Total Cost of Ownership

In tests with real Intel EDA workloads, we required fewer servers based on high-end processors to achieve the same performance. This resulted fewer EDA application licenses; reduced data center power, space, and connectivity requirements; and substantially lower estimated TCO.

Intel internal measurements, February 2009.

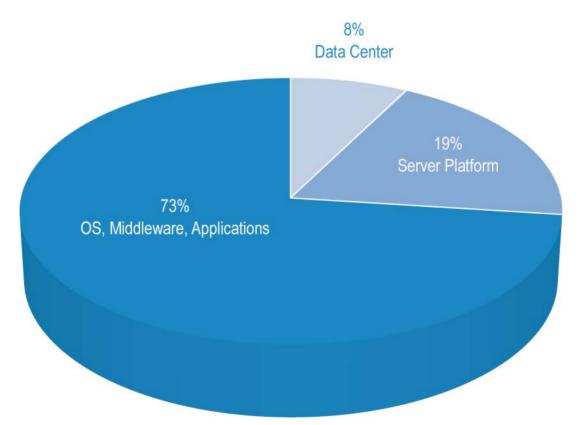

#### Server TCO

The hardware platform accounts for a small proportion of server total cost of ownership (TCO). TCO calculations based on Intel® Xeon® processor X5570 (2.93 GHz).

Intel internal measurements, February 2009.

#### Profile: Intel<sup>®</sup> Xeon<sup>®</sup> Processor 5500 Series

- High-end processors reduce server TCO by 42 percent compared to low-end processors

- High-end processors deliver up to 87 percent faster performance

#### IT@Intel Brief Intel Information Technology

with the introduction of

platforms, the benefits

5500 series-based

the intel<sup>®</sup> Xeon<sup>®</sup> processor

we are seeing from our IT strategy to standardize on

higher-end processors for

even more compelling and

- Dere Dryant

our servers nurchases is

results in a significantly

bewer TCO.

#### Selecting Server Processors to Reduce Total Cost

F.M. Dissemblisher matchief som fraka som 475-49. terts filled on second cost and a design on pringobservations when the loader. In testing and index shows they be benefited and block som noves stored of the considerable. The order of the fill have a same public of your more where performing participation operations, and self-fits. reduce planes to be reading to an interview. As we enti-

#### Profile: Intel<sup>®</sup> Xeon<sup>®</sup> Processor 5500 Series

- inherit niccessors voluce server TCO by 42 recent out valed to in literation processors.

- ligh-end processors deliver up to: 87 percent faster performance.

Georgian the help of history and war 4270025 to the off the letter hill. You to cover EARLING solution la comparigne comparis des comparis privaire et collopalisation example Photosophic reduction and interface value of examples for the 201 ally average and the same as function or an area inside. As a confluent the out for cars as As a minute for an answer and the index scalar education date she is the educed stress boostion ProvVVVVId a documentaria de la visional e Det visioname ferant van de Dynami name a log

Outana sisele ro strakstic late. En congener ta strae tes oper opsitial soft sar las positionar to usual odds which teached by the first which the fact which there are the start of the manufacture of the start of the s the state to be viewed prove of nieth concerning star acking on het such providents of the first state in the state of second state of the second state.

### HPC-1 to HPC-2 Storage Performance

#### HPC-2 Generation Limit: ~15K OPC jobs accessing one Parallel-Storage

| Category                   | Parallel-Storage-Gen1 | Parallel-Storage-Gen2     |

|----------------------------|-----------------------|---------------------------|

| Meta Data Server Load      | ~100%                 | ~80%                      |

| Interactive Latency        | Unacceptable          | Acceptable (no impact)    |

| Write (sec)                | 25.00                 | 4.00 (6.25x)              |

| Read (sec)                 | 25.00                 | 0.47 ( <mark>53x</mark> ) |

| File listing (sec)         | 17.00                 | 0.7 (24x)                 |

| File removal (sec)         | 25.00                 | 0.36 ( <mark>69x</mark> ) |

| Event: Storage Vol Offline | Yes                   | No                        |