# Proposta per uso di rivelatori a strip per il tracciatore di FOOT.

L. Servoli, G. Ambrosi, M.Biasini

Napoli, 25-26 maggio 2017

### Origin and Motivations

The work of this proposal has started after the last meeting of INFN CSN 3 in march, when it became clear the the Perugia group could no longer try to work on the pixel solution for the FOOT tracker and vertex.

Scientific motivations lies in proposing a solution for the Inner Tracker that could overcome some of the problems that the pixel solution would face.

1) To reduce multiple scattering we need to reduce silicon thickness at least to 50  $\mu m$  level.

$\rightarrow$  this has already been done by several groups (ILC, UFSD)

Moser H. G. et al., Thinned Silicon Detectors, POS (Vertex 2007) 013

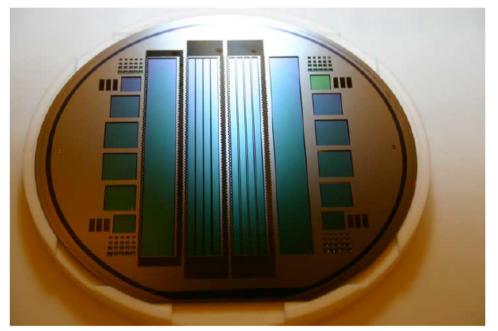

10.0 x 1.3 cm<sup>2</sup>

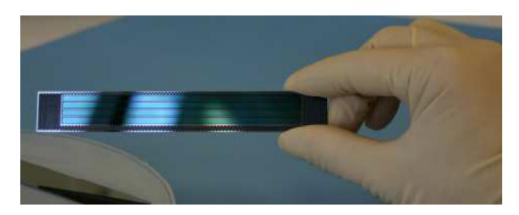

**Figure 2:** Photograph of the backside of a 6" SOI wafer with areas thinned to  $50\mu m$ . The large areas in the center correspond to ILC like modules,  $(10cm \times 1.3cm)$ , with and without reinforcement strips. The small structures in the periphery are test diodes.

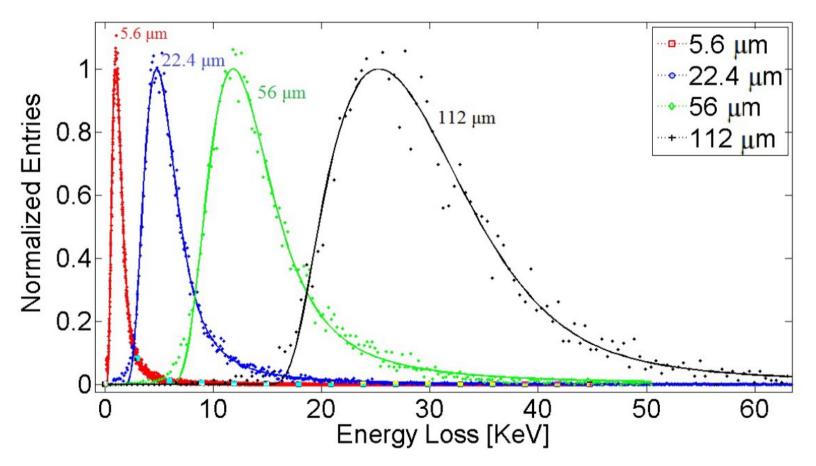

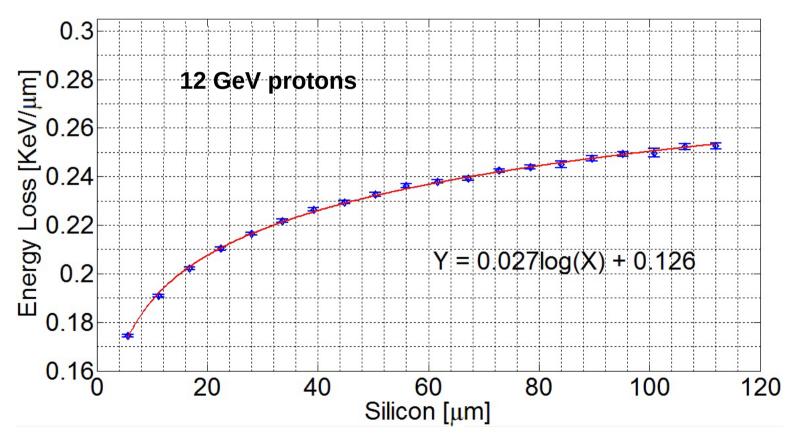

#### Thinning $\rightarrow$ signal reduction, more than proportionally below 100 $\mu m$

L. Servoli et al.: Energy loss measurement for charged particles in very thin silicon layers. Journ. of Instr. 6 P06013 (2011) 001-011

#### For 12 GeV protons @ 50 $\mu$ m thickness we have: MPV = 63 e-h / $\mu$ m $\rightarrow$ 3150 e-h pairs (noise > 1000 electrons)

L. Servoli et al.: Energy loss measurement for charged particles in very thin silicon layers. Journ. of Instr. 6 P06013 (2011) 001-011

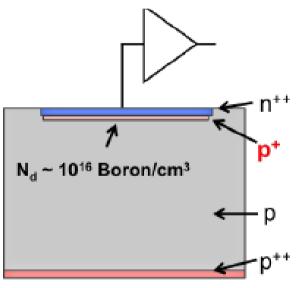

### How to recover signal, hence S/N? → Signal amplification on strip LGAD:

$E \sim 300 \,\text{kV/cm}.$

Low gain avalanche detectors

Fig. 1. Bias dependence of the leakage current and the signal gain for a 45  $\mu$ m-thick UFSD sensor with an area of 1.7 mm<sup>2</sup>. The gain determination is subject to an overall scale uncertainty of 20%. The similar exponential behaviour of gain and sensor current below 200 V bias is due to the common charge multiplication mechanism.

**Radiation damage**:  $10^{14} n_{eq}/cm^2$  without loss of performance.

R. Arcidiaconoi et al.: **Test of UFSD Silicon Detectors for the TOTEM Upgrade Project**, arXiv:1702.05180 [physics.ins-det] 16 feb. 2017

#### Are already there thinned LGADs?

# Yes. There is a batch in production at FBK, 50 $\mu$ m thin to be delivered to N. Cartiglia group (Torino).

- We have already discussed with him and he confirmed that:

- thinning can be made in most of the 6" wafer area (9.5x9.5 cm<sup>2</sup> at maximum), excluding external regions, to be left thick for mechanical reasons.

- 2) he is willing to cooperate in an investigation on the suitability of such devices for proton and ion detection.

- 3) we could have some of the prototypes now in production to start some testing in summer.

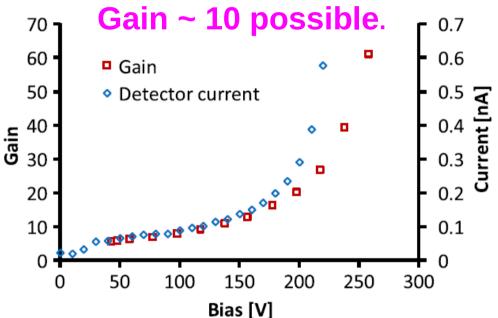

### Mechanical setup

- $\rightarrow$  Readout outside the beam region.

- → Reduction of dead space

Each silicon layer thinned to thickness: 50 micrometers ;

Two layers glued via biadhesive kapton foil, 30 micrometer thickness;

Total thickness: 115 micrometer silicon equivalent.

It could be even less if thinner silicon (25 micrometers) could be machined and used.

Support ring (aluminum? steel?) larger than the beam spot;

→ sensor area with uniform density and thicknes

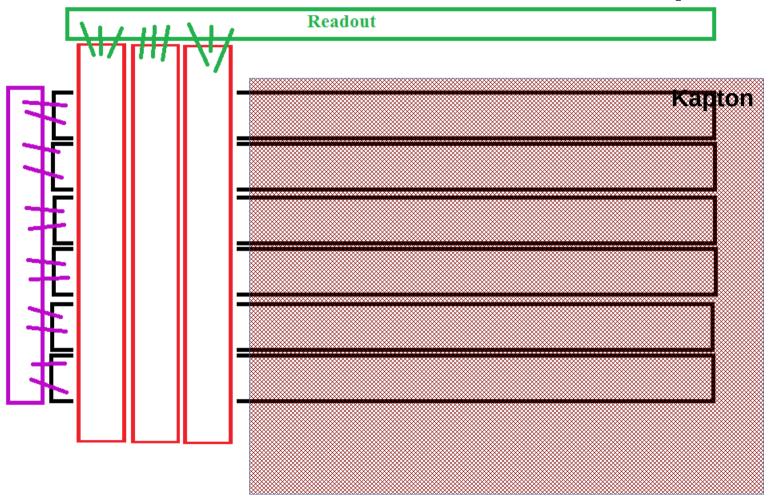

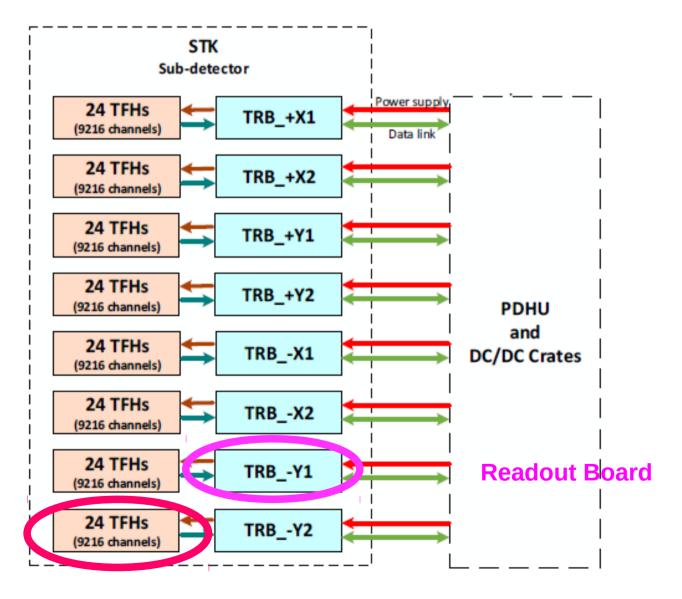

### How many readout channels?

To obtain spatial resolution < 30  $\mu$ m  $\rightarrow$  125  $\mu$ m strip pitch, analog readout. **(AMS).**

- $\rightarrow$  8 x 8 cm<sup>2</sup> instrumented area  $\rightarrow$  80000  $\mu$ m /125  $\mu$ m = 640 strips per coordinate.

- $\rightarrow$  1 DAMPE readout chip: 64 channels => 10 chips per coordinate.

- $\rightarrow$  we need two planes with both coordinates,  $\rightarrow$  40 chips + 10 chips spare.

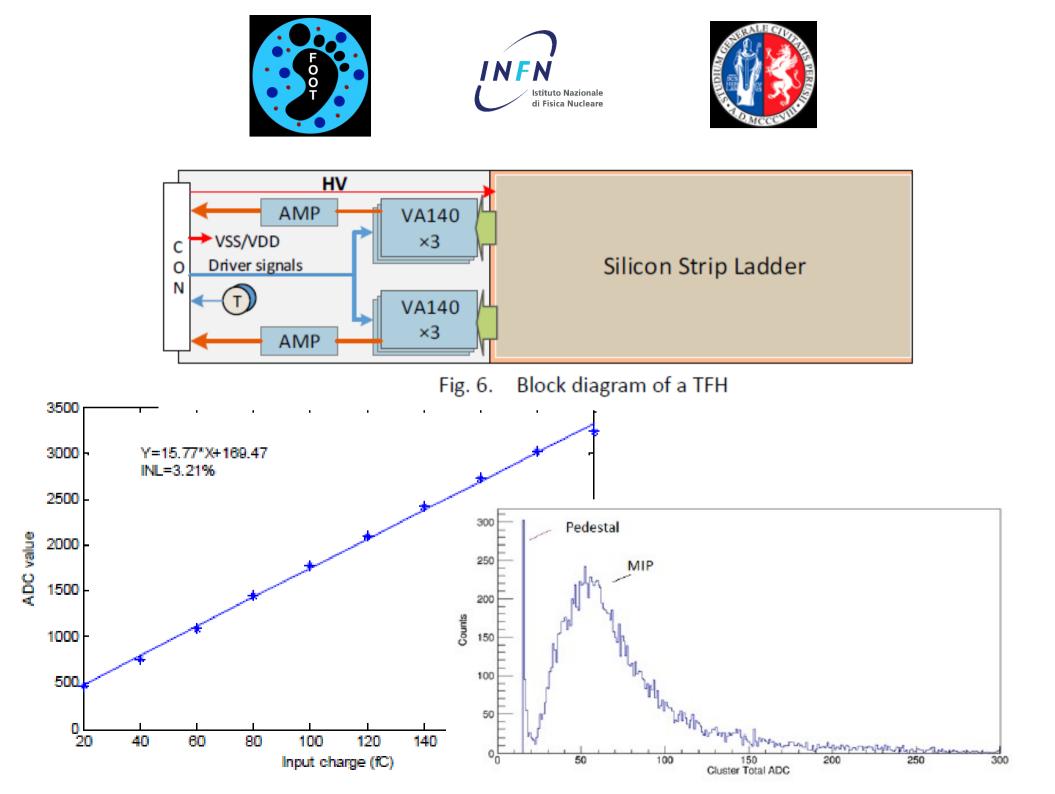

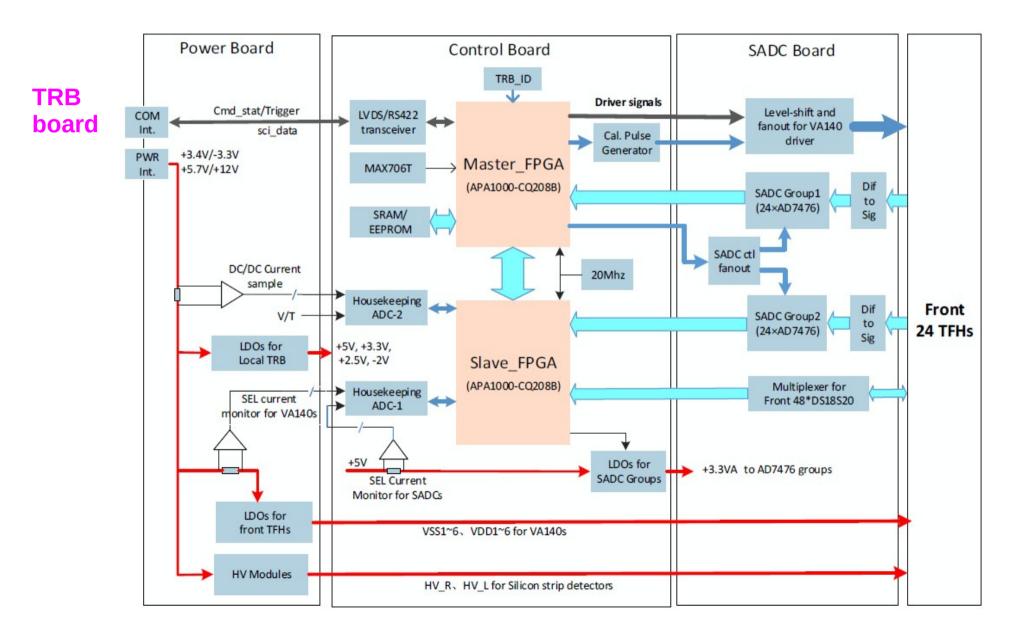

- → Hybrid for front-end chip (TFH): hosts readout chips + bias + services. (essentially same design of DAMPE hybrids)

- → Readout board (TBR) to host connection with computers and links to/from Hybrids

**Baseline: the DAMPE front-end – hybrid – readout board chain.**

## Reuse as much as possible:

# DAQ chain based on DAMPE chain.

Preams: +- 200 fC

Hybrid with readout chip

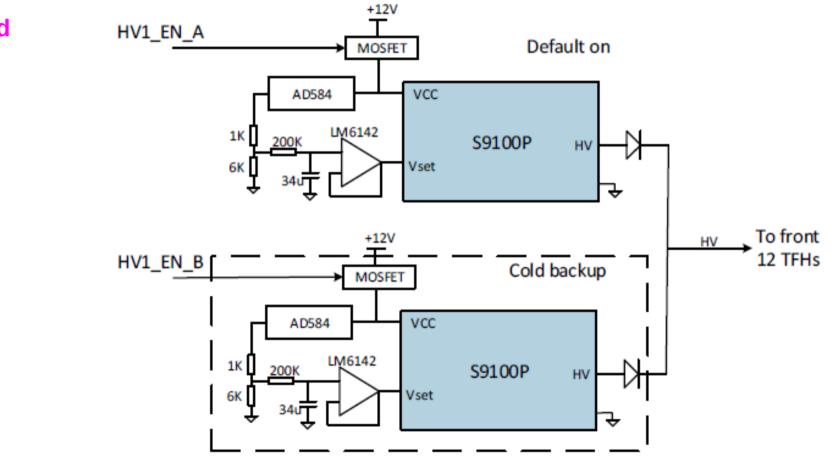

Fig. 8. Circuit for a HV-generator group

HV board

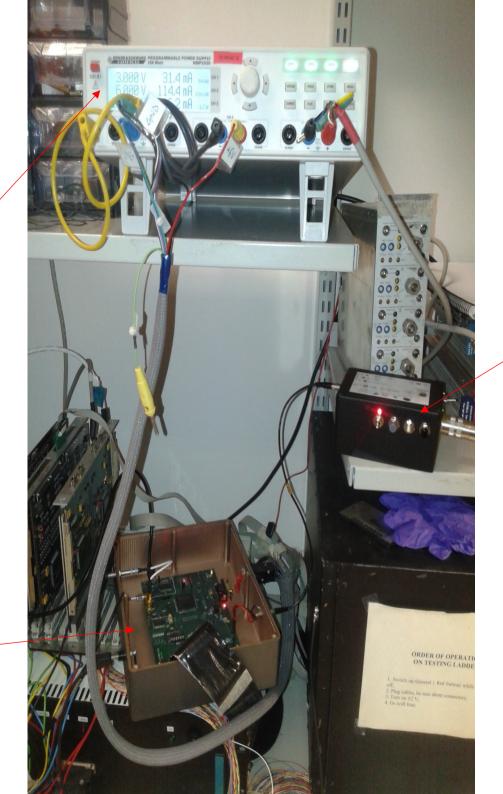

Laboratory Setup for Dampe Ladder Test

ROHDE&SCHWARZ Programmable Power Supply HMO2030

**BIAS Box**

Some rough computation on dinamic range and Signal.....

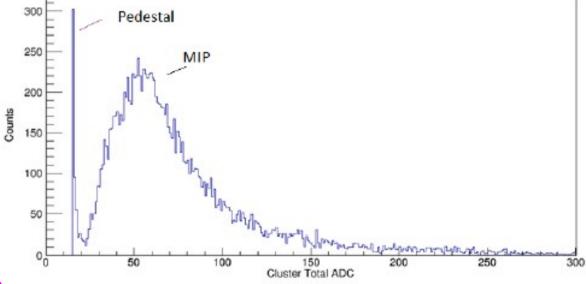

50 ADC / MIP (@300 μm)

- $\rightarrow$  8.3 ADC /MIP (@ 50  $\mu m)$

- $\rightarrow$  83 ADC / MIP (@ 50  $\mu m$  with LGAD = 10)

→ 1 FBK run = 80 k€ (12-15 wafers). If MPW, our costs decrease.

In each wafer we could reserve 3 sensor  $8 \times 1$  or 2 sensor  $8 \times 2 \text{ cm}^2$  to have 36-46 sensor  $8 \times 1 \text{ cm}^2$  or 24-30 sensor  $8 \times 2 \text{ cm}^2$ . In first hypothesys we do need 32 sensors + spares, and we will use about 30% of wafer. (24 k€) In second hypothesys we do need 16 sensors and we use 40% of wafer. (32 k€) Costs should decrease proportionally.

- → jig development to handle and mount sensors + kapton (5 10 k $\in$ )

- → each readout chip costs 300  $\in$  → 15 k $\in$  (50 chips)

- → hybrid front end → 500 € /piece → 5 k€ (8 + 2 spare);

- → Readout board (ADC +, digital communication) :  $5 \text{ k} \in$ ;

Hence, total costs: 54 - 67 k€;

Next steps in 2017:

- 1) Refine idea and get all the relevant information, mainly on mechanical stability.

- 2) obtain test devices from N. Cartiglia and bond to available DAMPE readout.

- 3) test in laboratory and also at beam test (November @ CERN) and in a proton and ion beam.

- 4) mechanical test of thinned layer of silicon glued to biadhesive kapton foil.