#### Electronics, Trigger and Data Acquisition part 1

#### Summer Student Programme 2017, CERN

July 5, 2017

Roberto Ferrari Instituto Nazionale di Fisica Nucleare

roberto.ferrari@pv.infn.it

## Introduction

- Lectures will be concerned with Data Acquisition (DAQ) in High-Energy Physics ...

- Data acquisition is an alchemy of electronics, computer science, networking, physics

- ..., resources and manpower matter as well, ...

- Topics are pretty much correlated  $\rightarrow$  you will realise this in the lecture non-linearity

Credits: material and ideas come largely from my predecessor (Wainer Vandelli) and from the lectures of ISOTDAQ schools (http://isotdaq.web.cern.ch/isotdaq/isotdaq/Home.html)

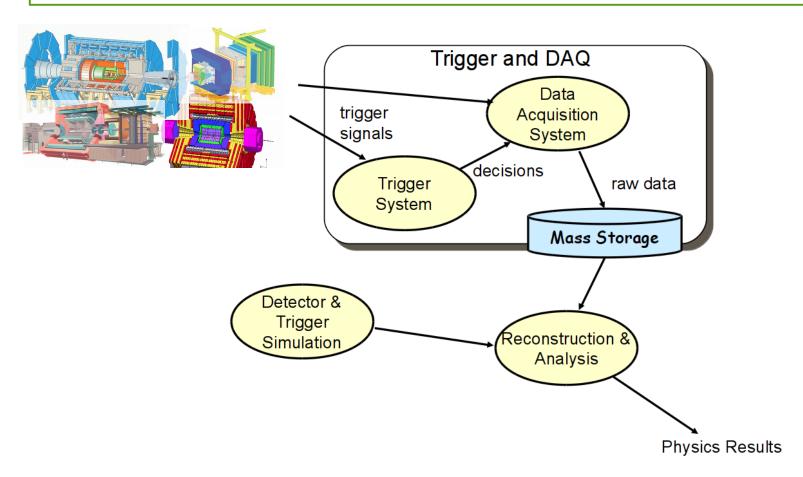

## **General** Overview

• main role of Electronics, Trigger & DAQ is to process signals generated in "a detector", likely storing all useful information in some safe place

# Signals ?

- Sometimes, somewhere in our detector, something ("one event") happens,

i.e. in some short time several particles interact within it.

- In High-Energy Physics, even a single event is composed by sequences of many different probabilistic (quantum-mechanics) processes → fluctuations are built-in

- At the end, "electrical" signals arrive at detector output terminals.

Different signals:

- a) have different characteristics (size, arrival time, duration, ...)

- b) carry different, (likely) independent, information

- c) need quite some electronics in order to become "profitable"

#### Electronics

#### [Horowitz & Hill, The Art of Electronics]

# Role?

- Sense, transform and collect electrical signals from detector(s) very often short current/light pulses (i.e. bunches of electrons or photons)

– you may be interested in total charge or in signal time or in both

- Adapt signals to optimize different, **conflicting**, characteristics  $\rightarrow$  <u>balance</u>:

- minimum detectable signal (min. noise and max. signal-to-noise ratio)

- maximum detectable signal (dynamic range)

- speed (signal rate)

- timing

- pulse shape dependence

- Digitize and preserve information

- allow for subsequent processing, transmission, storage using digital electronics

- $\rightarrow$  computers, networks, ...

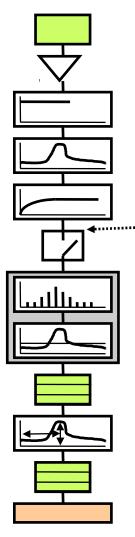

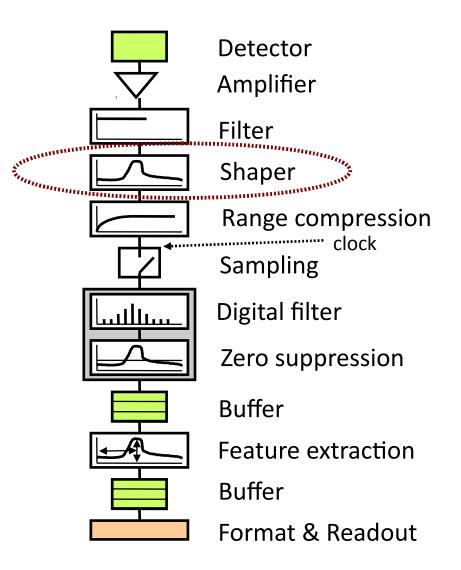

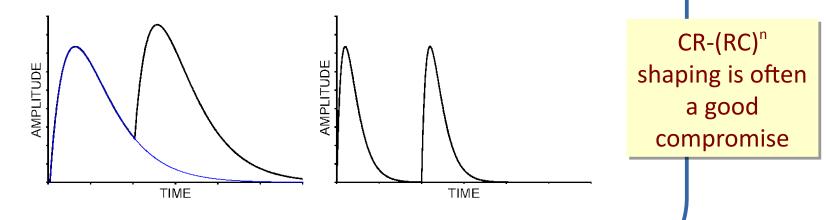

# Read-Out Chain

Detector Amplifier Filter

Shaper

Range compression clock Sampling

Digital filter

Zero suppression

Buffer

Feature extraction

Buffer

Format & Readout

- Front-end electronics very specialized

- custom-built to match detector characteristics

- Cannot discuss all design and architecture details

- if you are into electronic design you already know more than me

- Find yourself dealing or choosing commercial electronics

- provide you with base guidelines

- Selected functions and principles

#### **Read-Out** Chain

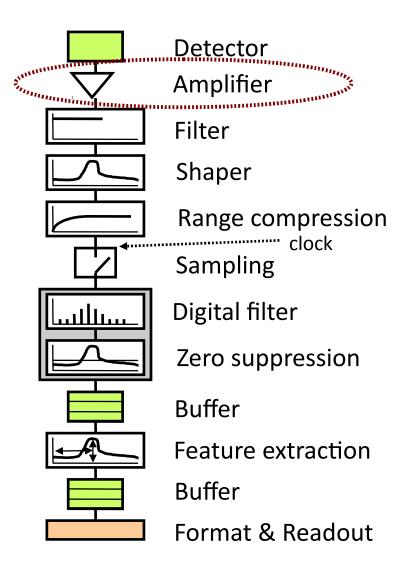

# Amplifiers

**Amplifier:** powered black box connected that receives an input signal with power  $P_0$  and produces an output signal with amplified power  $P_1$

**Open loop gain:**  $k = P_1 / P_0$  (usually very large)

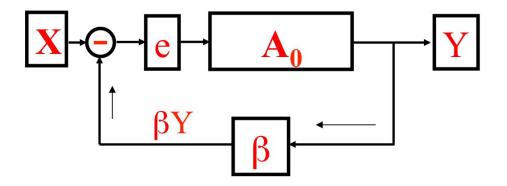

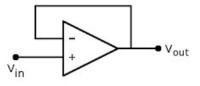

## Negative Feedback

Part of the output signal Y is sent back to cancel some of the input:

$$Y = A_0 e = A_0 (X - \beta Y) \rightarrow Y (1 + A_0 \beta) = A_0 X$$

$$Y = \frac{A_0}{1 + \beta A_0} X$$

If  $A_0 >> 1 \rightarrow Y = X/\beta$  $\rightarrow$  stable and controlled gain (1/ $\beta$ )

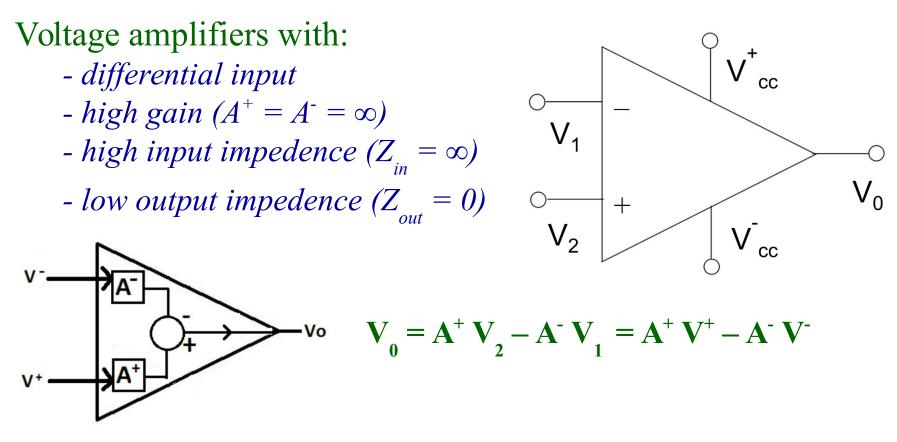

# **Operational Amplifiers**

The output voltage V0 is the sum of:

- the signal at the inverting input (-),  $V_1$ , inverted and amplified by  $A^-$

- the signal at the non-inverting input (+),  $V_2$ , non-inverted and amplified by  $A^+$

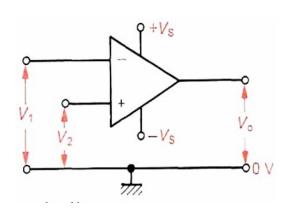

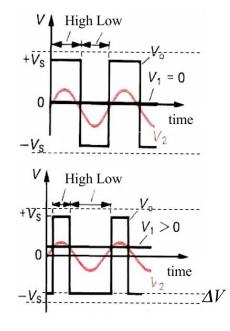

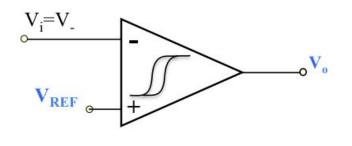

# Open-loop Configuration: Comparator

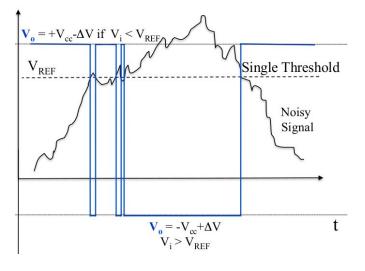

# Positive Feedback $\rightarrow$ Schmitt Trigger

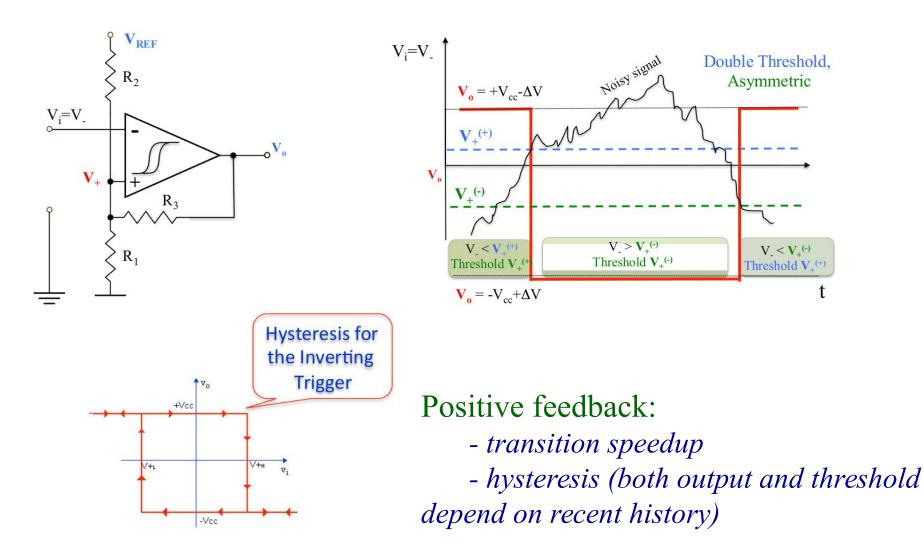

# Negative Feedback ...

Golden rules:

- 1) output keeps zero voltage difference between inputs

- 2) inputs draw no current

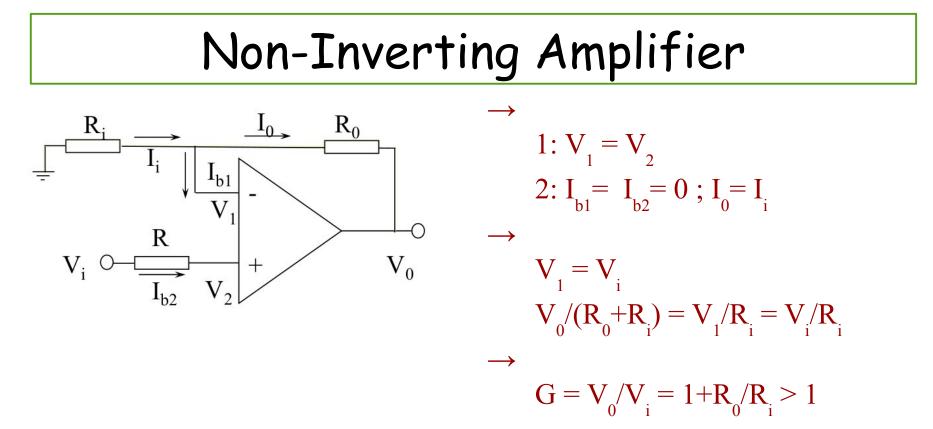

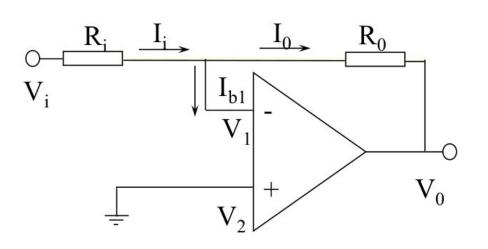

# Inverting Amplifier

$$\rightarrow 1: V_1 = V_2$$

$$2: I_{b1} = I_{b2} = 0; I_0 = I_1$$

$$\rightarrow V_1 = 0$$

$$V_0/R_0 = -V_1/R_1$$

$$\rightarrow G = V_0/V_1 = -R_0/R_1$$

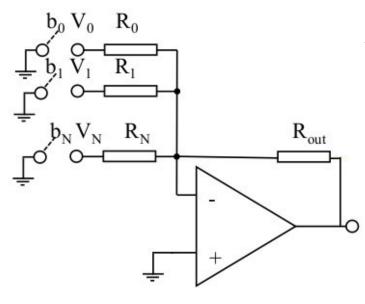

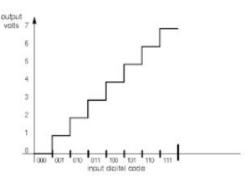

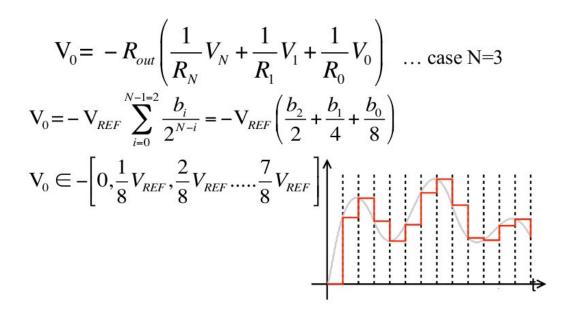

#### Inverting Amplifier $\rightarrow$ Current Adder $\rightarrow$ DAC

If  $V_N = 0$ , then  $R_N$  is short-circuited (bit at 0) Set  $R_{out} = R_0$ ,  $R_1 = 2R_0$ ,  $R_2 = 4R_0$ , etc. etc.

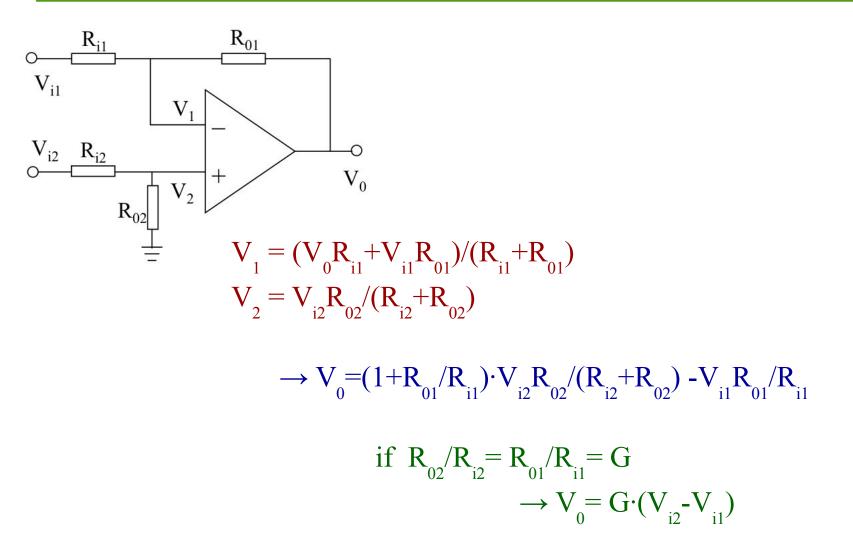

#### **Differential Amplifier**

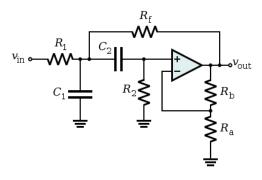

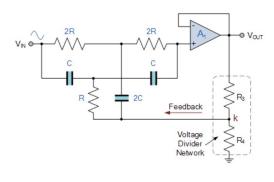

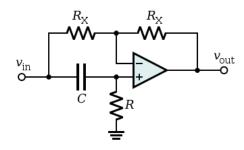

# Some Magics ...

Band-pass Filter

Band-stop Filter

Phase Shifter

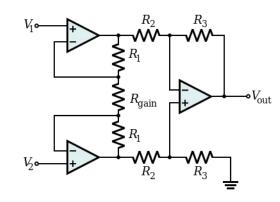

Instrumentation Amplifier (High CMRR amplifier)

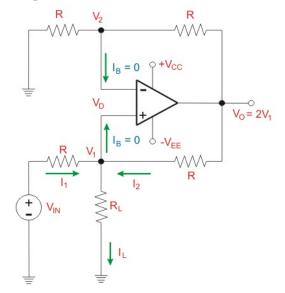

#### Voltage-to-Current Converter

Buffer!

and billions of others ...

# Back to signals: what can a signal be ?

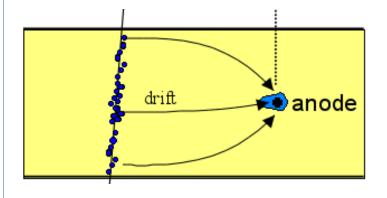

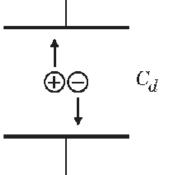

- Detectors may be electrically represented as a capacitor (Cd)

- more realistic schemes will include other contributions

- Interactions of passing particle  $\rightarrow$  energy release E  $\rightarrow$  short current pulse i<sub>s</sub>

$$E \bigotimes Q_s = \int i_s(t) dt$$

Pulse duration may range from O(100 ps) up to O(10 μs)

DETECTOR

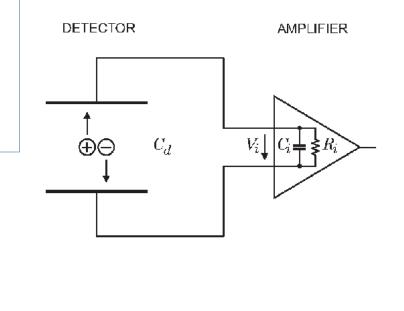

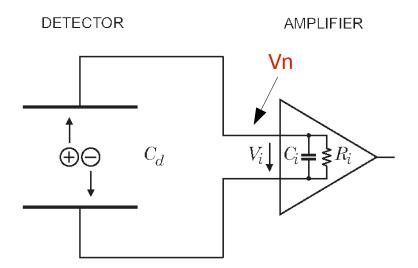

# Voltage-Sensitive Amplifier

- Signals are possibly very small, amplify to:

- improve signal resolution, adapt it to next stages

- avoid SNR degradation ...

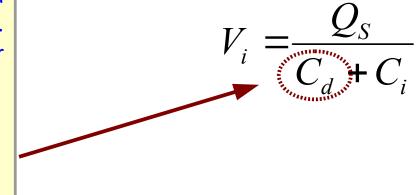

Using a simple voltage amplifier, the sensed **input voltage V**<sub>i</sub> **depends on the detector capacitance.**

Detector capacitance could be a function of the operation point (e.g. high voltage) and/or detector dimension.

Additional **calibration** efforts

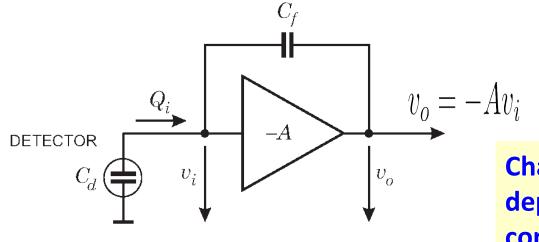

#### Charge-Sensitive Amplifier

Charge amplification only depends on a well-controlled component

Effective (dynamic) C input capacitance:

$$C_i = \frac{Q_i}{v_i} = C_f (A+1)$$

**Gain:**

$$A_Q = \frac{v_o}{Q_i} = \frac{Av_i}{C_f(A+1)v_i} = \frac{A}{A+1}\frac{1}{C_f} \approx \frac{1}{C_f} (A \gg 1)$$

# Charge Transfer

$$C_i = \frac{Q_i}{v_i} = C_f (A+1)$$

What total-charge fraction is measured ?

$$\frac{Q_i}{Q_s} = \frac{C_i v_i}{Q_{det} + Q_i} = \frac{C_i}{Q_s} \cdot \frac{Q_s}{C_i + C_{det}} = \frac{1}{1 + \frac{C_{det}}{C_i}} \approx 1 \text{ (if } C_i >> C_{det} \text{)}$$

Need large input capacitance to maximize charge transfer

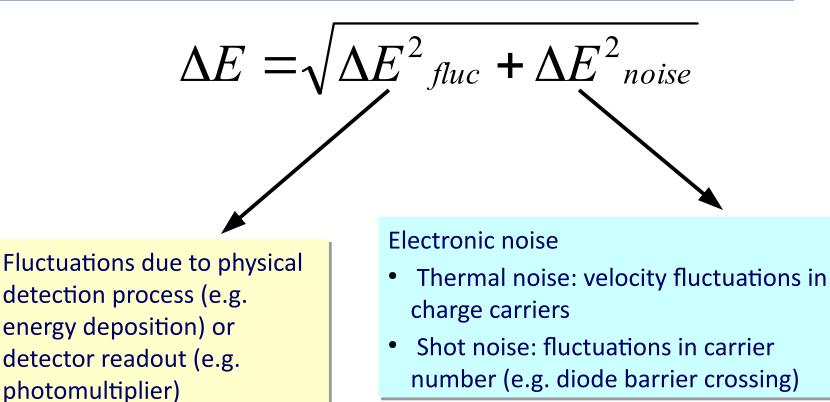

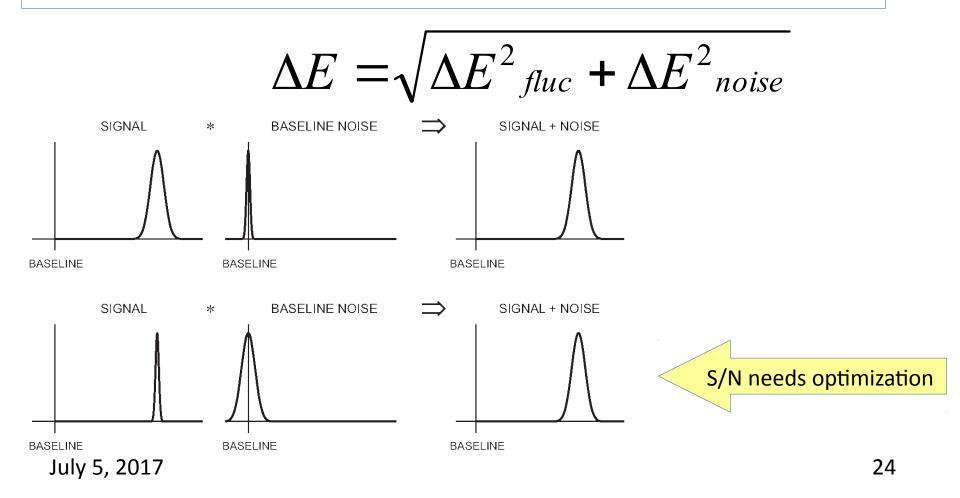

# Signal-to-Noise Ratio (SNR)

- Improving SNR improves sensitivity (minimum detectable signal)

- Electronic noise does not necessarily dominate each measurement

# Signal-to-Noise Ratio (SNR)

- Improving SNR improves sensitivity (minimum detectable signal)

- Electronic noise does not necessarily dominate each measurement

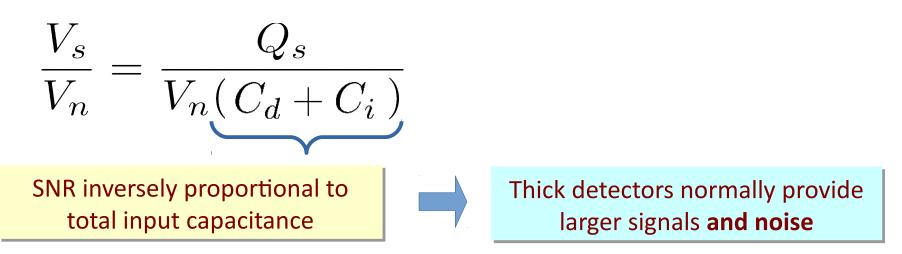

#### SNR .vs. Detector Capacitance

$\rightarrow$  given signal charge Qs

$$V_s = \frac{Qs}{C_d + C_i}$$

$\rightarrow$  assuming input noise Vn

# **Read-Out** Chain

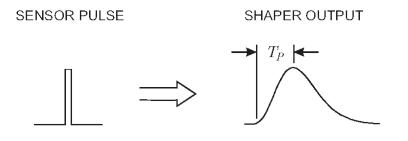

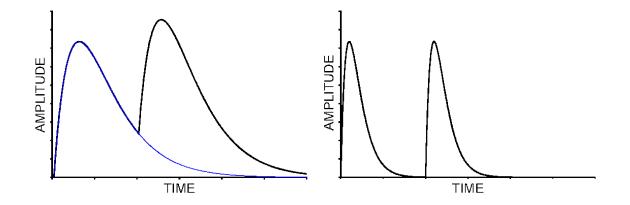

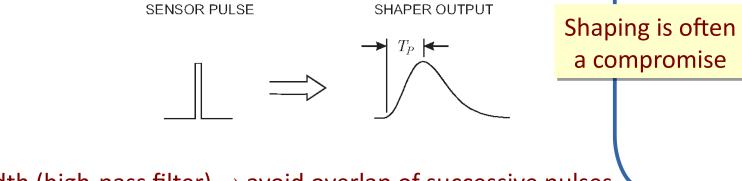

# Pulse Shaping

- Reduce signal bandwidth (low-pass filter)  $\rightarrow$  improve SNR

- fast rising signals have large bandwidth

- shaper broadens signals

- Limit pulse width (high-pass filter) → avoid overlap of successive pulses

- increase maximum signal rate at the cost of more noise

# Pulse Shaping

- Reduce signal bandwidth (low-pass filter)  $\rightarrow$  improve SNR

- fast rising signals have large bandwidth

- shaper broadens signals

- Limit pulse width (high-pass filter) → avoid overlap of successive pulses

- increase maximum signal rate at the cost of more noise

# **Read-Out Chain**

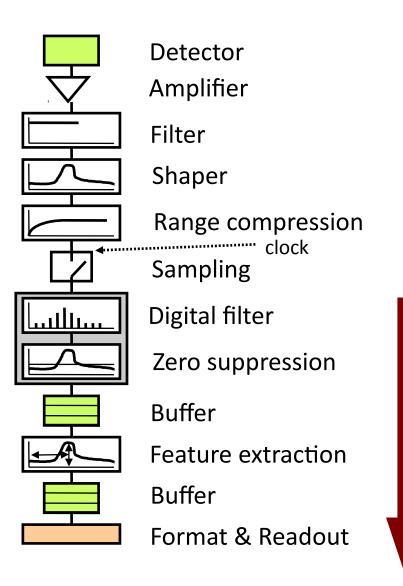

# Analog-to-Digital Conversion Introduction

Digitization → encode analog information into a numerical (discrete) format Why ? Much easier to handle and preserve Which format ? Usually binary, sometimes BCD

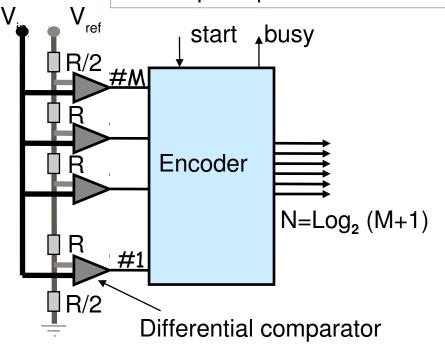

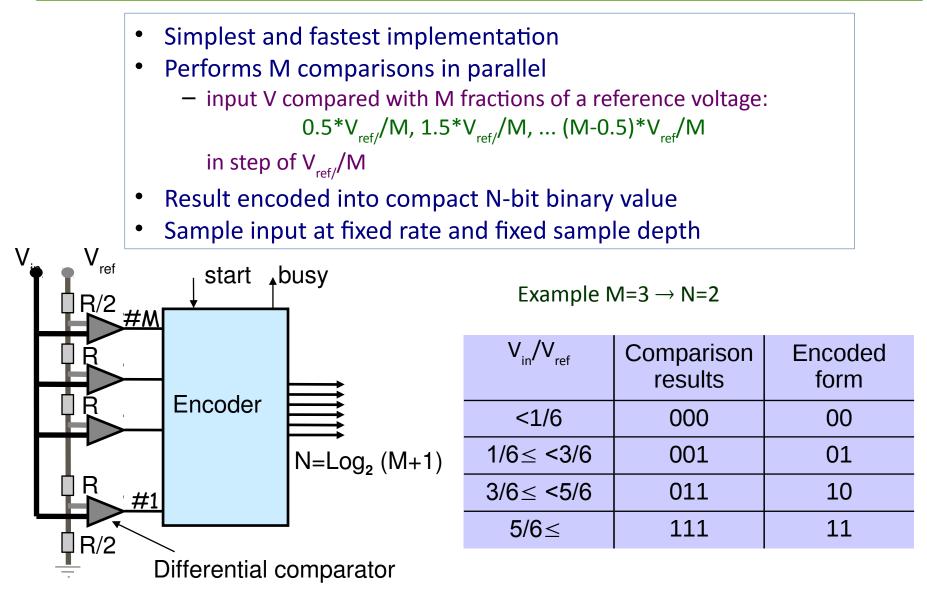

# Flash ADC

- Simplest and fastest implementation

- Performs M comparisons in parallel

- input V compared with M fractions of a reference voltage:

in step of  $V_{ref}/M$

- Result encoded into compact N-bit binary value

- Sample input at fixed rate and fixed sample depth

- Simple ? Yes

- Fast ? Yes

- Could be non-linear ? Yes

- Cheap ? Oopss ...

# Flash ADC

# ADC Characteristics

Digitization  $\rightarrow$  encode analog information into a numerical (discrete) format

| Entity to be measured |

|-----------------------|

|-----------------------|

Ruler unit

Compare entity ( $\rightarrow$  count) with a ruler

- Resolution (LSB), the ruler unit:  $V_{max}/2^{N}$

- 8bit,  $1V \rightarrow LSB=3.9mV$

- Quantization error: ±LSB/2

- Dynamic range: V<sub>max</sub>/LSB

- N for linear ADC

- >N for non-linear ADC; if logarithmic:

constant relative resolution on the valid input range

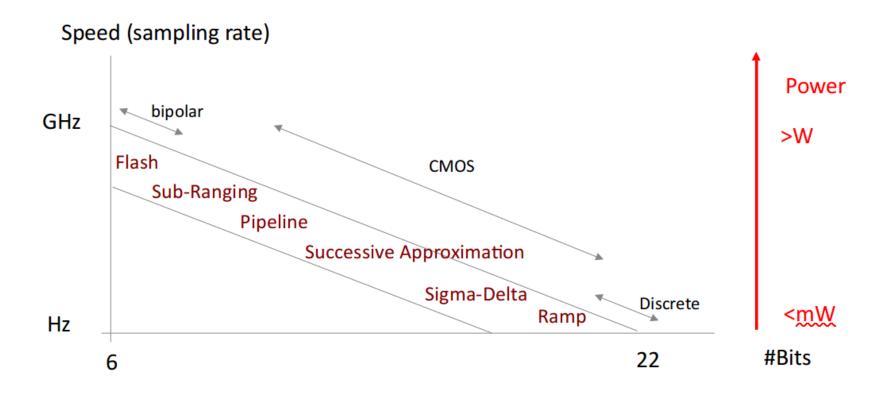

#### ADC Phase-Space

Many different ADC techniques exist, with different trade-offs between speed, resolution, power consumption, cost, ...

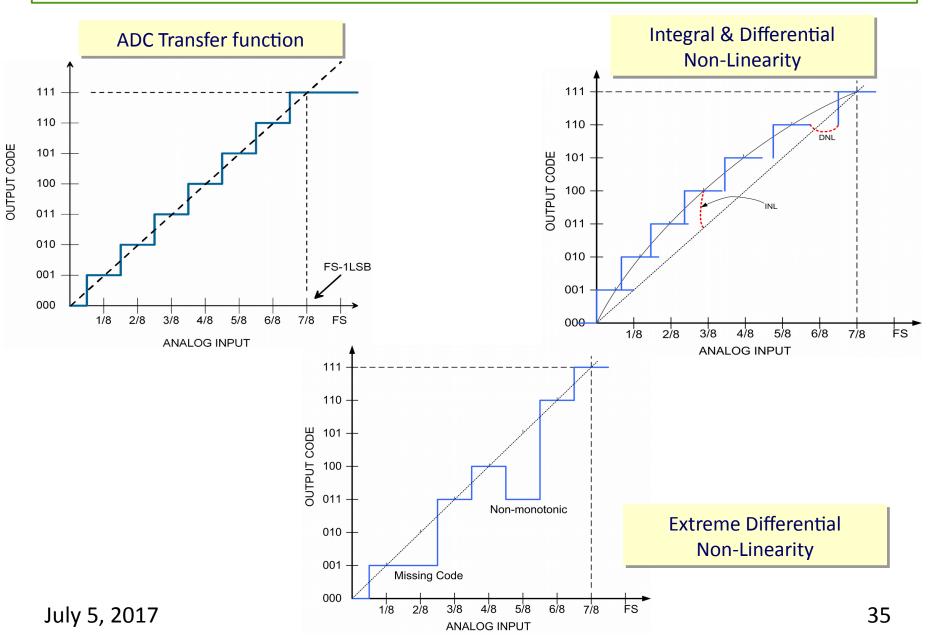

# ADC (In)Accuracies

# Real ADC.s at Work

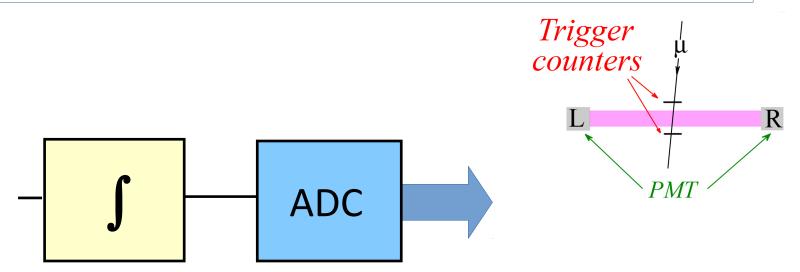

- Real data from a beam test @CERN

- PbWO<sub>4</sub> (scintillating) crystal equipped with two PMTs and exposed to e,  $\mu$  and  $\pi$  beams

- $QDC \rightarrow (gated)$  charge integrator followed by ADC

- $\rightarrow$  (fixed-duration) gate opened after trigger

- $\rightarrow$  digital conversion started after gate closing

- $\rightarrow$  integrator discharged after conversion

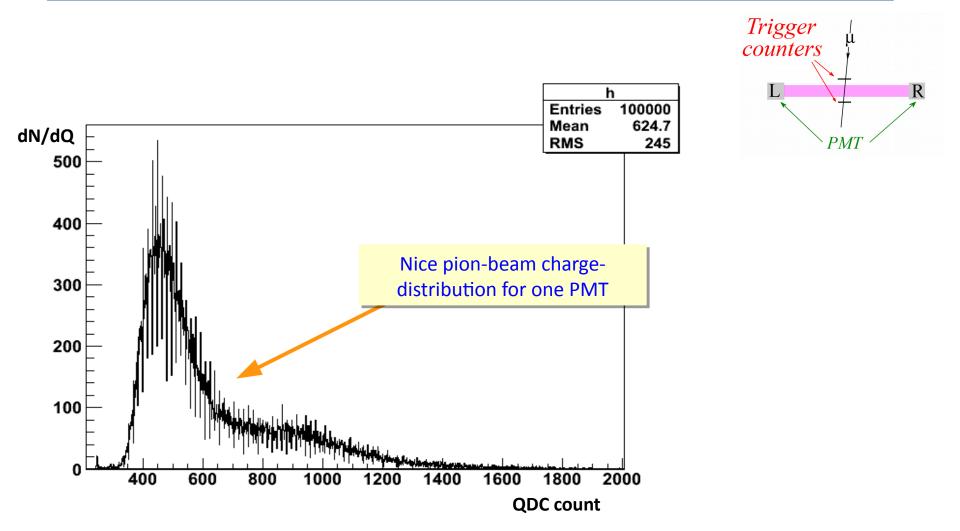

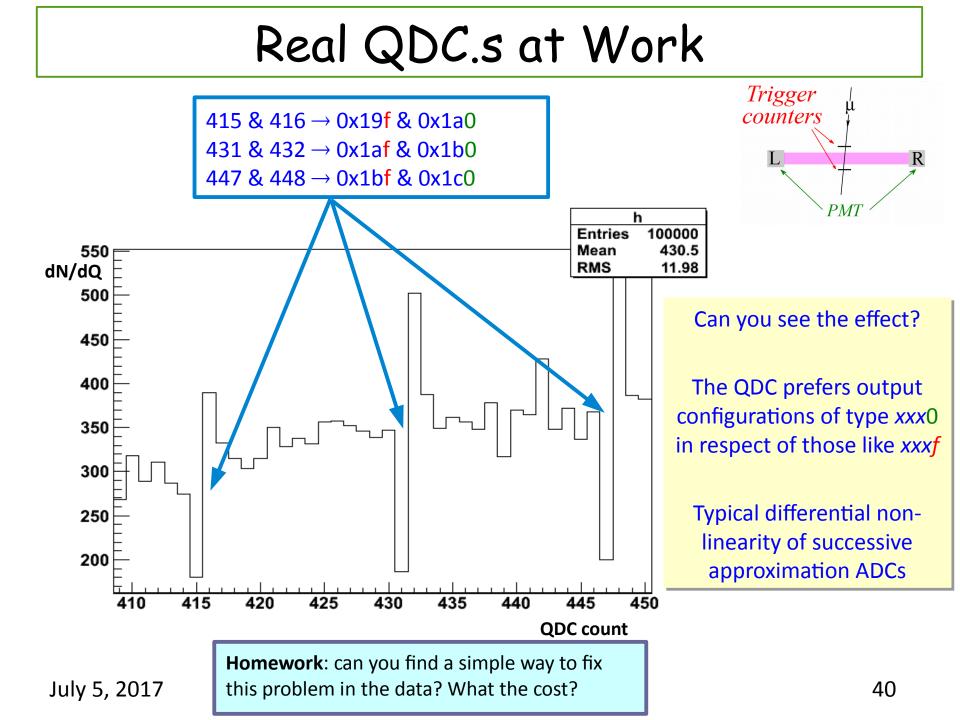

#### Real QDC.s at Work

PbWO<sub>4</sub> crystal equipped with two PMTs and exposed to e,  $\mu$  and  $\pi$  beams

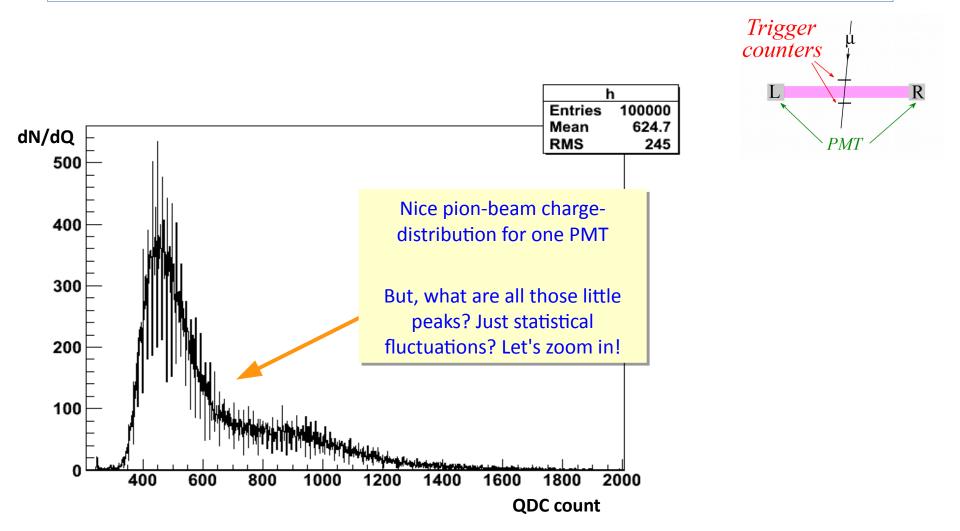

#### Real QDC.s at Work

PbWO<sub>4</sub> crystal equipped with two PMTs and exposed to e,  $\mu$  and  $\pi$  beams

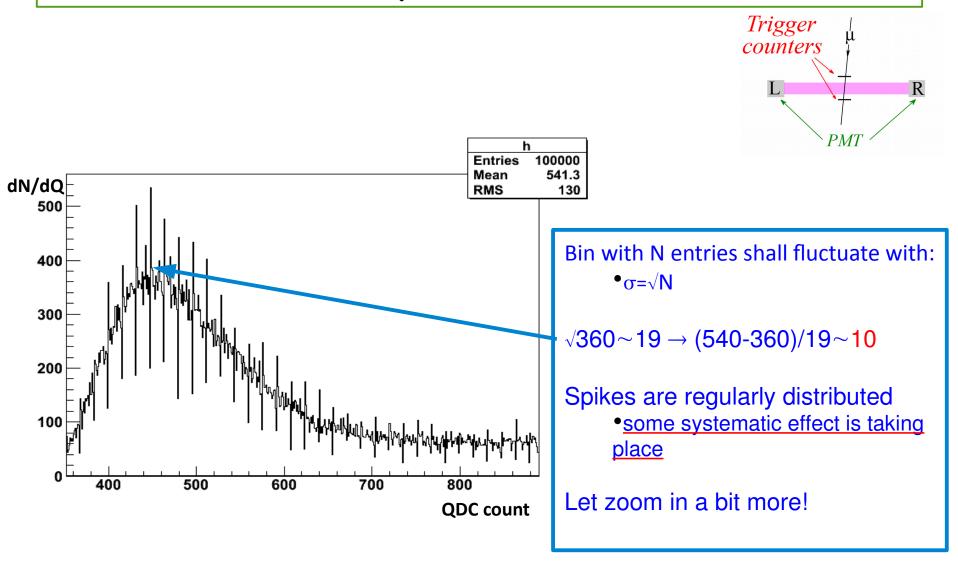

#### Real QDC.s at Work

# Some more ... Peak-Sensing ADC

- QDC signals need to be fully integrated, gate need not to be too long

→ need precise and stable timing .vs. gate:

- high-rate unipolar pulses may suffer of baseline drift

$\rightarrow$  to overcome such problems:

- 1) charge amplifier + shaper:

- signal shape stable

- peak value proportional to Q

- 2) peak-sensing ADC:

- find Vmax within a gate (rise-time shouldn't be too fast)

- at end-of-gate, convert

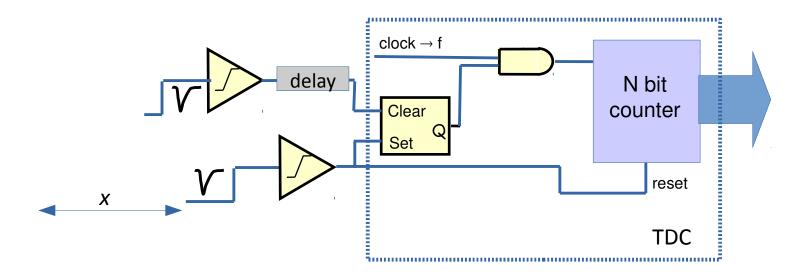

#### Time Measurements $\rightarrow$ TDC

- Time-to-Digital Converter

- Resolution: 1/f

- Dynamic range: N

- Single-hit TDC:

- e.g. noise spike arriving just before the signal → measure lost

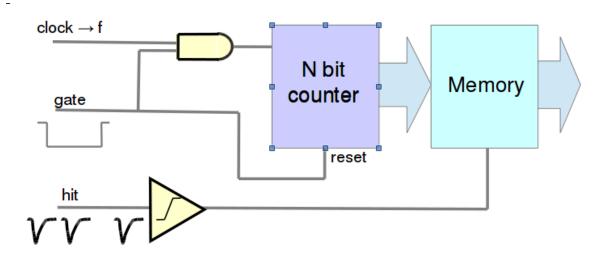

# Multi-Hit TDC

- Gate resets and starts counter. Also provides measurement period

- Gate duration < $\sim 2^{N}/f$

- Each "hit" (i.e. signal) forces memory (FIFO) to load current counter value, that's delay wrt. gate opening

- in order to distinguish hits belonging to different gates, some additional logic needed to tag data (end/start-of-gate marker)

- <u>Common-start configuration</u>

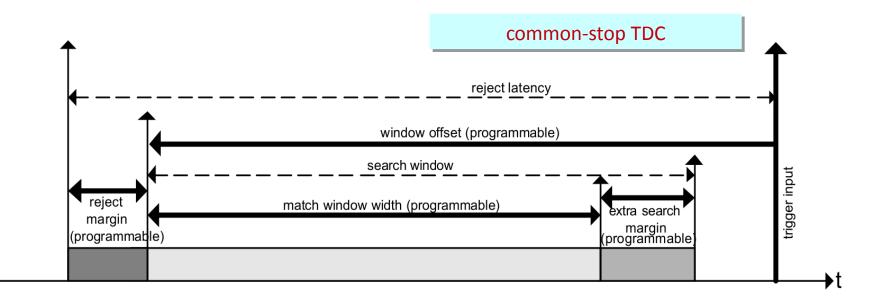

## Real TDC.s

- Real TDCs provide advanced functionalities for fine-tuning hit-trigger matching

- internal programmable delays

- internal generation of programmable gates

- programmable rejection frames

# Digital Converters - Summary

Speaking about measuring fast (short) pulses ...

- Flash ADC: high-speed sampling, measure V

- QDC: pulse integration, measure Q, pedestal\* proportional to gate length

- Peak Sensing ADC: measure V(peak)

- TDC: measure time intervals

- conversion (dead) time of commercial VME boards  $\sim$  few us

\*pedestal = measurement of input noise (absence of signal)

#### to be continued...