# Depleted CMOS chip design and test beam of the H35Demo chip

**Emanuele Cavallaro**, R Casanova, F Förster, S Grinstein, J Lange, C Puigdengoles, S Terzo

**30<sup>th</sup> RD50 Workshop** 5-7 June 2017

#### <u>Outline</u>

- Chip design

- LF ATLAS Pix

- LF2

- RD50 Chip

- H35Demo

- H35Demo Chip test beam

- Monolithic matrix readout

- Test beam measurements

- Results

- Conclusions

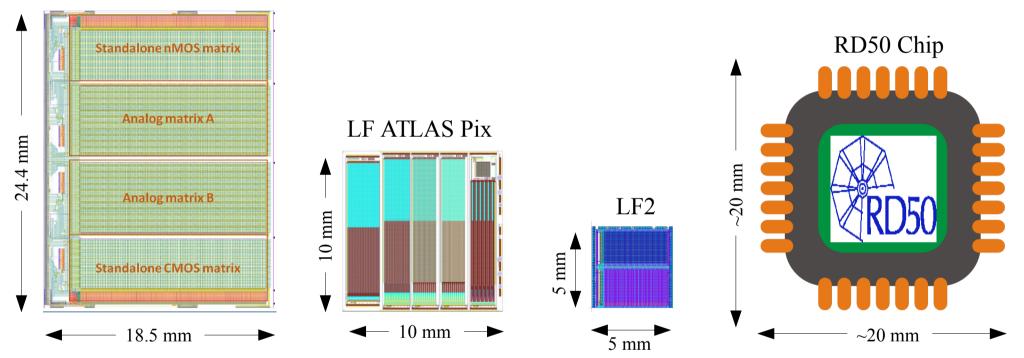

#### LF ATLAS Pix

- Technology: LFoundry 150nm HV-CMOS

- Resistivities: 100 Ωcm, 500 Ωcm,

1.1 kΩcm, 1.9 kΩcm and 3.8 kΩcm

- Designed by KIT, IFAE and University of Liverpool

- IFAE main contribution on the digital block

- Status: Received in February 2017

- Tests ongoing in KIT

- FEI3 like pixel matrix in  $50x50 \ \mu\text{m}^2$  pixel

- Technology: LFoundry 150nm HV-CMOS

- Resistivities: 500  $\Omega$ cm and 1.9 k $\Omega$ cm

- Designed by IFAE in collaboration with University of Liverpool

- Contributions from University of Geneve and KIT

- Status: Received in May 2017

- First tests ongoing

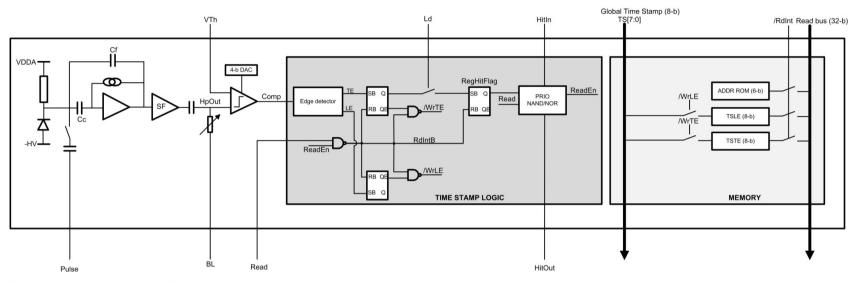

#### LF2 Readout a la FEI3

- Column-drain architecture

- Global 8-bit gray encoded time stamp (40MHz)

- For each hit:

- Leading Edge (LE): 8-bit DRAM memory

- Trailing Edge (TE): 8-bit DRAM memory

- Address: 6-bit ROM memory

- TOT = LE TE(off-chip)

| IO pads | IO pads                                                    | IO pads                                                 | IO pads               | IO pads        | IO pads                                                                     | IO pads |

|---------|------------------------------------------------------------|---------------------------------------------------------|-----------------------|----------------|-----------------------------------------------------------------------------|---------|

| Test 1  |                                                            |                                                         |                       |                |                                                                             | Test 4  |

| IO pads | Matrix 1                                                   | Matrix 2                                                | Matrix 3              | Matrix 4       | Matrix 5                                                                    | IO pads |

| Test 2  | with analogue timing<br>circuit to sample the<br>rise time | with time-to-digital<br>converter to sample<br>the time | with super-fast pixel | imaging matrix | multi-purpose<br>matrix to test pre-<br>stitching and<br>routing lines from | Test 5  |

| IO pads |                                                            |                                                         |                       |                | elongated pixels<br>(strip like) to<br>readout ASIC<br>(CLICpix or FE-I4)   | IO pads |

| Test 3  | Юран                                                       | IO pads                                                 | IO pads               | IC page        |                                                                             | Test 6  |

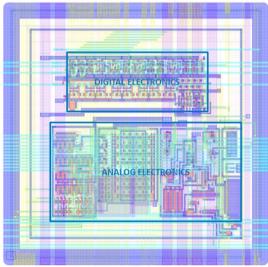

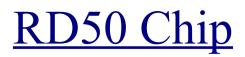

- LFoundry 150nm HV-CMOS

- Designed by: U. Liverpool, U. Barcelona, IFAE, FBK (...)

- IFAE main contribution on the matrix with on-pixel TDC (Time-to-Digital Converter):

- Global Time Stamp: coarse time measurement

- TDC: fine time measurement

- Status: Design phase

More details about the RD50 Chip in E. Vilella talk

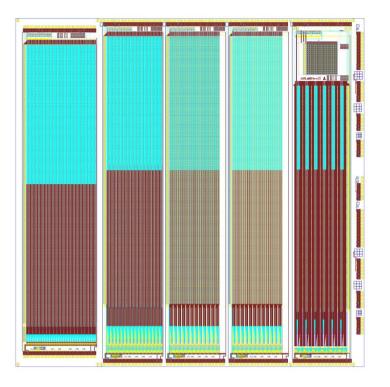

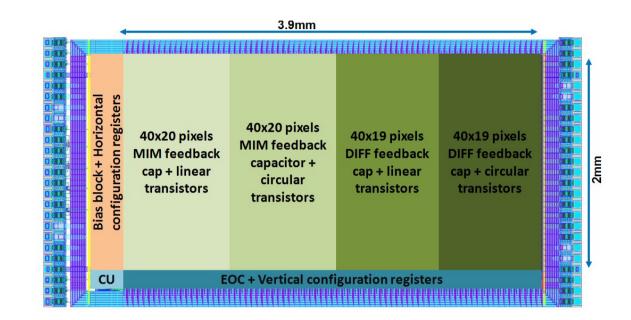

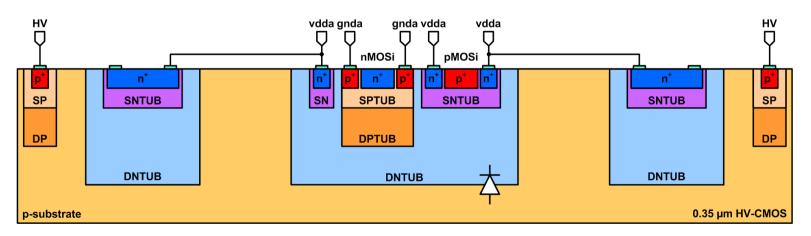

## H35Demo Chip

A large area demonstrator chip in the AMS  $0.35\mu m$  HV-CMOS technology produced on wafers of different resistivity: 20  $\Omega$ cm (standard), 80  $\Omega$ cm, 200  $\Omega$ cm, 1 k $\Omega$ cm

Designed by KIT, IFAE and University of Liverpool

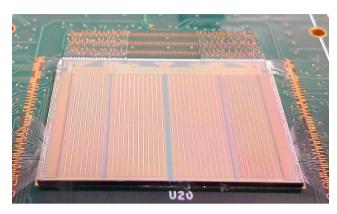

#### **Eight different pixel matrix flavors:**

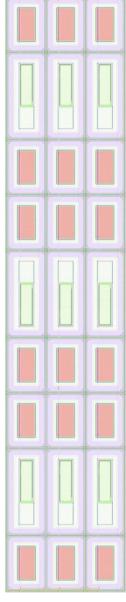

Monolithic nMOS matrix

Digital pixels with in pixel nMOS comparator

Two flavors: w/ Time Walk compensation and w/o Time Walk compensation

• Analog matrix (2 arrays)

Different flavors in terms of gain and speed

- To be capacitative coupled to FE-I4 readout chips

- Monolithic CMOS matrix

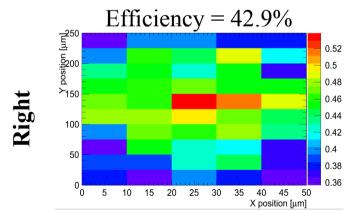

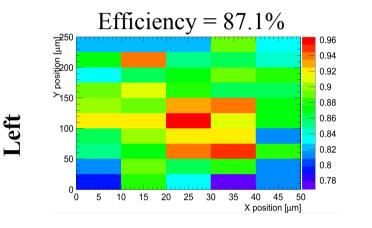

- Analog pixels with off pixel CMOS comparator In the readout cells:

- 1 discriminator for the left half

- 2 discriminators for the right half

## Monolithic matrix readout

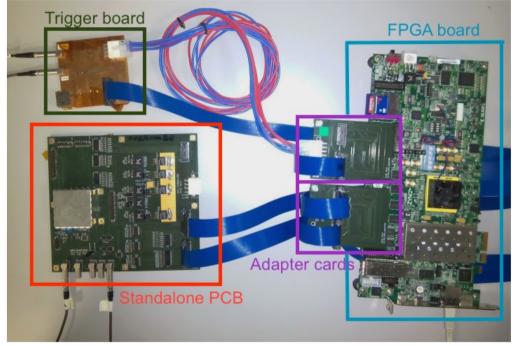

Readout of the monolithic matrices developed at IFAE: hardware, firmware and software

FPGA board:

• Xilinx ZC706

H35Demo PCB:

- Low voltage regulators

- Sensor bias

- Test pulse input

- Analog signal output

- Able to program all matrices and read both CMOS and nMOS

Trigger board:

- Trigger in

- Busy out

#### Steering software

| Select scan        | Matrix           | Scan parameters |           |                 |          |   |

|--------------------|------------------|-----------------|-----------|-----------------|----------|---|

| THRESHOLD_SCAN     | CMOS O           | Max events      | 100       | 0 Voltage min   | 0,200 V  | 0 |

| START Scan STOP Sc | an Continue scan | Injections      | 25        | C Voltage max   | 1,200 V  | 0 |

|                    |                  | Timeout         | 100,00 ms | Voltage steps   | 50       | 0 |

|                    |                  | Clocks          | 430       | C Event block   | 60       |   |

|                    |                  | Event buffer    | 10000     | C Dead time     | 1        |   |

|                    |                  | Column interval | 5         | C Trigger delay | 50       |   |

|                    |                  | Row interval    | 15        | C Threshold     | 0,600 V  |   |

|                    |                  |                 |           |                 |          |   |

|                    |                  | Instrument      |           |                 | C Refres | h |

|                    |                  |                 |           |                 | Refres   | h |

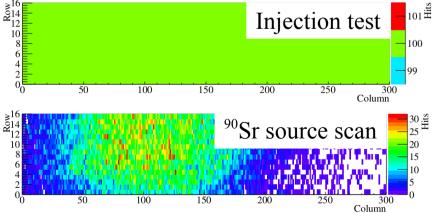

#### Preparatory lab test

Emanuele Cavallaro - 30th RD50 Workshop - 5-7 June 2017

## Threshold tuning

| Monolit<br>Flavour                  |                  | MOS Matrix<br>Flavour 2 |  |  |  |  |

|-------------------------------------|------------------|-------------------------|--|--|--|--|

| Ar                                  | alog Matı        | <b>J Matrix</b>         |  |  |  |  |

| Flavour 3                           | <sub>Flave</sub> | Flavour 4               |  |  |  |  |

| Ar                                  | nalog Matı       | <b>ix</b>               |  |  |  |  |

| Flavour 5                           | Flavour 6        | Flavour 7               |  |  |  |  |

| Monolithic CMOS Matrix<br>Flavour 8 |                  |                         |  |  |  |  |

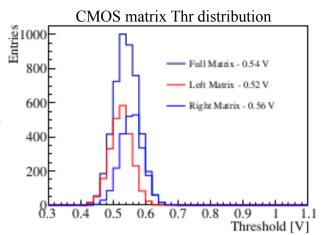

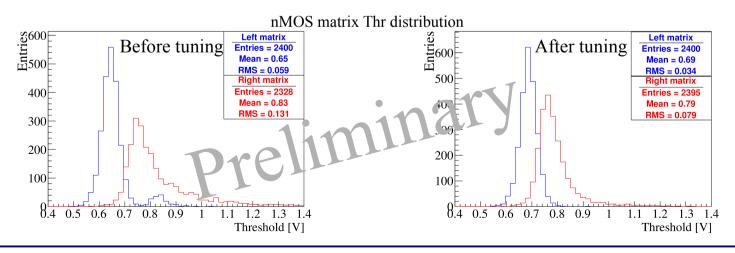

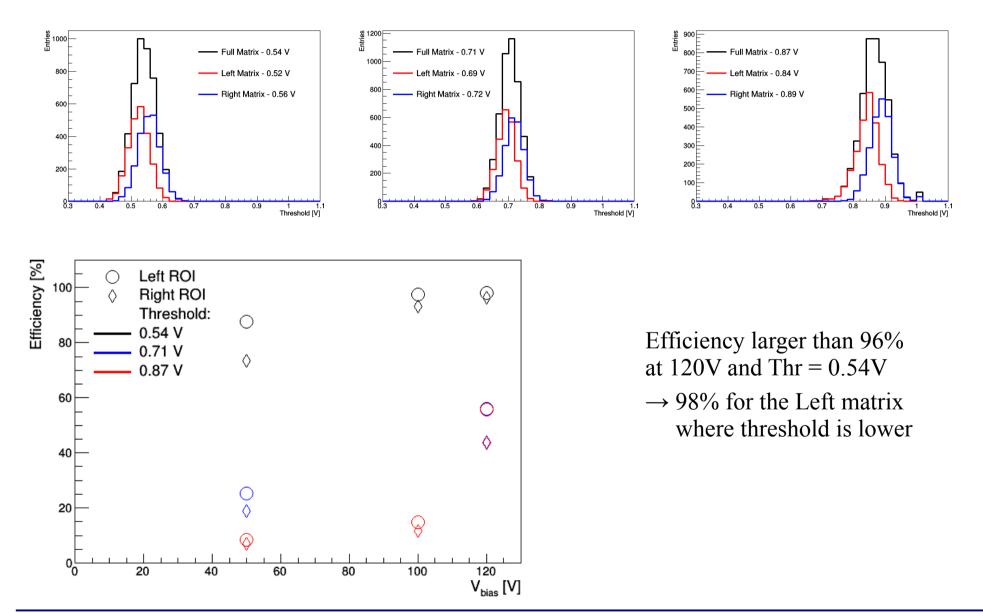

There is a large threshold dispersion if the chip is not tuned, the left and right parts of the matrix have two different distributions

On the CMOS matrix a 4-bit DAC per each pixel is available in the periphery (TDAC)

- The left part of the matrix stops responding after the TDAC is changed

- When assigning different values to each pixel the outcome is not the expected one

On the nMOS matrix an in-pixel 2-bit DAC is available

- It allows to recover the pixels out of the central distribution for the left matrix

- Time-Walk discriminator need to be adjusted to recover the right matrix

#### Test beam in collaboration with UniGe

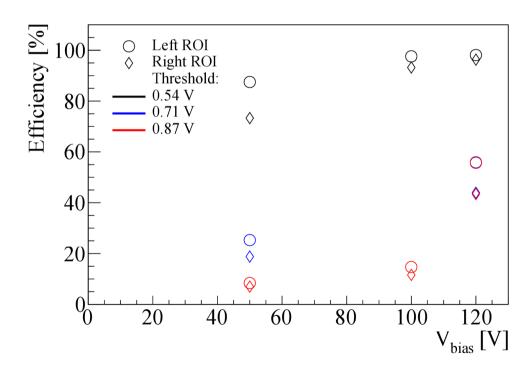

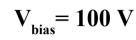

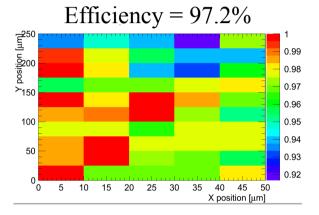

First Test Beam (TB) w/ UniGe FEI4 telescope in November 2016 @ CERN SPS

- CMOS matrix of a non irradiated 200  $\Omega cm$  chip tested

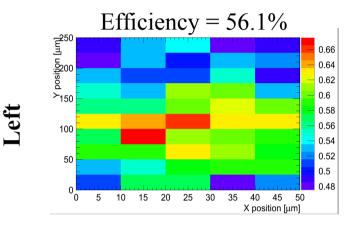

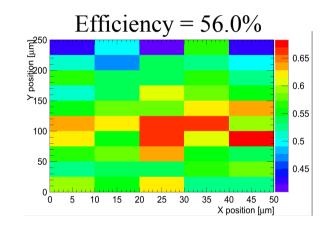

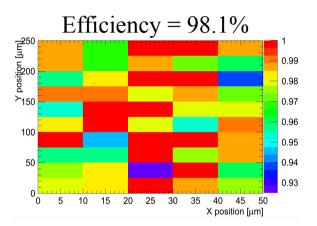

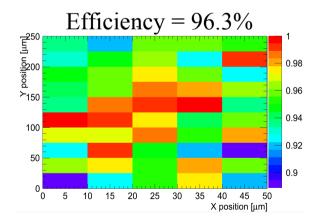

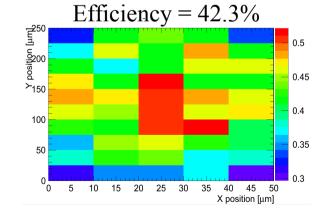

- Maximum efficiency of 98% (97%) on the left (right) half of the CMOS matrix

- Threshold value too large to have larger efficiency at lower voltage

- Left/Right asymmetry can be explained by the different threshold distribution

- Results presented at Instrumentation for Colliding Beam Physics (INSTR17) by S. Terzo

→ arxiv.org/abs/1705.05146

Thanks to the UniGe ATLAS group: M. Benoit, F. Di Bello, M. Kiehn, B. Ristic and M.V. Barrero Pinto

#### Test beam in collaboration with UniGe

Second TB w/ UniGe FEI4 telescope in April 2015 @ Fermilab, first time with irradiated chips

Beam properties: - 120 GeV protons

DUTs: Non irradiated devices -  $\rho = 20, 80, 200$  and  $1000 [\Omega cm]$ Irradiated devices w/  $\rho = 200 [\Omega cm]$ -  $\Phi = 5E14, 1E15 [1 \text{ MeV } n_{eq}/cm^2]$ Irradiated w/ neutron at JSI

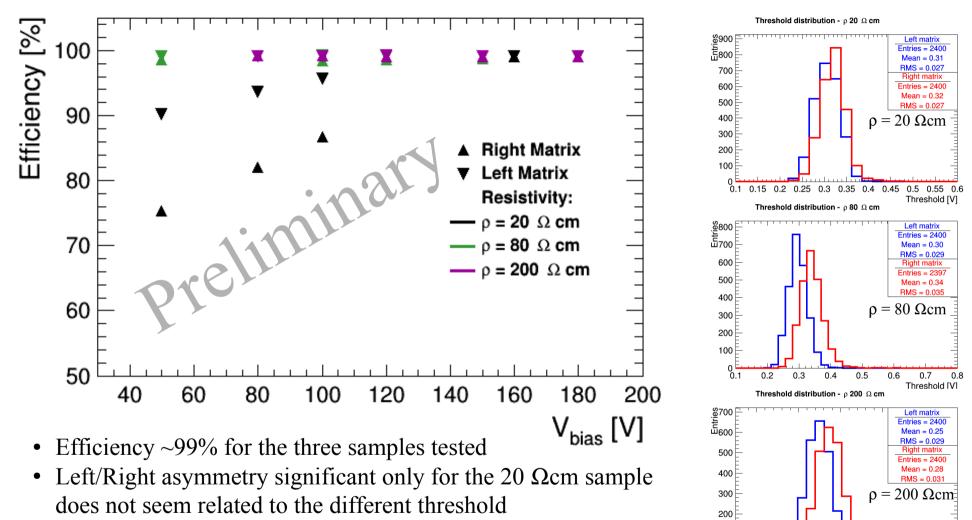

## Non irradiated DUTs

- 1 k $\Omega$ cm sample trips with the spill low V<sub>bd</sub>, probably from a bad wafer

- The 200  $\Omega$ cm sample has larger efficiency than in previous TB where it was tested with a larger threshold

0.5

Threshold [V]

100

0.1

0.2

0.3

0.4

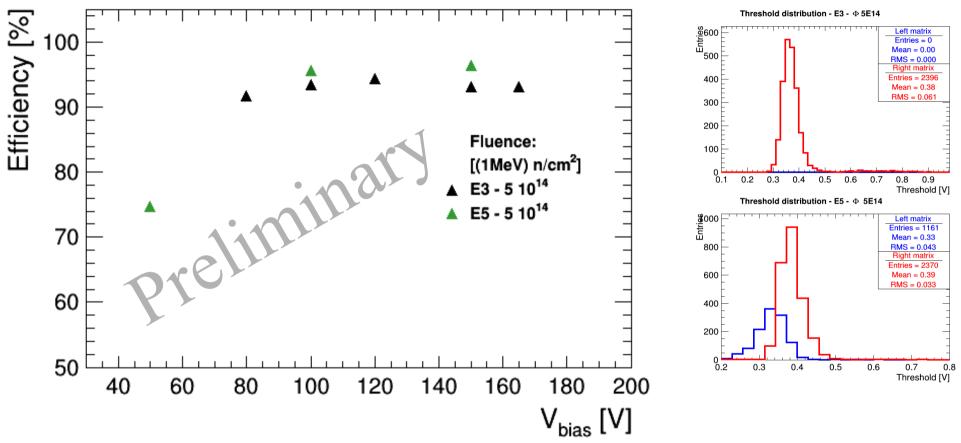

## Irradiated DUTs

- The telescope and H35Demo data streams run out of synchronization

- Current analysis on lower statistics

- Issue more serious on sample w/ higher irradiation dose (analysis ongoing)

- The two samples irradiated at 5E14 n/cm2 have reach an efficiency larger than 90% (a V > 80 V

Thanks to the JSI people for the irradiation effort:

G Kramberger, I Mandic, V Cindro

#### **Conclusions**

- IFAE is involved both in designing and testing HV-CMOS chips for high energy physics experiments

- The first TB of a monolithic matrix of the H35Demo chip after irradiation has been performed

- Non irradiated H35Demo chip of different resistivities tested → Efficiency ~ 99%

- $\rightarrow$  Compatible w/ previous results from the CERN SPS TB

- Synchronization issue for the irradiated samples  $\rightarrow$  Efficiency > 90% on the 5E14 samples

- $\rightarrow$  Preliminary analysis, not full statistics

- Proton irradiated H35Demo chips just received from KIT

#### Thanks

# Backup

### **Motivation**

#### Depleted CMOS for the ATLAS upgrade

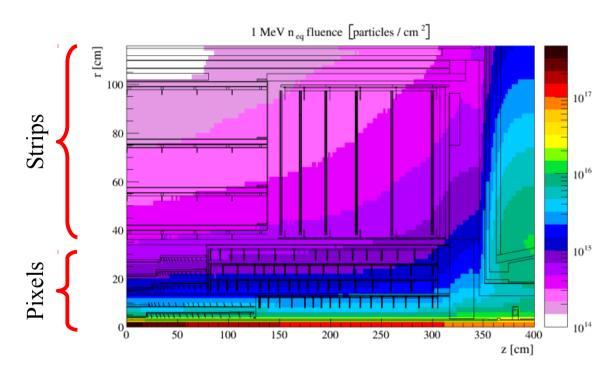

LHC upgrade to High Luminosity LHC scheduled for beginning 2024 Plan to increase the luminosity by an order of magnitude up to  $10^{35}$  cm<sup>-2</sup>s<sup>-1</sup>

Detector challenges: particle multiplicity - pileup rejection radiation hardness

ATLAS ITk - tracker upgrade for HL-LHC

- 5 layers Pixel detector

- 4 layers Strip detector

A total area of  $\sim 10 \text{ m}^2$  of pixel detectors will be installed

The innermost pixel layer will be required to stand up to a fluence of  $2 \cdot 10^{16} n_{eq}/cm^2$ the outermost layer ~  $10^{15} n_{eq}/cm^2$

Sketch of an event in ATLAS at HL-LHC

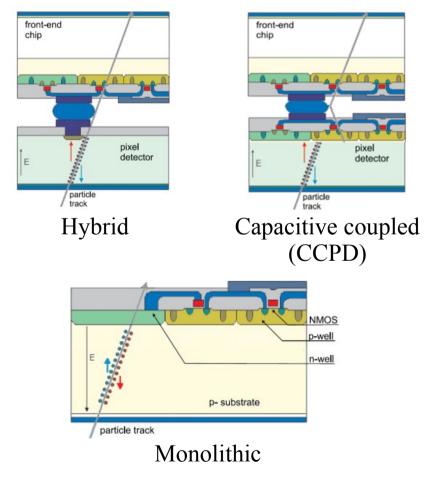

Depleted CMOS technologies being investigated in ATLAS as an option for the HL-LHC upgrade

ATLAS groups are investigating the performances of:

- Devices from different foundries

- Different approaches: CC coupled – monolithic

H35Demo

#### H35Demo test structure

The tested structure is a matrix of 3x3 pixels of  $50.250 \ \mu\text{m}^2$  each

- 3 deep N wells in each pixel

- central 50·110  $\mu m^2$

- external 50.70  $\mu$ m<sup>2</sup>

- no electronics inside the pixels

- deep P well inside the deep N well of the central N well

- deep N wells covered by a layer of polysilicon in the external N wells

- central pixel (marked in red in the figure) is read out individually

- signals of the 8 external pixels are shorted together

#### Backup

Requirements for inner and outer layers of the ATLAS ITK differ by orders of magnitude in terms of radiation tolerance, occupancy, ...

Possible solution: Hybrid solution for the inner layers CMOS monolithic or CCPD for the outer layers

CCPD and monolithic could be more cost effective and meet radiation hardness requirements for the outer layers

#### Different options:

#### **HV-CMOS** for HEP

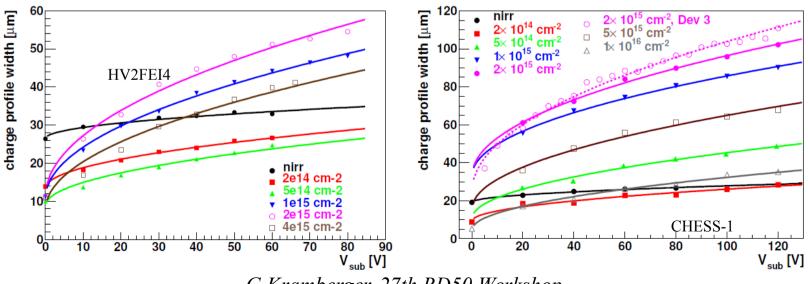

Several productions from different foundries have been made Each with its production technology and wafer resistivity:

- AMS 350nm,  $\rho = 20\Omega \cdot \text{cm}$  (CHESS-1)

- AMS 180nm,  $\rho = 10\Omega \cdot cm$  (HV2FEI4)

- LFoundry 150nm,  $\rho = 2k\Omega \cdot cm$

- X-FAB 180 nm,  $\rho = 100\Omega \cdot cm$

Interesting results have been obtained but it is hard to compare devices from different foundries because of different technologies, substrate doping and well properties

G Kramberger, 27th RD50 Workshop

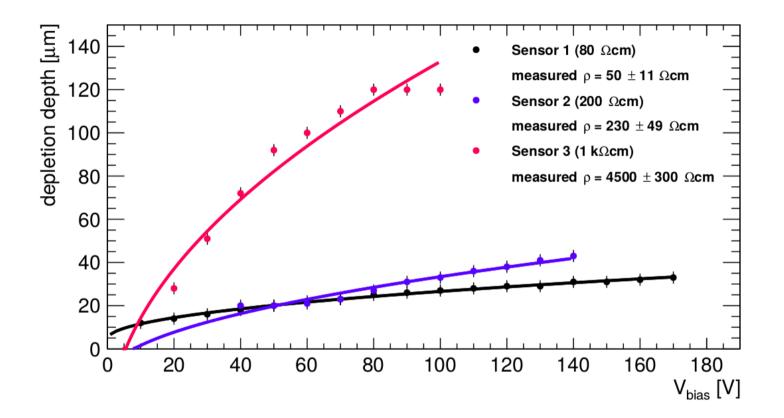

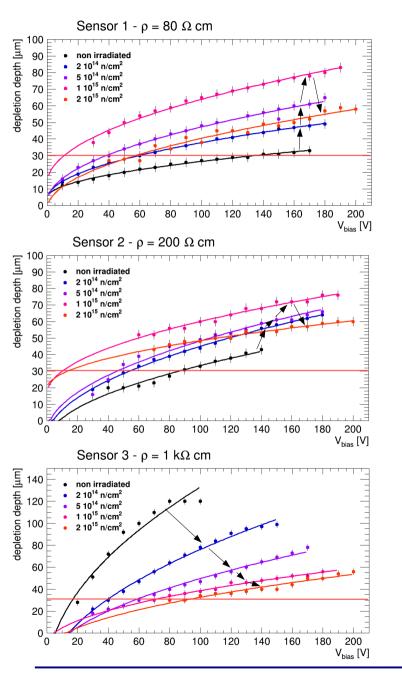

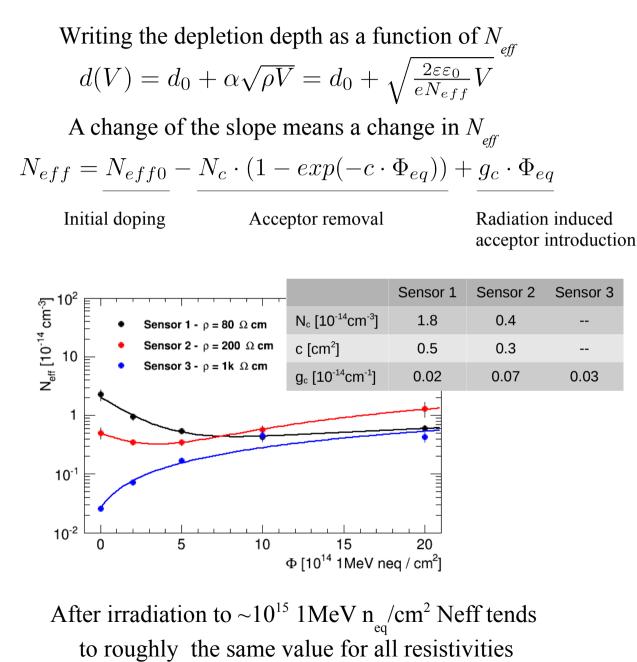

## Depletion depth

Depletion depth measured with edge-TCT on a scanning TCT set-up

#### **Depletion depth - irradiated**

Emanuele Cavallaro - TCT Workshop - 17-18 October 2016

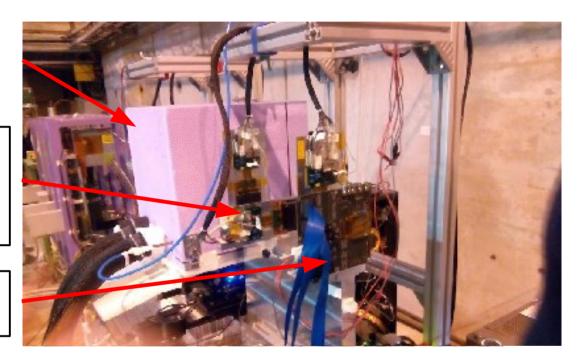

#### TB set-up

UniGe FEI4 Telescope and IFAE DAQ system for monolithic H35Demo chip

#### UniGe Cooling box

- Irradiated samples

- UniGe Telescope

- 6 x FEI4 planes

- 2 planes rotated 90°

- RCE readout

IFAE H35Demo PCBCMOS matrix aligned to the beam

#### Integration with the Geneva FEI4 telescope (Trigger – busy scheme)

- Triggers from the telescope reach the Xilinx FPGA board

- Busy signal from the FPGA is risen to stop the DAQ until H35 is ready again

- Events are written separately and sequentially by each DAQ system

- System running at 25 ns with ~2 kHz trigger rate

#### November 2016 TB resumee

Threshold distribution has Left/Right asymmetry, tuning not implemented

#### In-pixel efficiency Threshold dependence

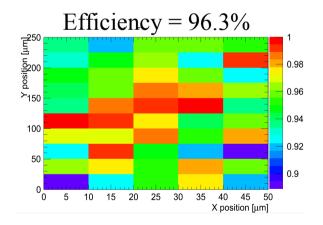

Threshold = 0.87 V

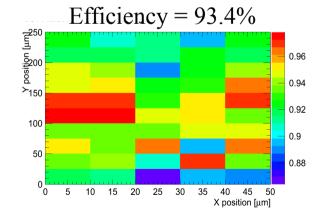

Threshold = 0.71 V

$V_{bias} = -120 V$

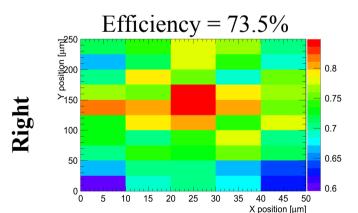

#### In-pixel efficiency Bias voltage dependence

$V_{bias} = 50 V$

Threshold = 0.54 V