# The Phase-1 Trigger Readout Electronics Upgrade of the ATLAS Liquid Argon Calorimeter

Yuji Enari, ICEPP, the University of Tokyo

On behalf of ATLAS LAr group

CALOR 2018, Eugine, Oregon, US 2018 May 23rd

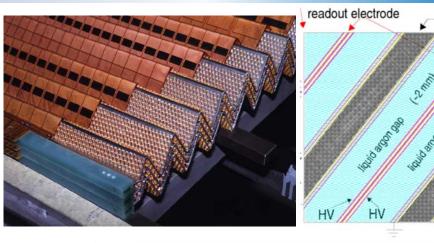

# ATLAS Liquid Argon Calorimeter

12m

ATLAS LAr Phase-1 upgrade *Y. Enari* 2 / 20

absorber

Ar electromagnetic end-cap (EMEC) Ar electromagnetic barrel Ar electromagnetic barrel Ar forward (ECal)

- Pb-LAr EM sampling calorimeter

- $\sigma/E \sim 10\%/\sqrt{E \oplus 0.7\%}$

- fine granularity:  $\Delta \eta x \Delta \phi = 0.025 \times 0.025$  (middle layer)

- Total 22 X<sub>0</sub>

- 4 layers, total 180 x 10<sup>3</sup> channels

- $e/\gamma$  trigger, ID, transverse energy

- → Essential for precise measurements, esp. Higgs physics

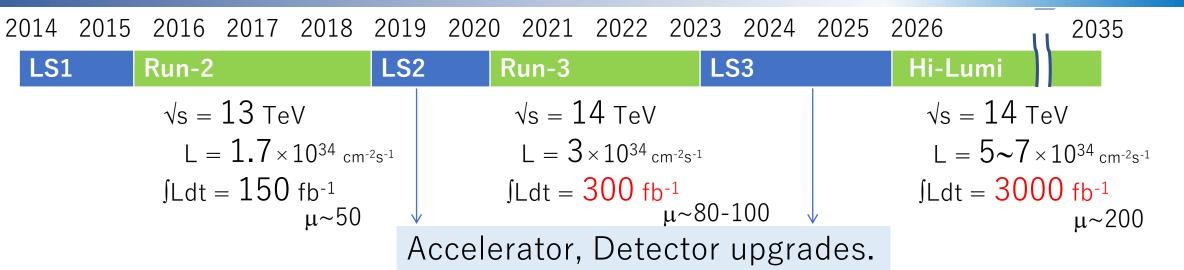

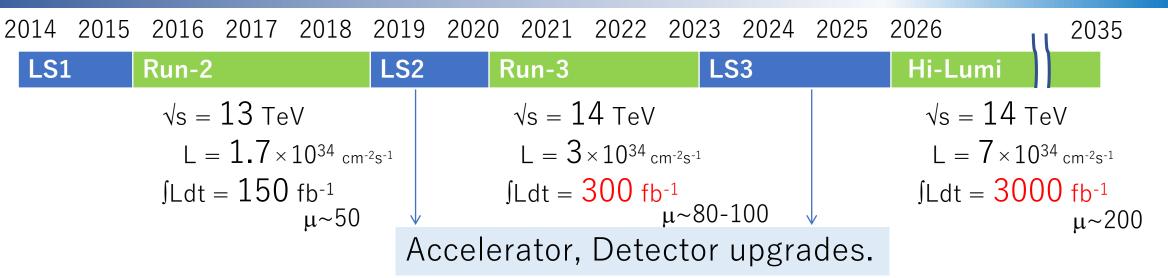

## LHC upgrade schedule

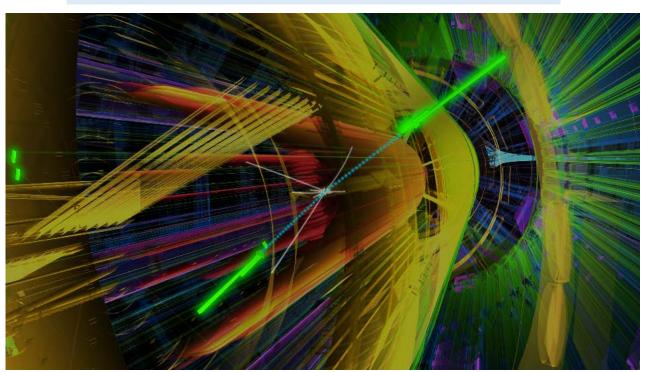

Event with two photons. (Recorded in 2014) Aiming such clean condition at high luminosity runs.

# LHC upgrade and ATLAS Calorimeter

### **ATLAS LAr Calorimeter upgrade:**

### LS2: Phase-1 upgrade

- Trigger readout upgrade

- Level-1 trigger 100 kHz ~ latency 3 μs

- data recording rate:1 kHz.

### LS3: Phase-2 upgrade

- Main readout upgrade

- Forward part detector upgrade

ATLAS LAr Phase-1 upgrade

Y. Enari

4/20

- Level-1 trigger

- $1 \text{ MHz} \sim \text{latency } 10\text{--}20 \ \mu\text{s}$

- data recording rate: 5~10 kHz.

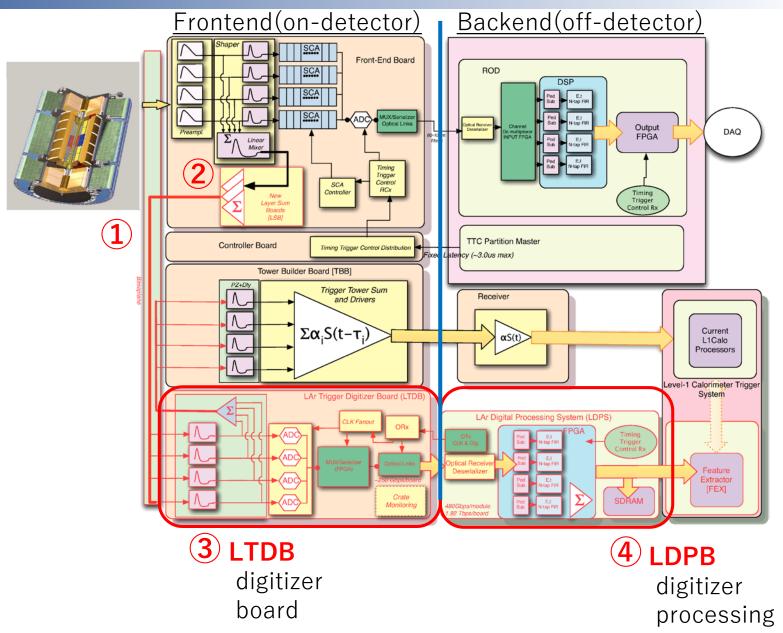

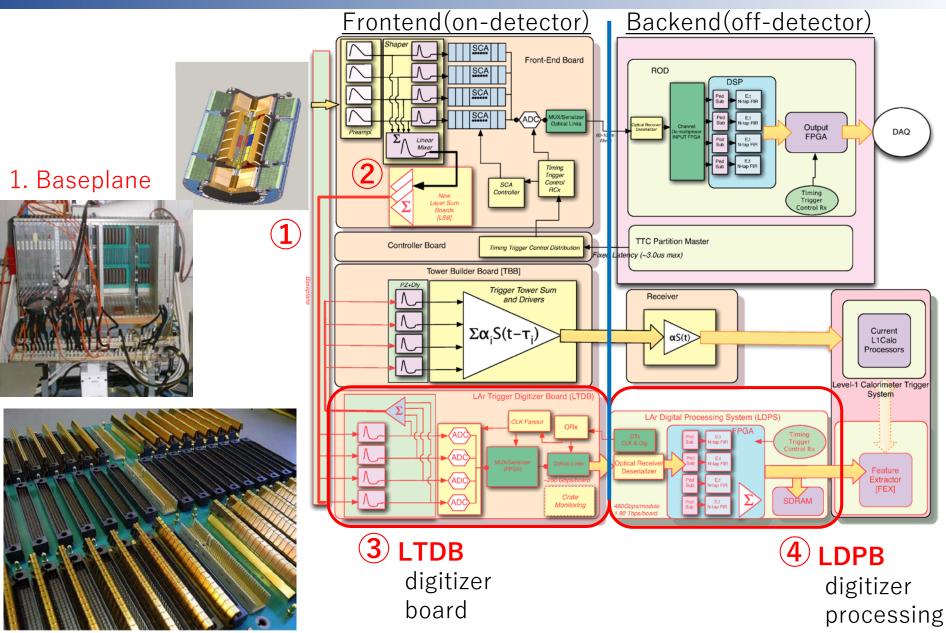

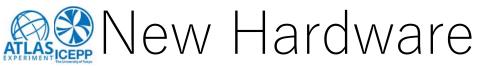

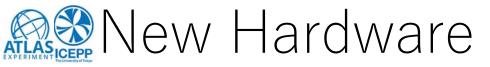

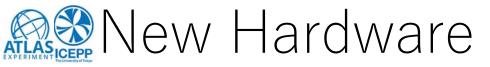

# ATLAS LAr Phase-1 upgrade project

ATLAS LAr Phase-1 upgrade *Y. Enari* 5 <sub>/ 20</sub>

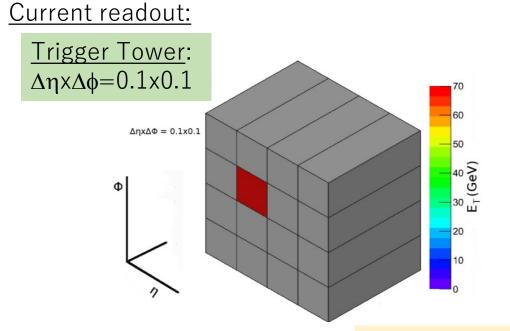

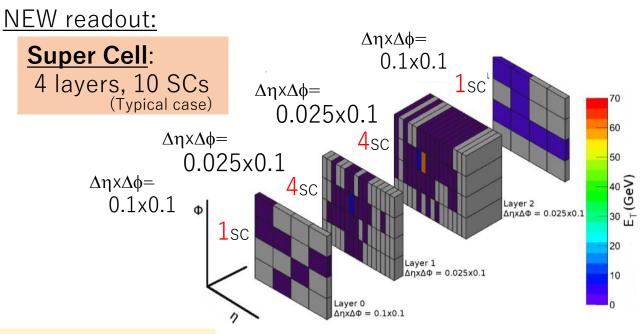

• Upgrade for Calorimeter trigger in LS2(2019-2020)

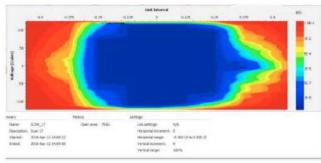

Electron with 70 GeV Size of Moliere radius in  $\eta$  is  $\sim 0.08$

Digitize at Frontend(on-detector), Realtime processing at Backend (off-detector).

→ High density, high speed data transmission

→ Digital filtering on FPGA  Ten times finer granularity +

Better energy resolution

→ Higher BG rejection

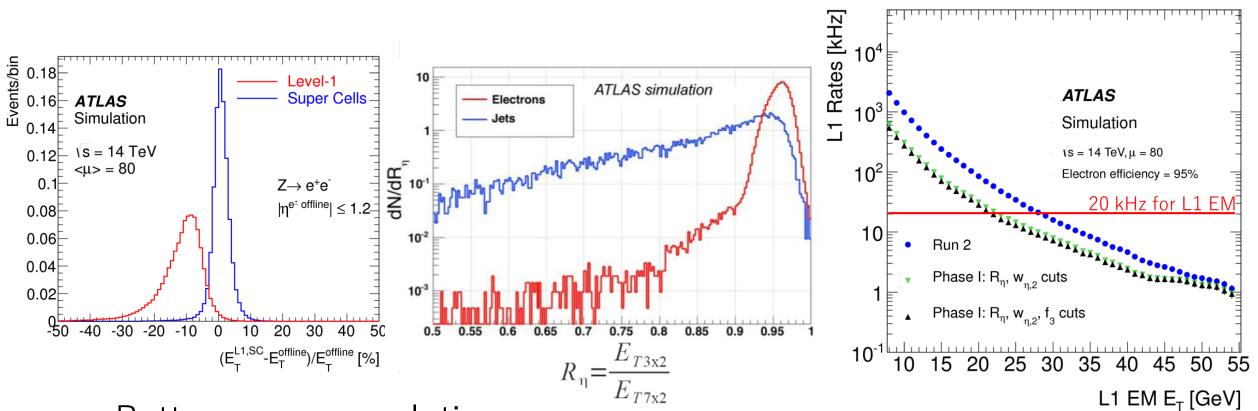

## Expected performance

- Better energy resolution

- Better signal(EM object) to background (Jets) separation

- Keep lower threshold within given Level-1 rate budget (20 kHz for Single EM)

- Very important for the ATLAS physics program!

- For  $W \rightarrow e_{v}$ ,  $Z \rightarrow e_{e}$ ,  $H \rightarrow \gamma \gamma$ : Trigger on EM objects with 20-30 GeV.

ATLAS LAr Phase-1 upgrade *Y. Enari* / 20

ATLAS LAr Phase-1 upgrade *Y. Enari* / 20

ATLAS LAr Phase-1 upgrade *Y. Enari* / 20

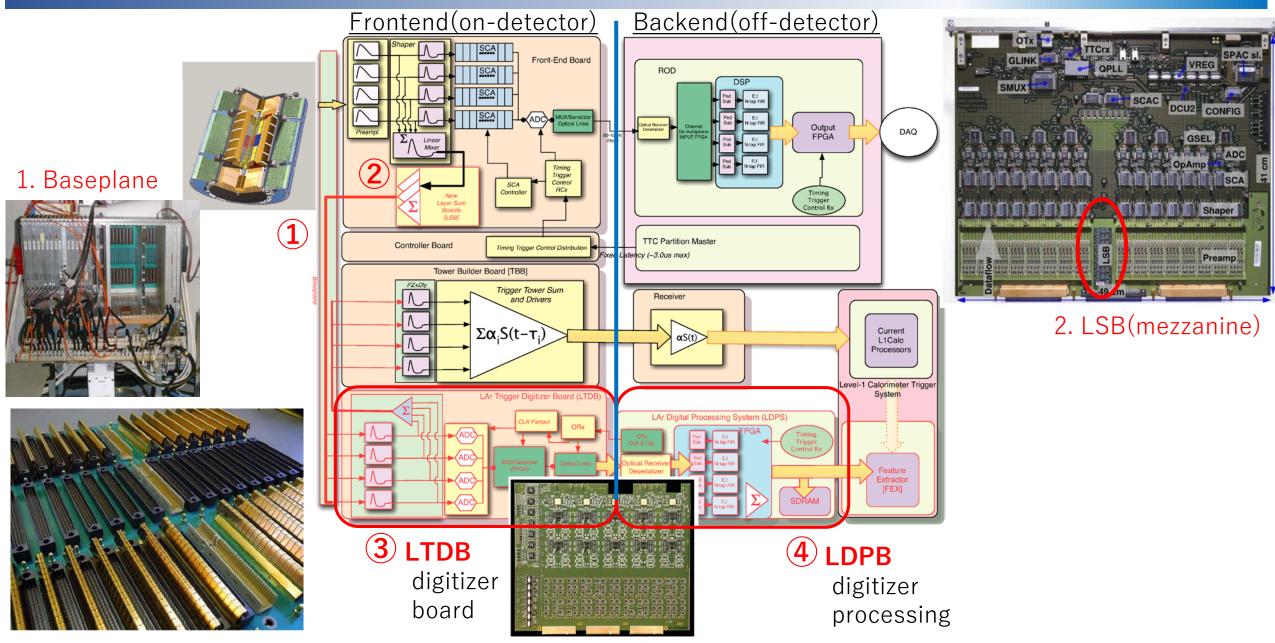

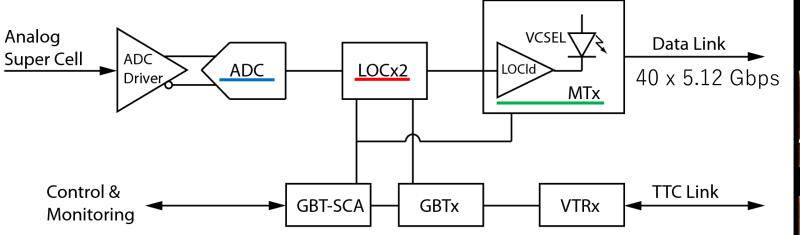

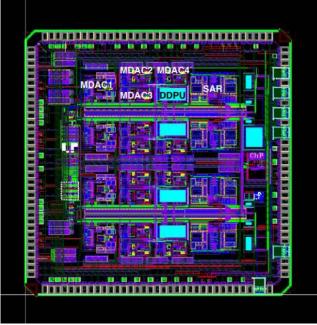

# Frontend: LTDB LAr Trigger Digitizer Board

• Functionalities:

### **Digitize** Analog signal, **serialize** and **transmit**

- Custom radiation tolerant **ASICs**(ADC, serializer)

- 320 Super Cells per board

- 24 layers PCB with 2.23 mm thickness

- Latency < 275 ns

- GBT links used for LHC clock and Trigger information (Timing, Trigger and Control)

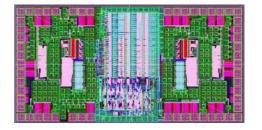

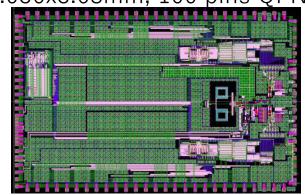

## • Quad channel ADC: Nevis-15

- 40 MS 12 bits pipeline ADC

- IBM8RF 130 nm CMOS

- ENOB 11 bits, Dynamic range: 11.7 Bits

- 50 mW / channel

- Latency ~ 100 ns

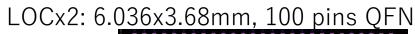

## • Serializer: LOCx2

- Dual channel 8x14 bits

- 5.12 Gbs transmission

- 250 nm Silicon-on-Sapphire

- Fixed latency < 75 ns

- Laser driver: LOCId

- Dual channel VCSEL driver

2.114 x 1.090 mm 40 pins QFN

LOCId:

#### ATLAS LAr Phase-1 upgrade *Y. Enari* 10 / 20

# Radiation tolerance on ASICs

- HL-LHC requirement

- 100 kRad of total dose and SEE tests with total fluency of 3.8 x 10<sup>12</sup> h/cm<sup>2</sup>.

- Quad channel ADC: Nevis-15

- Radiation tolerance established up to 10 MRad

- See cross section as 10<sup>-12</sup> cm<sup>2</sup> per channel

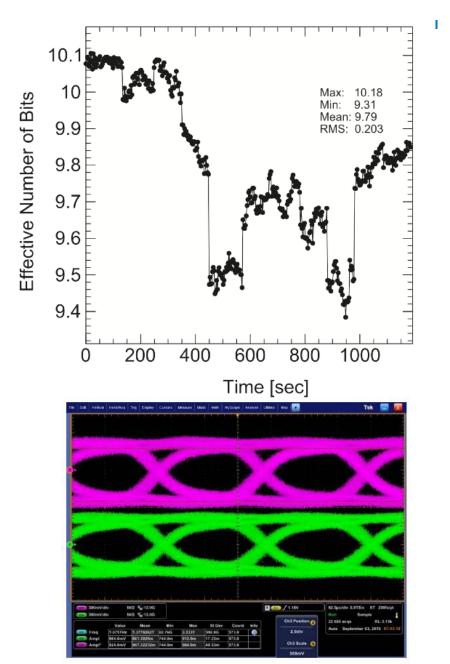

- Serializer(LOCx2) and Laser driver(LOCId)

- No change in the output eye diagram has been observed after ~ 200 kRad TID.

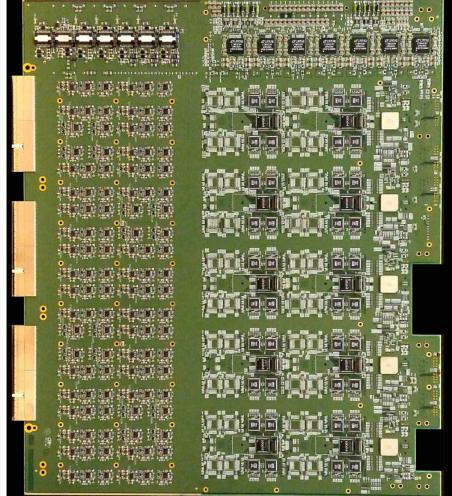

# Towards LTDB production

#### • ASIC production Serializer: LOCx2

- No issue observed in wafer production

- Working on packaging

- Reasonable yields, long term stability

- QA tests on-going.

## • LTDB board

- Pre-production board

- Design is almost final.

- After extensive test, two boards installed in ATLAS

- Replaced two demonstrators installed in 2014.

- Verified Super Cell connectivity.

- Last updates on fiber routing is ongoing.

- QA test stand is under preparation.

### ADC: Nevis-15

- Established 80% yield, including dicing and packaging

- Performed QC test on 186 chips

- Wafer production finished this month

- Established QA procedure

- ~ 2100 chips / week.

- $\rightarrow$  Expect all 13k chips available in Aug.

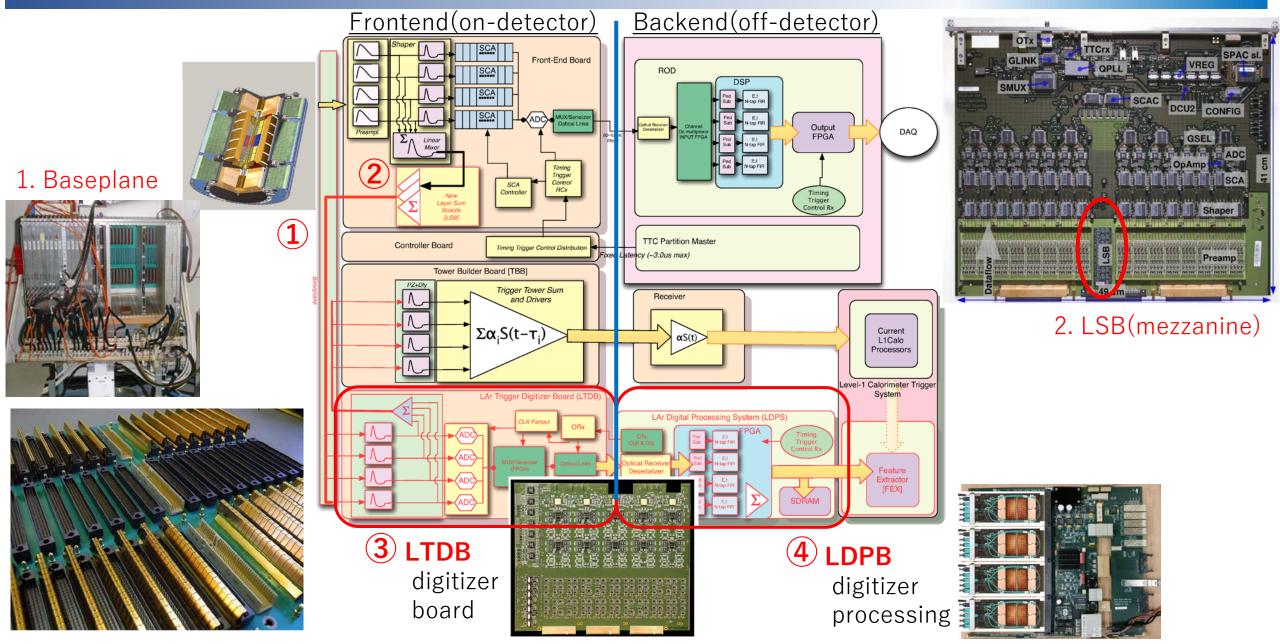

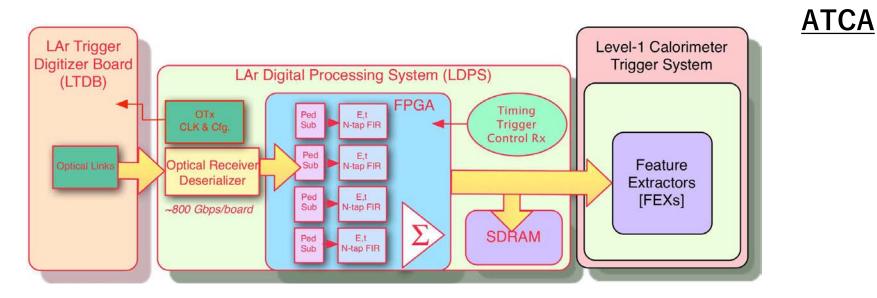

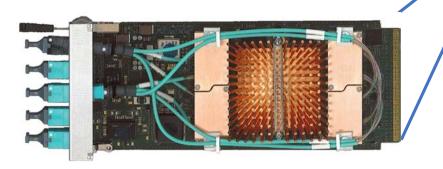

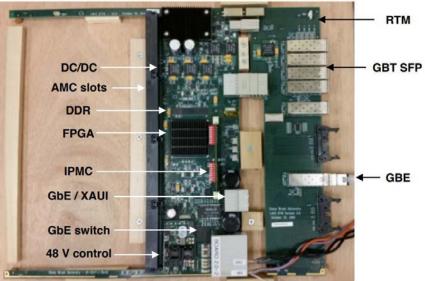

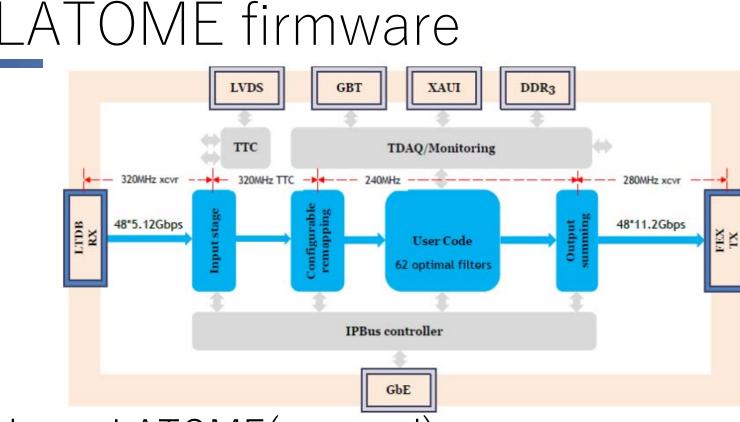

# Backend: LDPB LAr Digital Processing Board

- Main data transfer rate

- 25.2 Tbps from frontend

- 41.1 Tbps to L1 system

- Functionalities:

- Transverse Energy computation

- Energy sum

- Monitoring

Advanced Mezzanine Card (LATOME) → Total 124 LATOMEs

ATCA carrier blade and RTM → Total 32 blades.

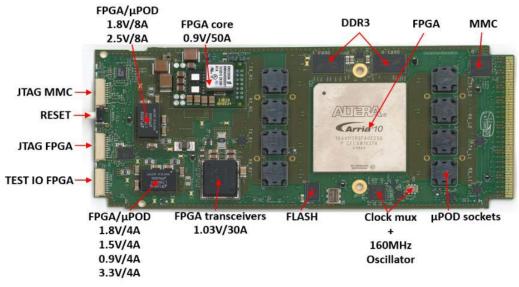

#### ATLAS LAr Phase-1 upgrade AIOME LAr Trigger prOcessing Mezzaine & LArC LAr Carrier card

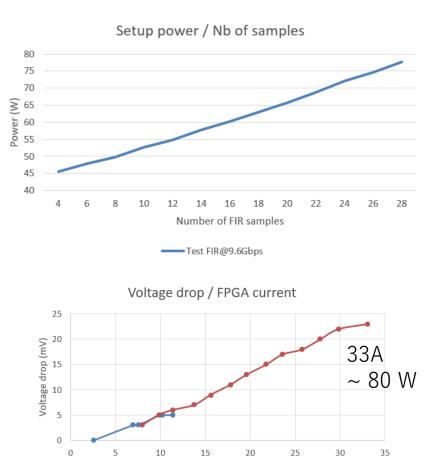

- LATOME (ATCA AMC)

- 16 layer PCB with 1.6 mm thickness

- Power consumption: up to 80 W

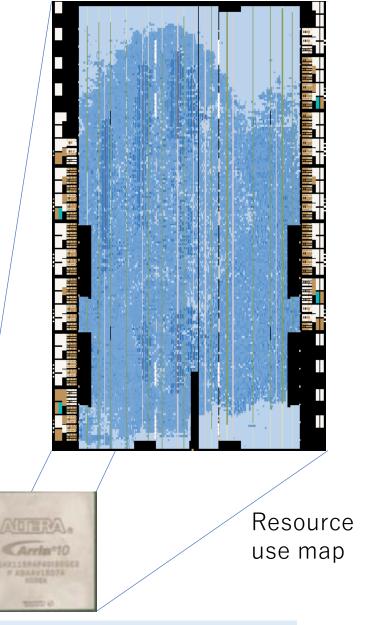

- Intel Arria-10 FPGA

- Data Transmission

- Input: **48 fibers (5.12 Gbps)**

- Output: **48 output fibers (11.2 Gbps)**

- Eight MicroPODs

- 1 GBT links

- LArC: (ATCA Carrier blade with RTM)

- 22 layer PCB with 2.4 mm thickness

- Power consumption: ~280 W

(designed up to 400 W)

Y. Enari 13 / 20

- Xilinx Vertex-7 FPGA

- ATCA IMPC

- Data Transmission

- 10 Gbps link via ATCA fabric

- 5 GBT links via RTM

- 1 Gbps links via RTM (slow control)

- Tasks on LATOME(per card)

- 1. Receive 48 data stream (fiber @ 5.12 Gbps)

- 2. Remap channel

- 3. ET and BC assignment (Filtering)

- Accurate Energy at proper bunch crossing

- 4. Energy Summing ( $\Delta\eta \times \Delta\phi = 0.1x0.1$  and 0.2x0.2)

- 5. Transmit 48 data stream (fiber @ 11.2 Gbps)

ATLAS LAr Phase-1 upgrade *Y. Enari* 14 / 20

Intel-Altera Arria-10 FPGA

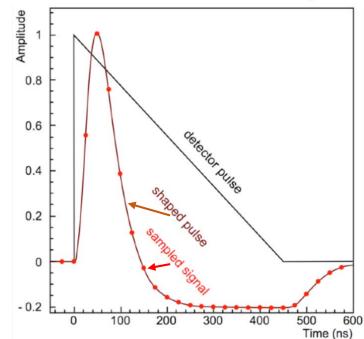

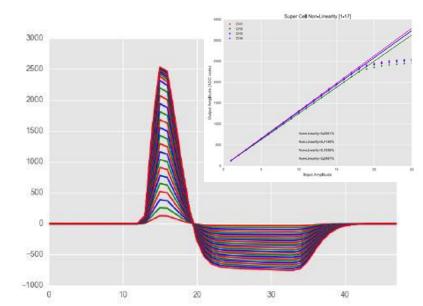

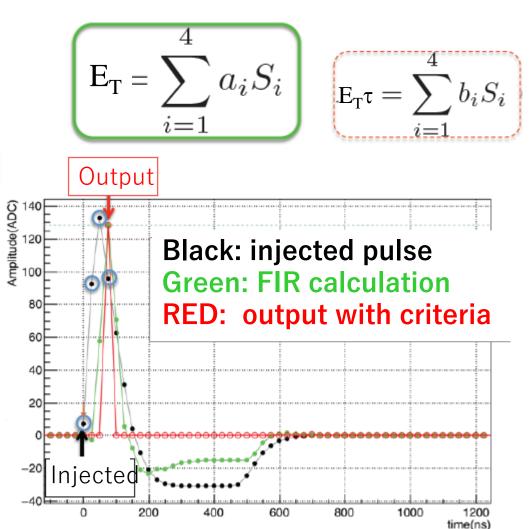

# Energy reconstruction

- Calculate the energy at fixed Latency

- The energy is proportional to peak value of pulse.

- The peak is around 3<sup>rd</sup> point

- FIR calculation(optimal filtering)

- $a_i$ ,  $b_i$  are set to minimize noise by using calibration and physics data.

$$E_T > 0 \& |\tau| < 12.5 \text{ ns}$$

Criteria

An energy with fulfilling the criteria is the energy at the right BC.

Options for alternative filter: Wiener filter, Extended Optimal filter

# Performance test towards production

ATLAS LAr Phase-1 upgrade *Y. Enari* 16 / 20

## **Data transmission**

To gFEX

To eFEX

#### All 48 Rx/Tx: BER (<10<sup>-14</sup>)@11.2 Gbps

#### Power consumption

#### Latency

| Block                     | Spec | Meas    |

|---------------------------|------|---------|

| Interface                 | 2    | 2       |

| Input stage               | 3    | 2.63    |

| Remapping                 | 1.5  | 1.75    |

| ET calc                   | 5    | 4.5     |

| Summing                   | 1.5  | 2.5     |

| Interface                 | 2    | 2       |

| Total                     | 15   | 15.38   |

| Unit <sup>.</sup> BC=25 r |      | 3C=25 n |

Unit: BC=25 ns

Verify a fixed latency on various resets.

All requirements fulfilled. Production has been started!

Verified LATOME operation with full load on FPGA.

FPGA current (A)

– FPGA Transceivers – FPGA Core

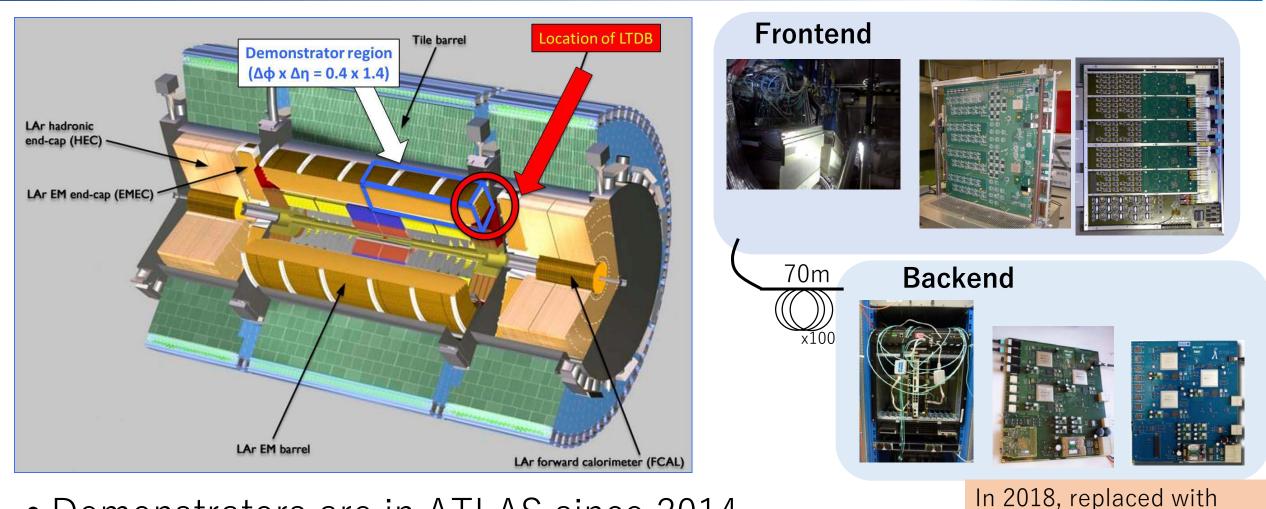

## LAr Phase-1 Demonstrators

ATLAS LAr Phase-1 upgrade *Y. Enari* 17 / 20

pre-production boards.

- Demonstrators are in ATLAS since 2014.

- Collecting collision data in LHC Run2

- Check installation procedure, system feasibility and stability

ATLAS LAr Phase-1 upgrade *Y. Enari* 18 / 20

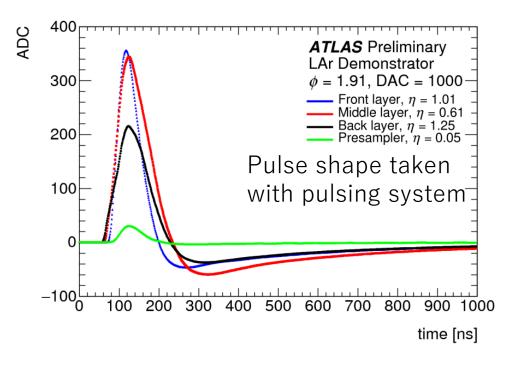

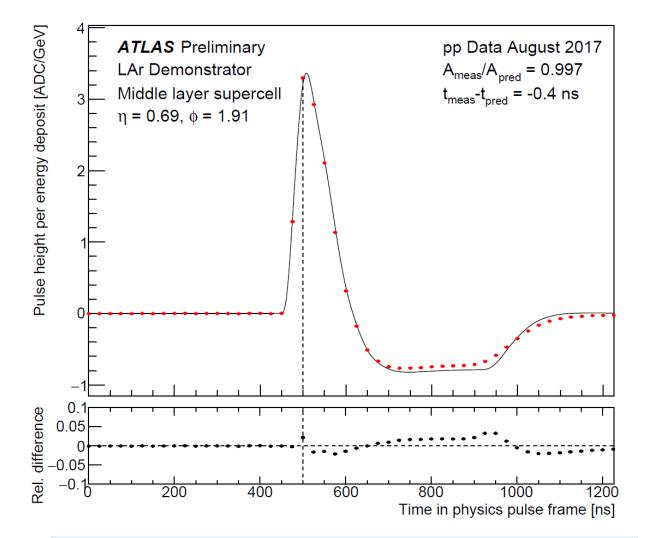

# Demonstrator calibrations

- It is important to understand the pulse shape of Super Cell output to reconstruct the transverse energy.

- Established calibration method for Super Cell.

Expected pulse from calibration run(black). Compared to collision data(red). Good match!

# Collision data with demonstrator

0.7

0.75

ATLAS LAr Phase-1 upgrade *Y. Enari* 19 / 20

Physics pulse timing from OFCs [ns]

• Comparison with Main readout on cluster ATLAS Preliminary  $10^{2}$ LAr Demonstrator pp Data June 2017 ATLAS Preliminary pp Data June 2017 LAr Demonstrator Supercell in the middle layer E<sub>total</sub> = 124.4 GeV  $\eta = 0.69, \phi = 1.91$  $E_{max}^{SC} = 48.7 \text{ GeV}$ • 2.11 Demonstrator 10 2.01. 1.91 Back Well calibrated 1.81 10 Middle 0.4 0.45 Front ET output 0.5 0.55 0.6 0.65 Presampler 0.7 0.75 0.8 ATLAS Preliminary pp Data June 2017 10 25 35 5 15 20 30 LAr Main Readout Demonstrator supercell energy [GeV] E<sub>total</sub> = 135.7 GeV  $E_{max}^{SC} = 49.5 \text{ GeV}$ ATLAS Preliminary pp Data August 2017 Mean = -0.58 ± 0.11 ns LAr Demonstrator 0.35 Back layer supercel RMS = 1.15 ± 0.08 ns  $\eta = 0.65, \phi = 1.81$ 0.3 Main readout 2.11\_ 0.25 2.01\_ Time phase 0.2 1.91. Well distributed 0.15 01 1.81 within same BC. 0.05 0.4 0.45 0.5 0.55 0.6 0.65 (1 BC=25 ns)

- ATLAS LAr Calorimeter Phase-1 upgrade (2018 Dec-2021 Mar)

- Upgrade the trigger readout, will be used for HL-LHC (upto ~2035).

- Frontend: design is almost finalized.

- ASIC packaging and update analog mapping to ease fiber routing

- Backend: going well

- Production will be started soon

- Next: assembling and QA tests

- Demonstrator

- Installed in 2014 August, data taking since beginning of Run-2.

- Established calibration machinery

- compatibility test with Main readout.

- 2018 Jan, replaced with Pre-production board.

- Overall latency, stabilities will be verified.

- Collect more data for filtering studies.