# Trigger Architectures and Hardware

ISOTDAQ 2018 Vienna February 14, 2018

Manfred Jeitler

Institute of High Energy Physics, Vienna

## **Acknowledgments**

This lecture was previously prepared and presented by

Francesca Pastore and Alessandro Thea

page 2 Manfred Jeitler

#### What do we want:

- Get the data we want: efficiency

- ► Get *only* the data we want: purity

- ► Be able to afford the system: cheap

- No breakdowns: robust

- Adjust to changing conditions: flexible

page 3 Manfred Jeitler

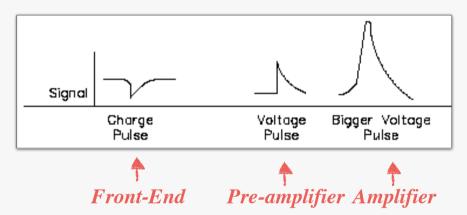

## The simplest trigger system

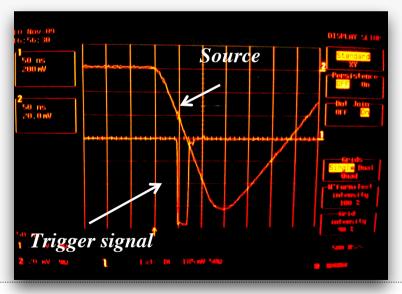

**Source**: signals from detector ("detector Front-Ends")

- ▶ Binary: e.g. tracking detectors (pixels, strips): yes/no

- ► Analog: e.g. calorimeters: pulse height

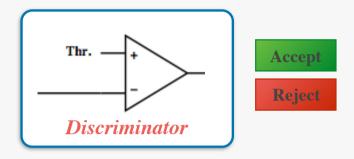

The most trivial trigger algorithm: *Signal > Threshold*

- lowest possible threshold

- compromise between signal efficiency and noise

page 4

## Detector signal characteristics

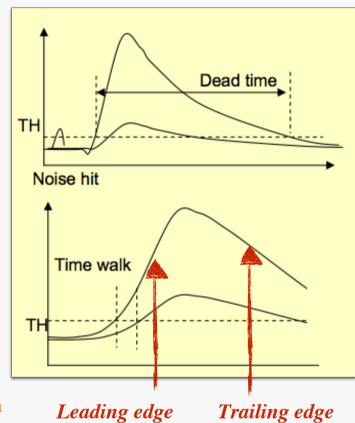

#### Pulse width

- Limits the usable hit rate

- ▶ Must be adapted to the desired trigger rate

#### Time walk

- ▶ The threshold-crossing time depends on the signal amplitude

- ► Affects timing resolution

Time walk can be suppressed by triggering on total signal fraction

- ▶ Applicable on same-shape input signals with different amplitude

- e.g., from scintillators

page 5

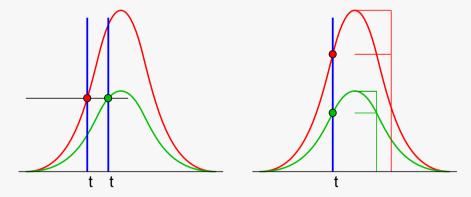

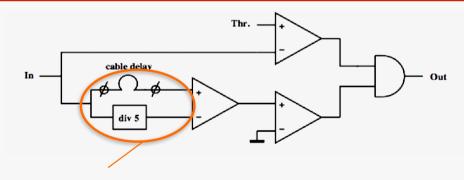

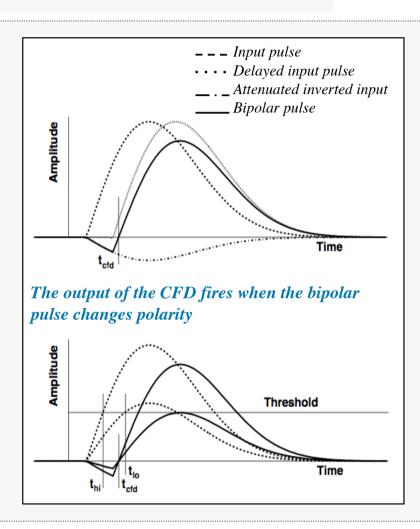

## Constant fraction discriminator

#### Signals with same rise time, at fraction f

$$\Delta t_f = t(f \cdot A_0) - t(A_0) = \text{const.}$$

$$A(t)/f - A(t - \Delta t) = 0 \text{ at } t = t_{CDF}$$

- ► Attenuation + configurable delay

- applied before the discrimination determines  $t_{CFD}$

- If delay too short, the unit works as a normal discriminator

- the output of the normal discriminator fires later than the CFD part

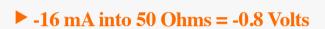

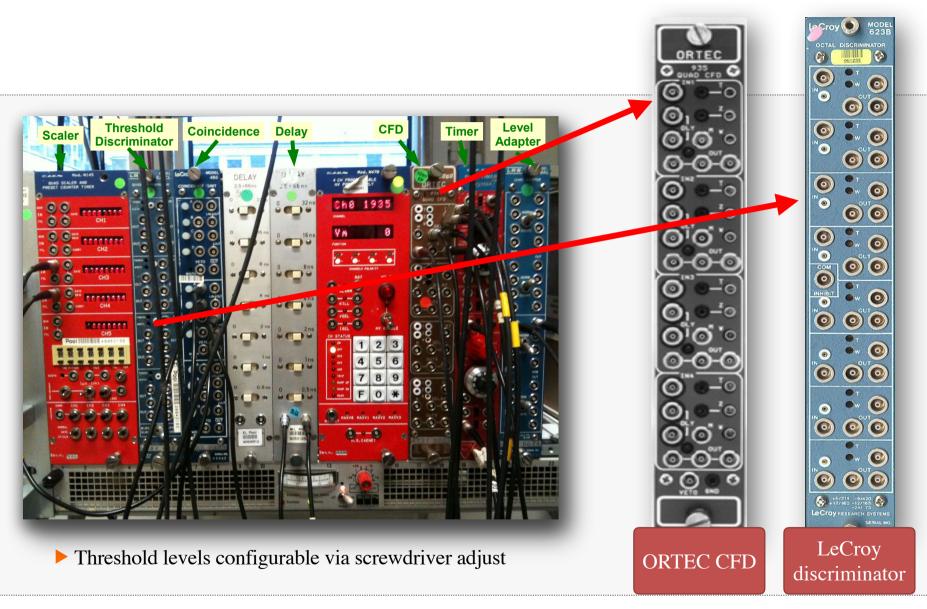

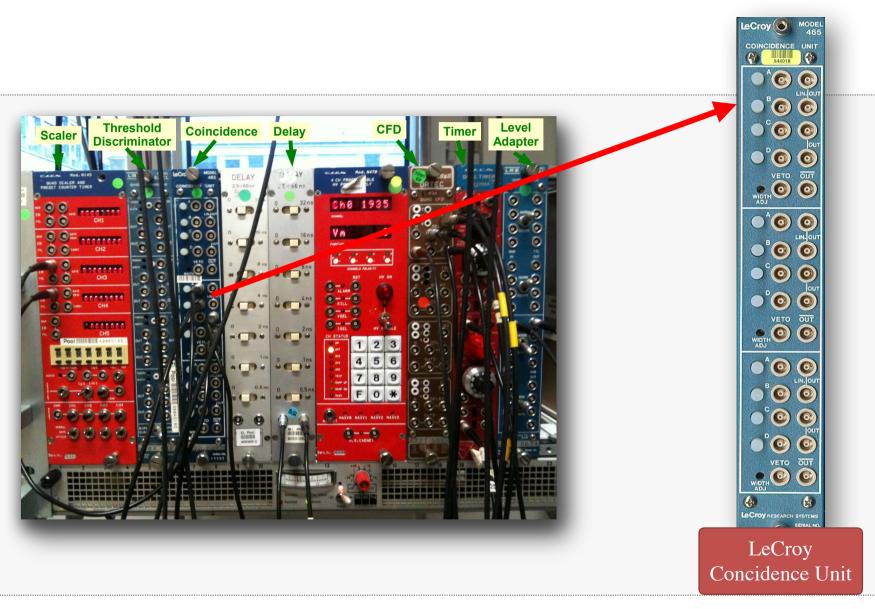

## Build your own trigger system

A simple trigger system can start with a **NIM crate**

- Common support for electronic modules,

- standard impedance, connections, logic levels (negative)

page 7 Manfred Jeitler

page 8 Manfred Jeitler

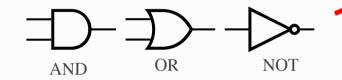

## Trigger logic implementation

## decision logic described by mathematical operators

#### Analog systems

▶ amplifiers, filters, comparators, ...

Digital systems

- Combinatorial sum, decoders, multiplexers,...

- ► Sequential flip-flop, registers, counters,...

Converters

ADC, TDC, .....

page 10 Manfred Jeitler

## We want:

High Efficiency Low dead-time Fast decision

## Wait ... I'm busy!!

- Incoming event rate can temporarily exceed processing rate due to fluctuations

- Trigger signals are then rejected if busy is high, i.e. if previous event is still being processed

page 12 Manfred Jeitler

#### **Dead Time**

The key parameter in high speed T/DAQ systems design

- ▶ The fraction of the acquisition time when no events can be recorded.

- Typically of the order of a **few %**

- ► Reduces the overall system efficiency

$$\epsilon' = \epsilon \cdot (1 - \tau_d)$$

Arises when a given processing step takes a finite amount of time

- ► Readout dead-time

- ► Trigger dead-time

- ► Operational dead-time

page 13 Manfred Jeitler

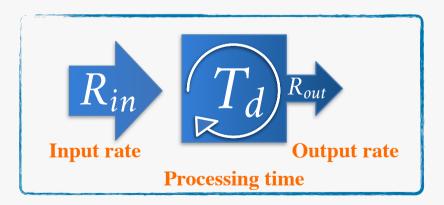

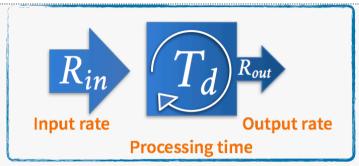

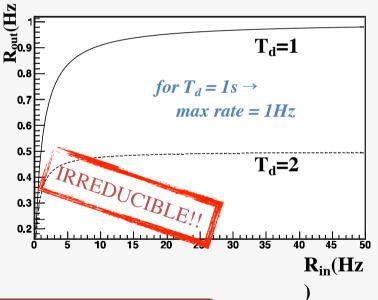

## Maximising data-recording rate

$R_{in}$  = Trigger rate (average)

$R_{out} =$ Readout rate

$T_d$  = processing time of one event

Fraction of lost events  $R_{out} \cdot T_d$

Number of events read  $R_{out} = (1 - R_{out} \cdot T_d) \cdot R_{in}$

Fraction of surviving events

$$\frac{R_{out}}{R_{in}} = \frac{1}{1 + R_{in}T_d}$$

► For instance:  $R_{in} = 1/T_d \rightarrow dead\text{-}time = 50\%$

To achieve high efficiency  $\Longrightarrow R_{in} \cdot T_d \ll 1$

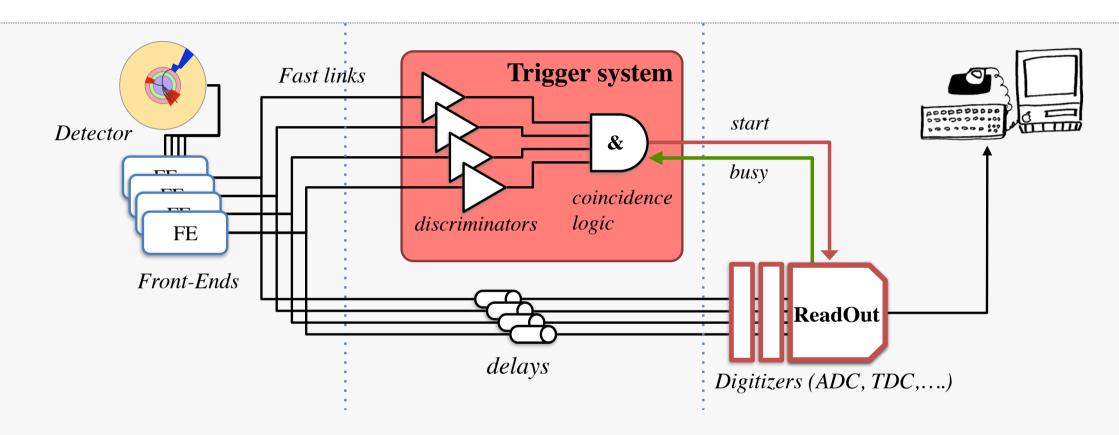

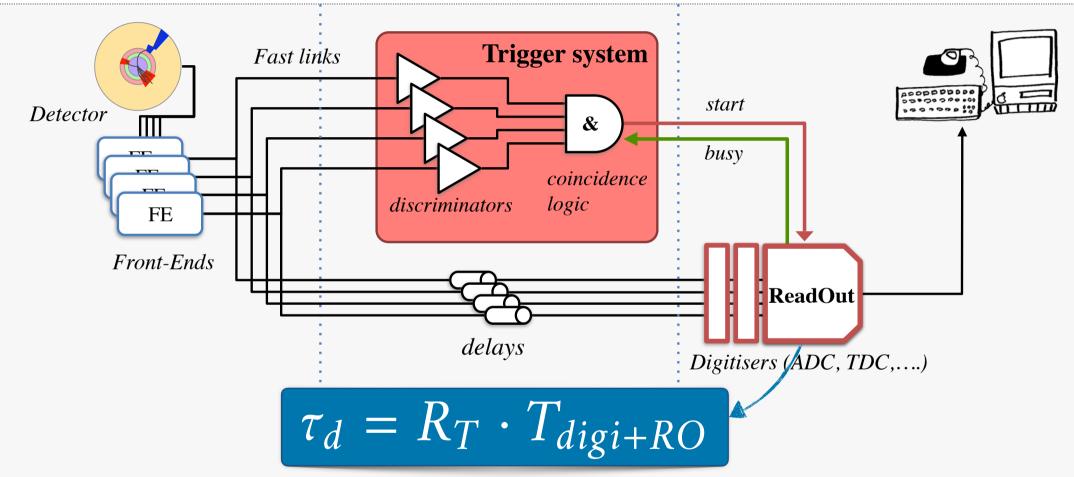

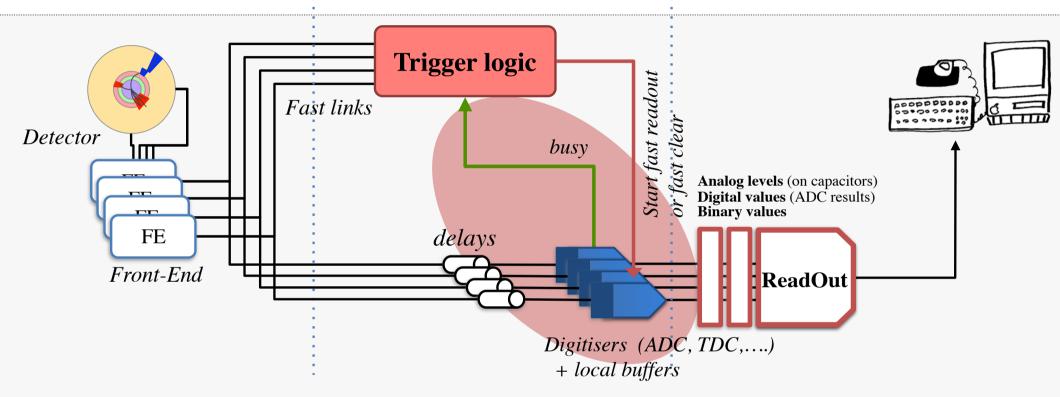

## A simple trigger system

Fraction of lost events due to finite digitisation & readout time

page 15

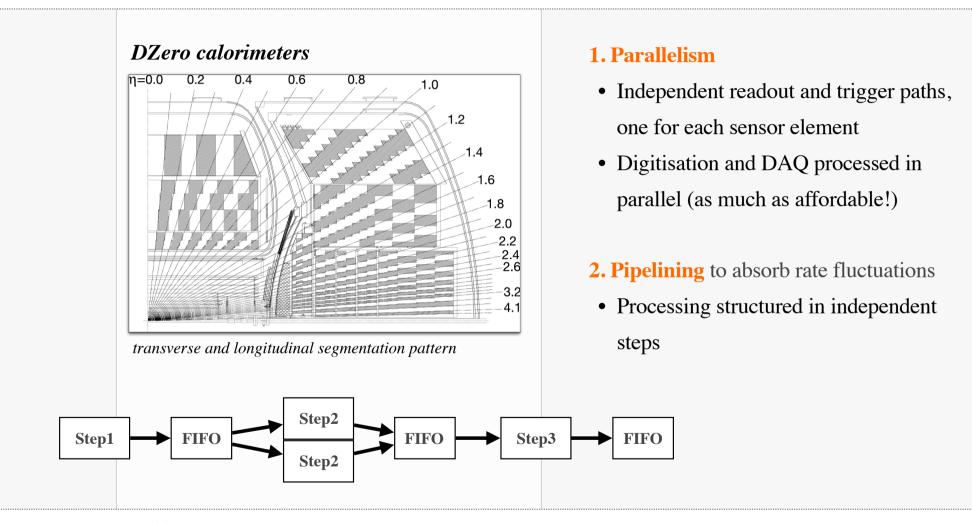

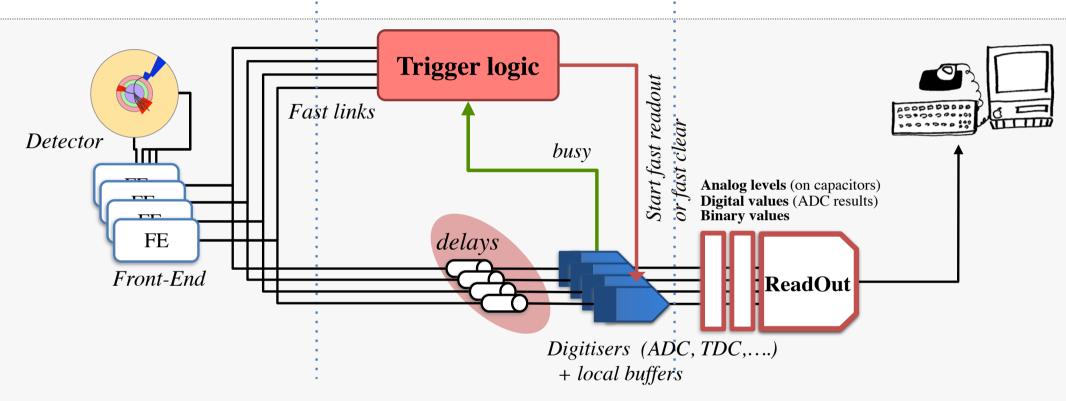

## Approaches to minimise dead time

page 16

### Minimising readout deadtime

Parallelism: Use multiple digitisers

**Pipelining**: Different stages of readout

**▶ local readout (fast) + global event readout (slow)**

## Trigger latency & deadtime

#### Latency: time to form the trigger decision and distribute to the digitisers

- ► Signals must be delayed until the trigger decision is available

- ▶ The more complex is the selection, the longer is the latency

### **Latency**

I'm late! I'm late!

- latency is an important constraint on trigger architecture

- pipeline memory is expensive

- in terms of money, space, energy consumption

- → need fast algorithms

- no iterative loops

- small propagation times → put trigger electronics close to detector

- but not on detector (radiation protection!)

page 19

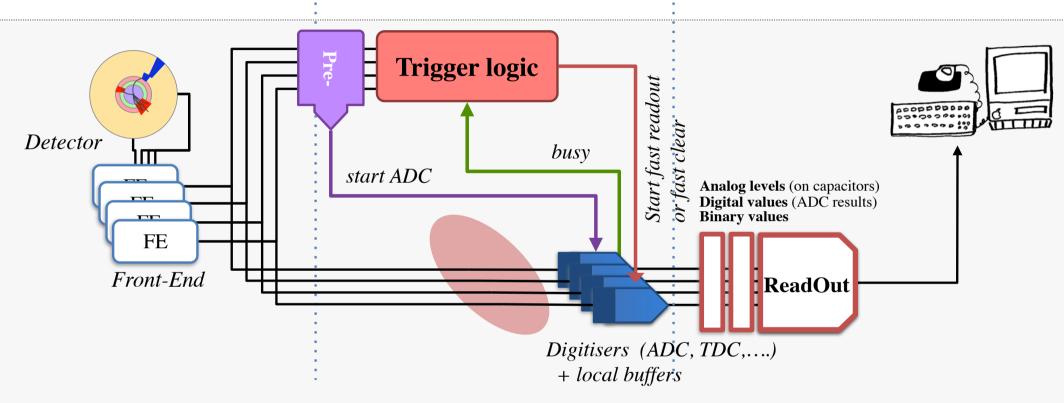

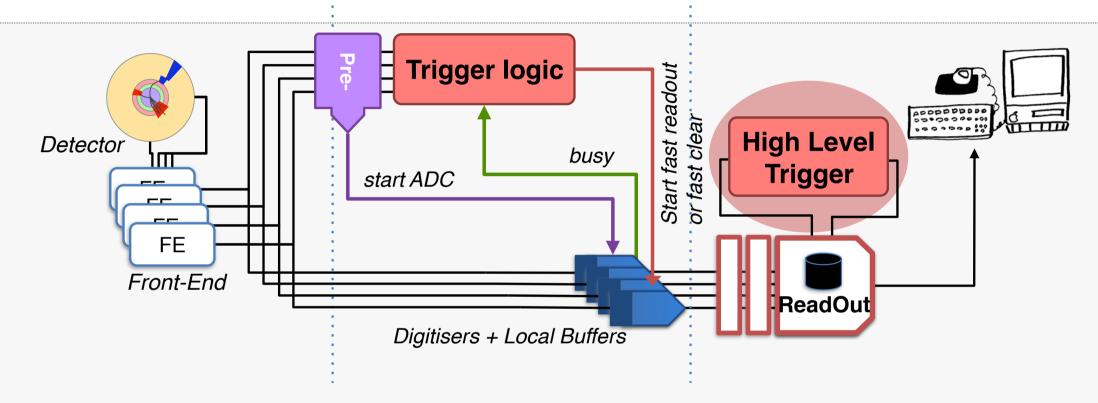

### Pre-trigger stage

Pre-Trigger stage: very fast, indicating presence of minimal activity in the detector

- ▶ Used to START the digitisers, with no delay

- ► The complex trigger decision comes later

- L<sub>T</sub>: pre-trigger processing time ("Latency")

$$\tau_d = R_{pT} \cdot L_T + R_T \cdot T_{LRO}^{fast}$$

page 20

## Trigger and Readout dead time coupling

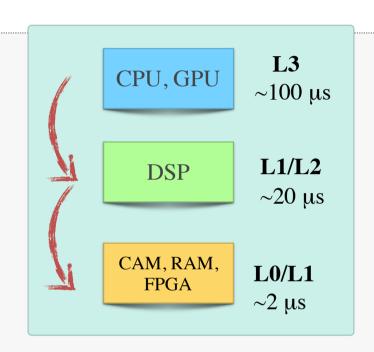

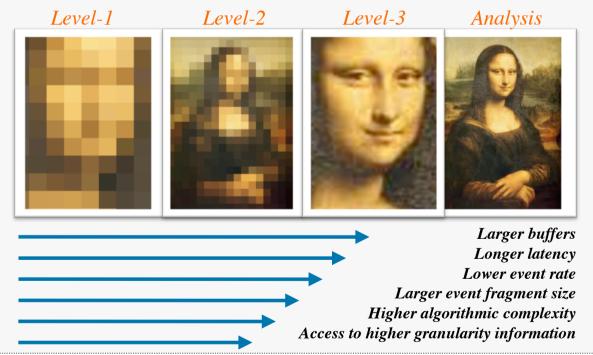

#### Extend the idea... multiple trigger levels

- Complexity of algorithms increases at each level

- Each stage further reduces the rate

- Later stages have longer latency

Dead-time is the sum of the trigger dead-time, summed over the trigger levels, and the readout dead-time

$$\tau_d^{multi} = \left(\sum_{i=1}^{N} R_{i-1} \cdot L_i\right) + R_N \cdot T_{LRO} \qquad \stackrel{\text{Pre-trigger}}{=0}$$

$R_i$  = Rate after the i-th level

$L_i$  = pre-trigger processing time for the i-th level

$T_{LRO}$  = Local readout time

Readout dead-time is driven by the final-level trigger rate

page 21 Manfred Jeitler

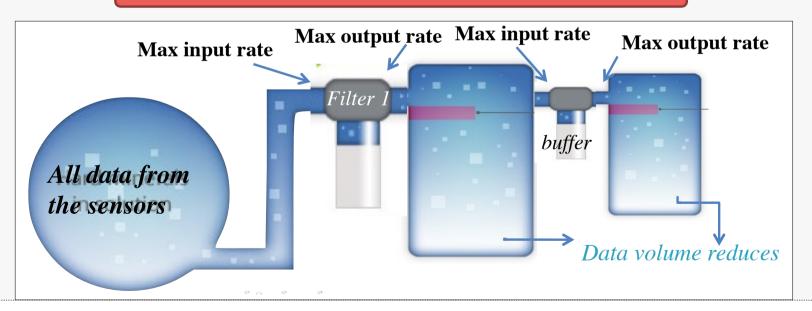

## **Buffering**

At each stage, data volume is reduced

- input rate constrains the filter processing time and the buffer size

- **output rate** limits the maximum latency allowed in the next step

No additional dead-time is introduced, unless buffers fill up (overflow)

page 22 Manfred Jeitler

- ▶ More and more complex algorithms are applied on lower and lower data rates

- First level with short latency, working at higher rates

- Higher levels apply further rejection, with longer latency (more complex algorithms)

page 23 Manfred Jeitler

page 24 Manfred Jeitler

page 25 Manfred Jeitler

page 26 Manfred Jeitler

## Multi-level trigger architecture

#### **Multi-level architecture**

- different levels of trigger, accessing different buffers

- ► The pre-trigger starts the digitisation

$$\tau_d^{multi} = \left(\sum_{i=1}^N R_{i-1} \cdot L_i\right) + R_N \cdot T_{LRO}$$

page 27 Manfred Jeitler

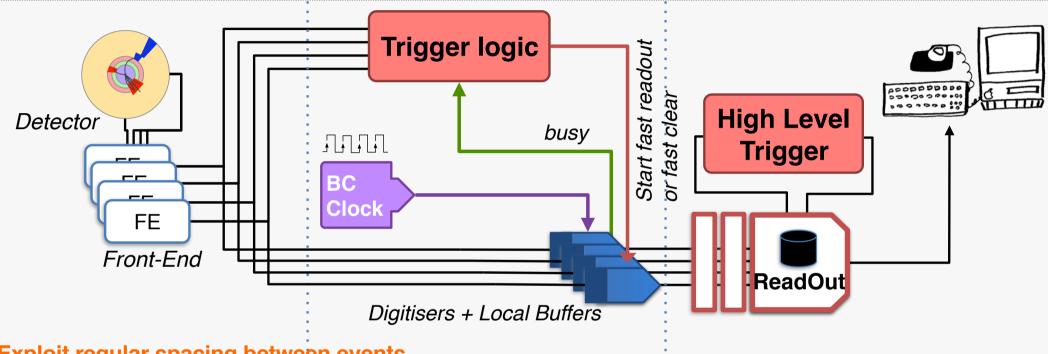

## Multi-level trigger architecture @ colliders

#### **Exploit regular spacing between events**

- BC clock starts digitisation No Pre-trigger dead time

- L1 trigger synchronous to BC clock.

- No Level-1 dead time if  $L_{I,1} < T_{BC}$

$$\tau_d^{multi} = \left(\sum_{i=1}^N R_{i-1} \cdot L_i\right) + R_N \cdot T_{LRO}$$

Manfred Jeitler page 28

## synchronous vs asynchronous trigger processing

- some calculations are harder, others easier

- example: there may be many or just a few tracks

- if you put data onto a computer: some events take longer to calculate than others

- overall computing resources will be optimally used

- so, is this fine?

page 29 Manfred Jeitler

## synchronous vs asynchronous trigger processing

- some calculations are harder, others easier

- example: there may be many or just a few tracks

- if you put data onto a computer: some events take longer to calculate than others

- overall computing resources will be optimally used

- so, is this fine? NO!

- danger! what if an event takes too long to process and is outside latency?

- "watchdog" events: the watchdog will bark if you take too long!

- just take all such events? But there may be far too many of them!

- just drop them? But these may be the most interesting events!

You might be killing all the "New Physics" events!

- just take the percentage of them that you can afford? Compromise,

but may be a nightmare to analyze!

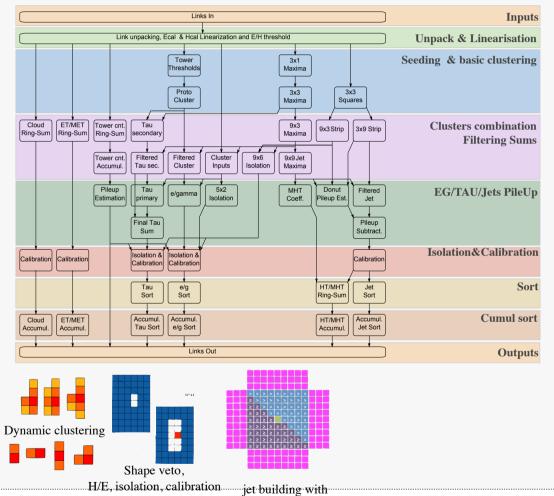

## The beauty of synchronous trigger processing

- guaranteed latency even the most complicated calculations fit into the available processing time

- you are just "wasting resources" in case of "simple" events

- like an assembly line: if a worker is fast, he will be idle part of the time and you lose salary money; if he is too slow, the whole production process will crash!

- enormous resources of present-day integrated circuits (ASICs and FPGAs) make this possible

- take care to choose correct programming style!

- no loops

- no conditional jumps

- make everything parallel as much as possible

page 31 Manfred Jeitler

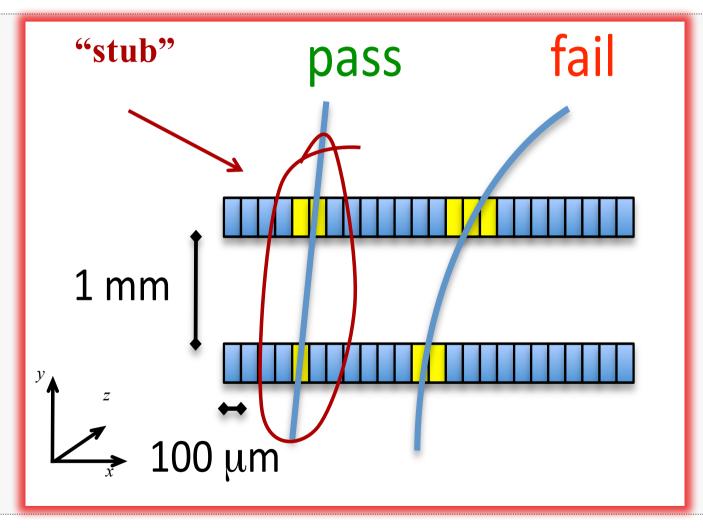

## Silicon tracker trigger: local intelligence

page 32

### Why a hardware trigger?

### Ideal: read out everything

- read out detector data for every "bunch crossing": every 25 ns, so

read out at 40 MHz

- reconstruct events using all detector data in computers

- discard data without interest before writing to tape

## ■ Why not work without hardware trigger?

- need very big computer farms (money problem)

- but also:

- have to get all data out from detector

- have to supply detector with much power

- not only money problem but resolution degradation due to amount of material in detector ("copper tracker")

## Level-1 trigger technologies

Pipelined trigger

Fast processors

Fast data transfer

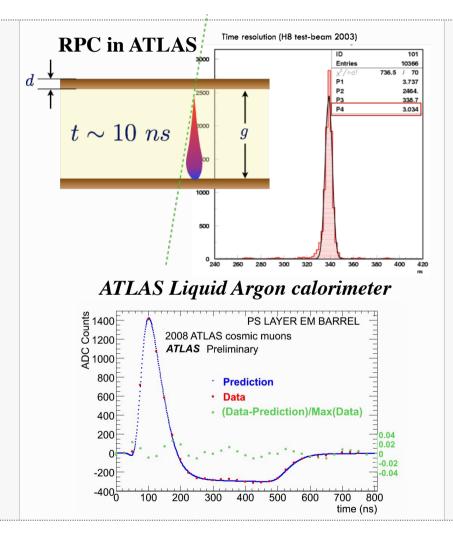

## How does the trigger receive input data?

Typically 'parasitic' on the main detector readout system

- Exception is when dedicated trigger detectors are used

- (e.g. ATLAS RPCs for muons)

- Organic scintillators

- ► Electromagnetic calorimeters

- ▶ Proportional chambers (short drift)

- ► Cathode readout detectors (RPC, TGC, CSC)

#### Typical requirement

- Fast signal: good time resolution and low jittering

- ▶ Shaping and on-board peak finding for slower detectors

- ► High efficiency

- ▶ (often) High rate capability

Need high-performance FE/trigger electronics for fast signal processing

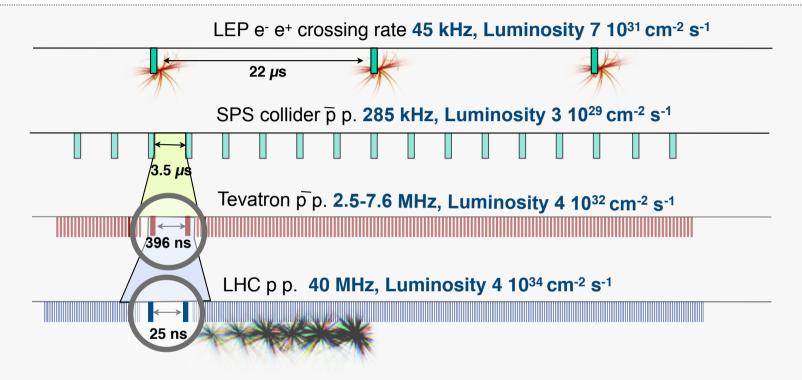

## Synchronous level-1 triggers @ colliders

$$R = \sigma \cdot \mathcal{L} = \mu \cdot f_{BX}$$

**@LEP**, BC interval 22  $\mu$ s: complex trigger processing was possible

- ▶ **In modern colliders**: required high luminosity is driven by high rate of BC

- BC spacing too short for final trigger decision!

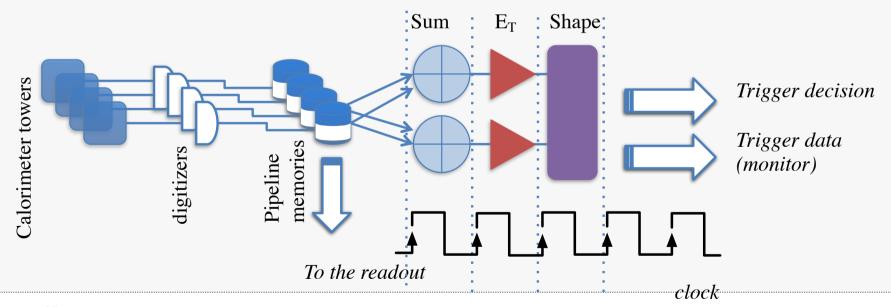

## Pipelining & buffers

With a synchronous system and large buffer pipelines, longer fixed trigger latency O(µs) becomes accessible

- Latency is the sum of each step processing and data transmission time Each trigger processor concurrently processes many events

- Divide processing in steps, each performed within one BC

page 37

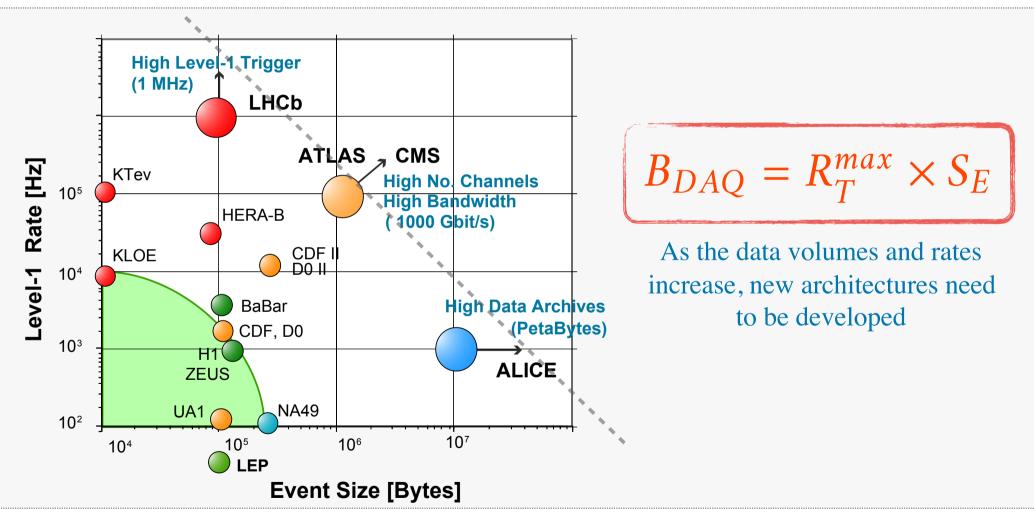

# Trigger and data acquisition trends

page 38

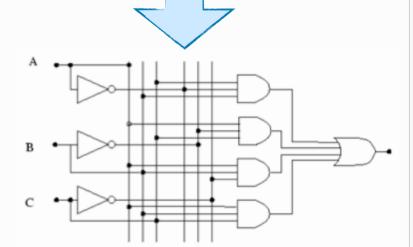

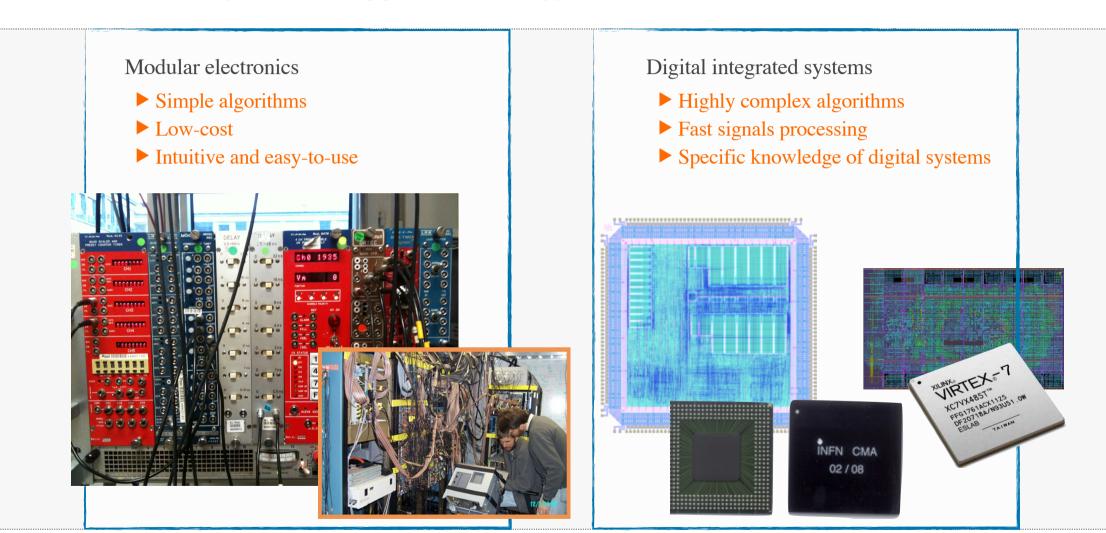

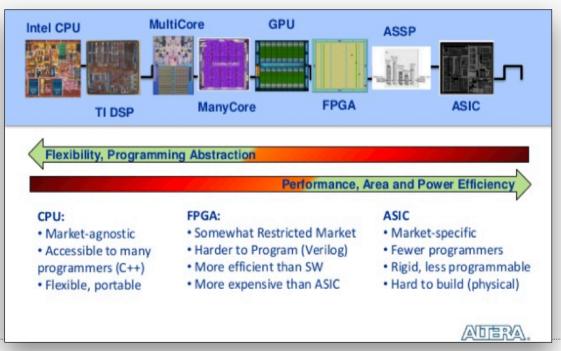

## Programmable devices

#### **Key requirements for high rate triggers**

- Fast processing

- ► Flexible/programmable algorithms

- ▶ Data compression and formatting

- ▶ Monitor and automatic fault detection

#### Digital integrated circuits (IC)

▶ Reliability, reduced power usage, reduced board size and better performance

#### Different families on the market:

- ► Microprocessors (CPU, GPU, ARM, DSP=digital signal processors)

- Available on the market or specific

- ► Programmable logic devices (FPGA, CAM)

- More operations/clock cycle, but costly and difficult software developing

## Choose your L1 trigger technology

page 40 Manfred Jeitler

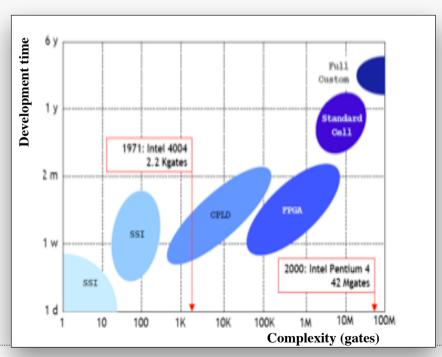

## ASICs vs FPGAs: unit cost vs flexibility

**Application-specific integrated circuits (ASICs)**: optimised for fast processing (Standard Cells, full custom)

► Intel processors, ~ GHz

Field-programmable gate arrays (FPGAs)

▶ Processors @ 100 MHz easily available on the market (1/10 speed of full custom ASICs)

page 41 Manfred Jeitler

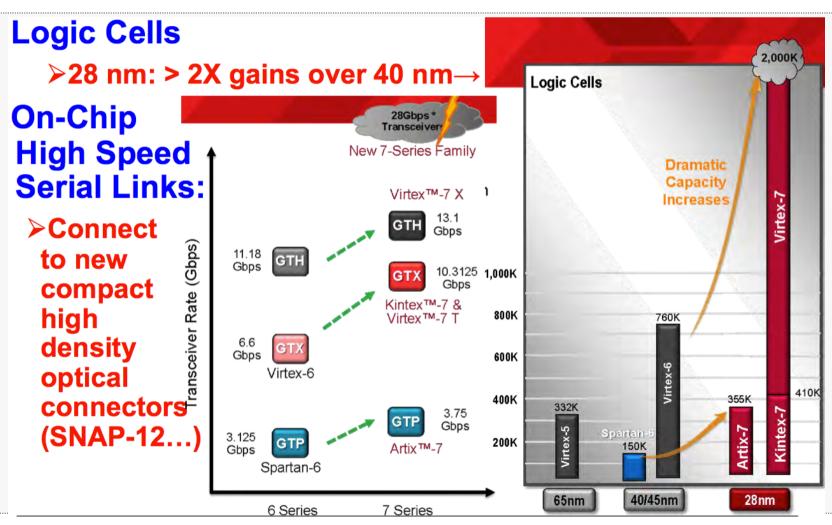

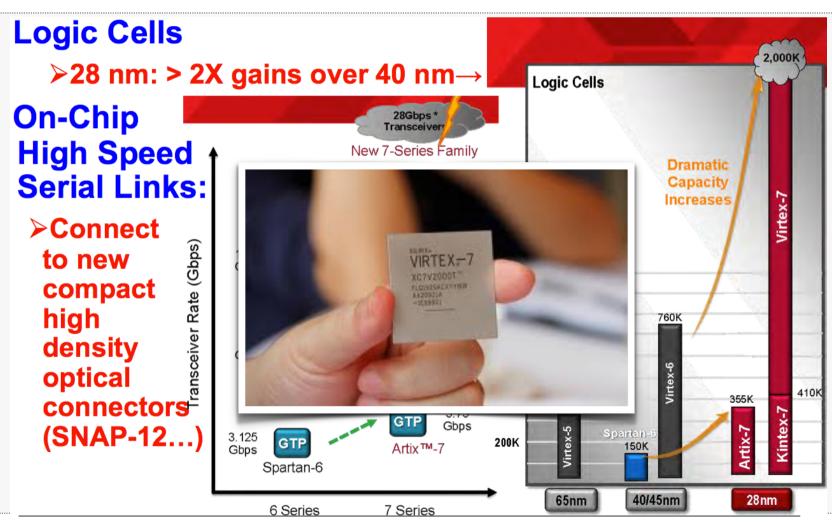

## Progress in FPGAs

page 42 Manfred Jeitler

## Progress in FPGAs

page 43 Manfred Jeitler

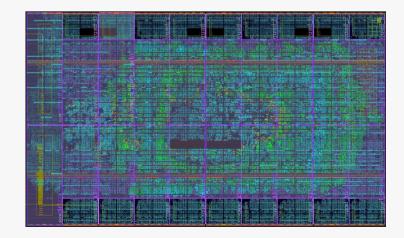

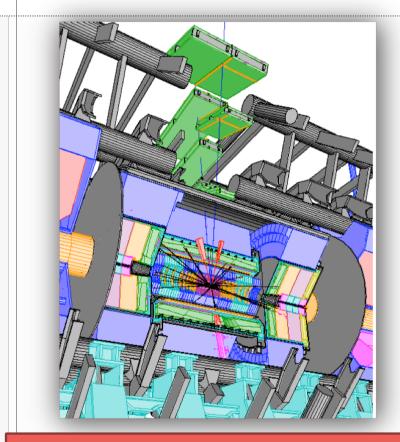

# Example: CMS Calorimeter trigger in FPGA

page 44 pileup subtraction

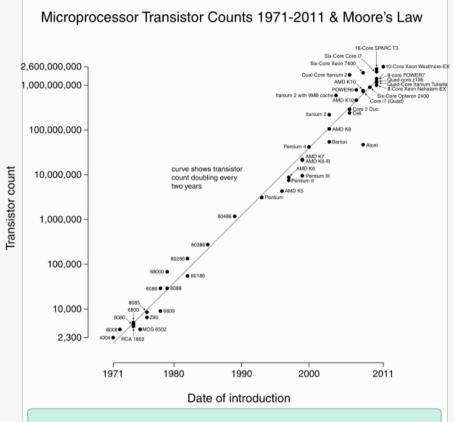

## Trends in processing technologies

Moore's Law: the number of transistors that can be placed inexpensively on an integrated circuit doubles approximately every two years (Wikipedia)

Demand of **higher complexity** → **higher chip density** → **smaller structure size** (for transistors and memory size):

▶ Nvidia **GPUs**: 3.5 B transistors

► Virtex-7 **FPGA**: 6.8 B transistors

▶ 14 nm CPUs/FPGAs in 2014

For FPGAs, smaller feature size means higher-speed and/or less power consumption

Multi-core evolution

► Accelerated processing GPU+CPU

Moore's law expected to hold at least until 2020, for FPGAs and co-processors as well

Market driven by cost effective components for Smartphones, Phablets, Tablets, Ultrabooks, Notebooks ....

## Data communication

Processing technology has now reached very high densities and speeds

High-speed serial links, electrical and optical

- Low cost and low-power LVDS links, @400 Mbit/s (up to 10 m)

- ▶ Optical GHz-links for longer distances (up to 100 m)

High density backplanes for data exchanges within crates

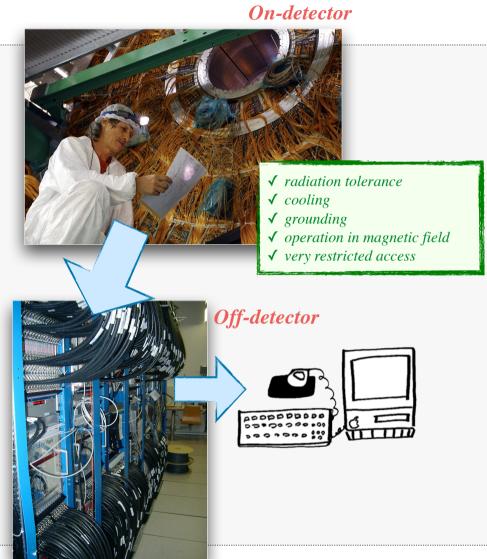

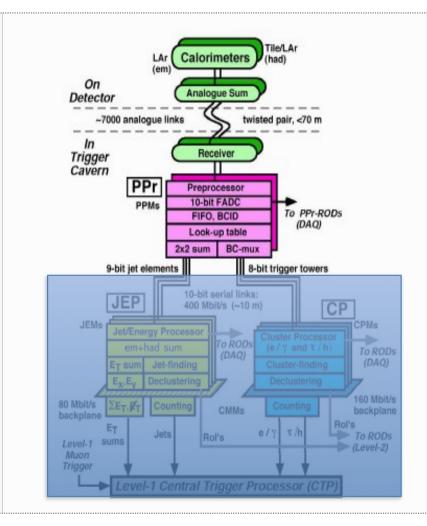

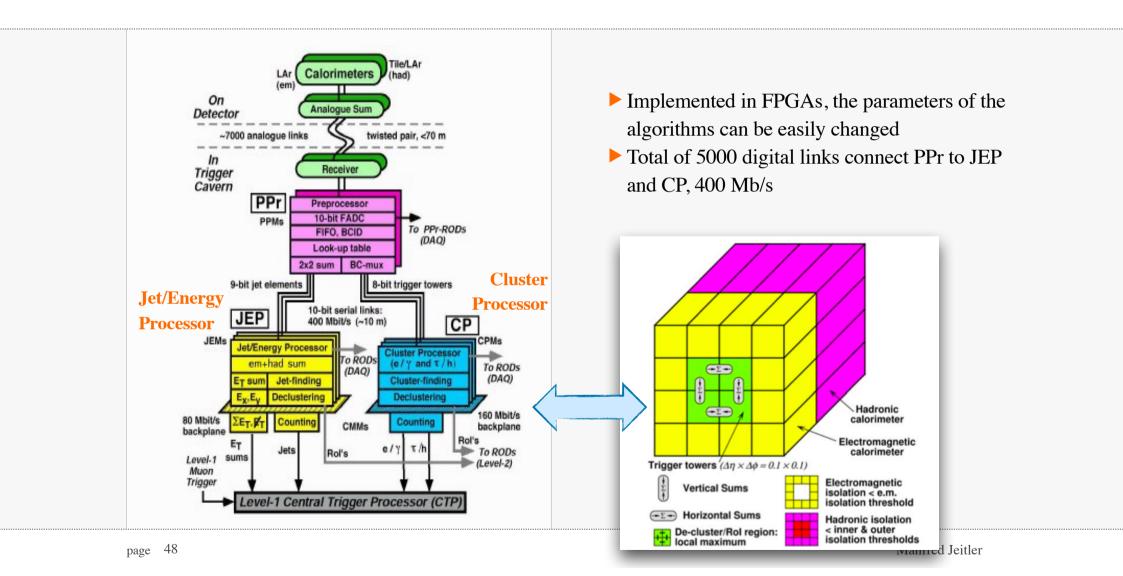

## Example: ATLAS calorimeter trigger

#### On-detector

Sum of analog signals from cells to form towers

#### Off-detector - L1 Trigger

- ▶ Pre-processor board

- ► ADCs with 10-bit resolution

- ► ASICs to perform the trigger algorithm

- Assign energy (ET) via Look-Up tables

- Apply threshold on ET

- Peak-finder algorithm to assign the BC

page 47 Manfred Jeitler

# Example: ATLAS calorimeter trigger

High-level trigger technologies

Can we use the offline algorithms online?

## High Level Trigger Architecture

|       | Levels | L1 rate                 | Event size | Readout bandwidth                  | HLT rate |

|-------|--------|-------------------------|------------|------------------------------------|----------|

| LEP   | 2/3    | 1 kHz                   | 100 kB     | a few 100 kB/s                     | ~5 Hz    |

| ATLAS | 2/3    | 100 kHz<br>(L2: 10 kHz) | 1.5 MB     | 30 GB/s (incremental Ev. Building) | ~1 kHz   |

| CMS   | 2      | 100 kHz                 | 1.5 MB     | 200 GB/s                           | ~1 kHz   |

**LEP**: 40 Mbyte/s VME bus sufficient for bandwidth needs

LHC: cutting-edge processors, high-speed network interfaces, high-speed optical links

#### Different approaches possible

- ▶ Network-based event building (LHC example: **CMS**)

- ► Seeded reconstruction (LHC example: **ATLAS**)

page 50 Manfred Jeitler

## HLT design principles

Offline reconstruction too slow to be used directly

• Takes >10s per event but HLT usually needs << 1s L1

Requires step-wise processing with early rejection

- 1. Fast reconstruction

- Trigger-specific or special configurations of offline algorithms

- L1-guided regional reconstruction

- 2. Precision reconstruction

- Offline (or very close to) algorithms

- Full detector data available

Stop processing as soon as one step fails

Event accepted if any of the trigger passes

## HLT design principles

#### Early rejection

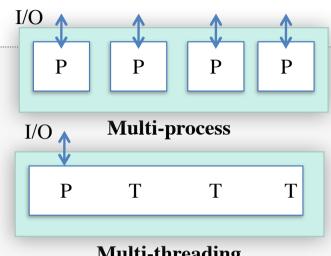

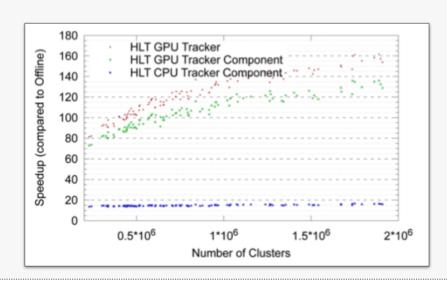

- ▶ Reduce data and resources (CPU, memory....) Event-level parallelism

- Process more events in parallel

- Multi-processing multi-threading

Algorithm-level parallelism

- ▶ multi-threading

- ► **GPUs** effective whenever large amount of data can be processed concurrently

Algorithms developed and optimized offline

Common HLT-reconstruction software framework reduces maintenace and increases reliability

**Multi-threading**

52 Manfred Jeitler page

# Now ... try it out in the lab!

# Now time to build your own trigger system!

- ► Trigger and DAQ systems use many new technologies —> contact with industry

- Microelectronics, networking, computing expertise are required to build an efficient trigger system

- But always in close contact with the physics measurements we want to study

- ▶ Here were presented some general problems, that will be discussed in detail during other lessons

Profit of this school to understand these connections!!

page 54 Manfred Jeitler

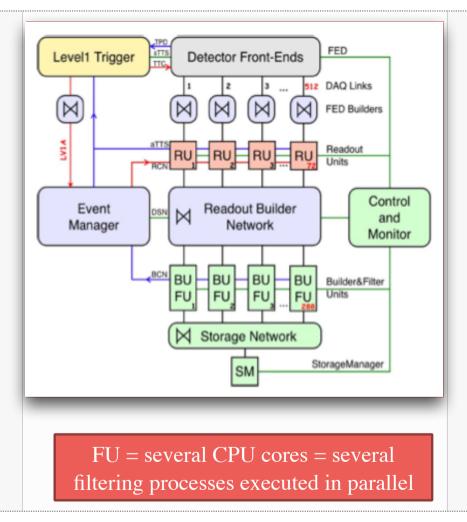

## **Network-based HLT: CMS**

Data from the readout system (RU) are transferred to the filters (FU) through a builder network

Each filter unit processes only a fraction of the events

page 55 Manfred Jeitler

## Seeded reconstruction HLT: ATLAS

Typically, there are less than 2 RoIs per event accepted by LVL1

Level-2 uses the information seeded by level-1 trigger

- ▶ Only the data coming from the region indicated by the level-1 is processed, called Region-of-Interest (RoI)

- The resulting total amount of RoI data is minimal: a few % of the Level-1 throughput

- Level-2 can use the full granularity information of only a part of the detector

No need for large bandwidth

Complicate mechanism to serve the data selectively to the L2 processing

page 56 Manfred Jeitler

## Multi-level triggers

#### Adopted in large experiments

- More and more complex algorithms are applied on lower and lower data rates

- First level with short latency, working at higher rates

- Higher levels apply further rejection, with longer latency (more complex algorithms)

Exp N. of Levels

ATLAS 3

CMS 2

LHCB 3

ALICE 4

Efficiency for the desired physics must be kept high at all levels, since rejected events are lost for ever