# RICH experience with MiniDAQ2

Antonino Sergi

### Outline

- Few (recycled) RICH slides:

- An overview of our application

- A couple of useful details

- Inter-system clock phases

- Annoying stuff

- WinCC amenities

- Our panels

- Packaging and repo

#### Overview

- Successful test beam, but:

- Phase alignment for the e-links can be annoying and unstable

- Clock generation could be improved

- Added input FIFO to delay 1 orbit (3564 clock cycles) to align data and trigger in the MiniDAQ1; just a patch: it will not be in the final design

- Plans for a final design, rad-hard:

- Move the orbit synchronization in the MiniDAQ (up to them) Done, but not fully tested

- Move most of the functionality in the TELL40 (Steve's suggestion) Done

- Reorganize the clock distribution:

- Drop the MMCM Done

- Try to make it synchronous with the 40MHz master clock Done

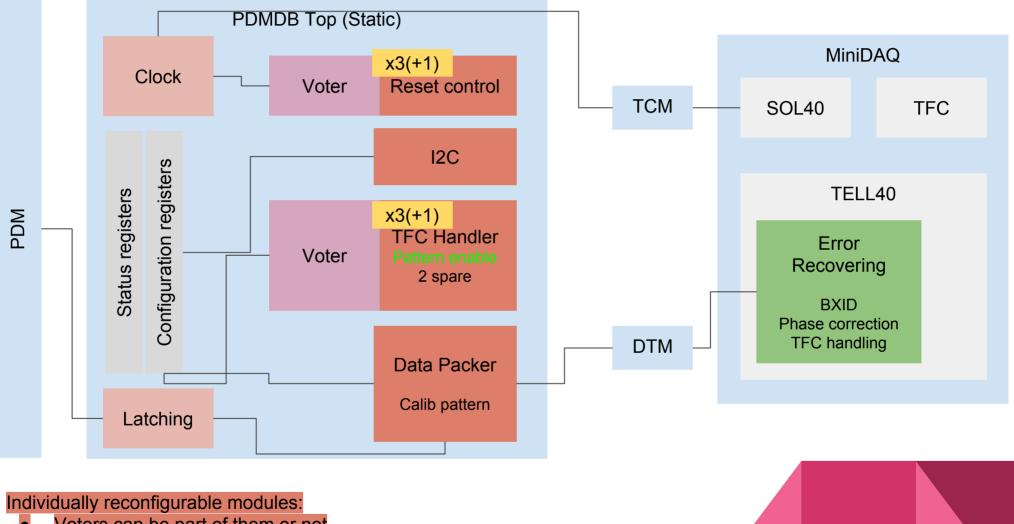

- Try to exploit Xilinx Partial Reconfiguration (PR) to minimize configuration time (15s/FPGA on MiniDAQ1 Done

- Introduce Triple Module Redundancy (TMR), integrated with PR

- Hierarchical design and implementation Done

- Thin down the firmware as much as possible Done

- Identify critical signals and apply triple voted logic Done

- Exploit TELL40 to react to failures Done, but not fully tester

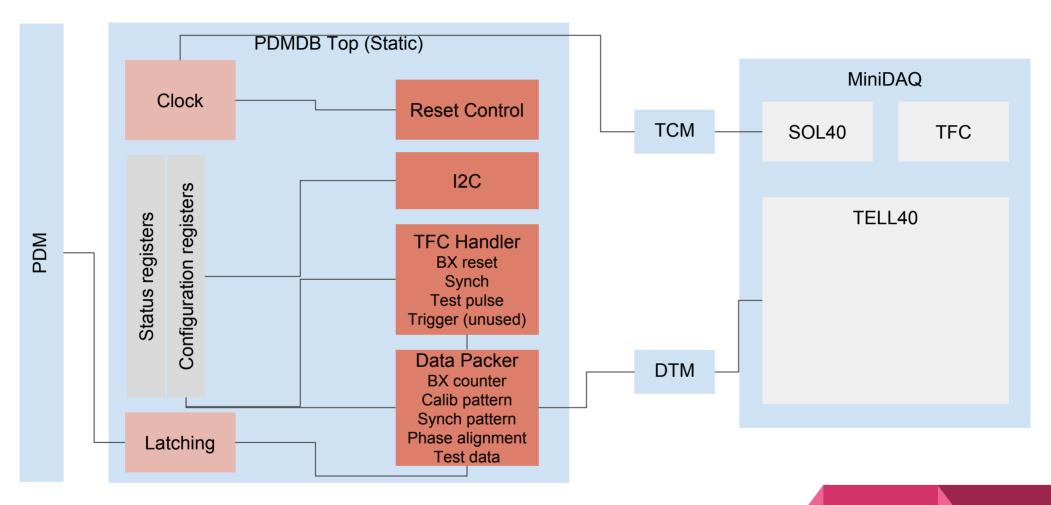

## Old architecture (full functionality)

Full functionality on detector:

- Reading TFC commands

- Flagging data

- Not rad-hard

#### Thinned architecture with PR and TMR

Voters can be part of them or not

#### Firmwares interaction and integration

- Master clock at 40MHz via GBTx

- Multiplied by GBTx to 160MHz (we use e-links at 320Mb/s DDR) and delivered to FPGAs

- We don't use any PLL to get 40MHz, but a clock buffer divider

- We don't use the clock lines from the e-links

- 40MHz is used to pack the data

- 160MHz is used to serialize data to send via e-links

- Individual serializers for e-links need to be aligned to the correct phase

- We managed to guarantee that the internal 40MHz is in phase with the master 40MHz

- Otherwise .... the misalignement of data changes at each startup

- We use the incoming e-links (for TFC) at 80Mb/s DDR

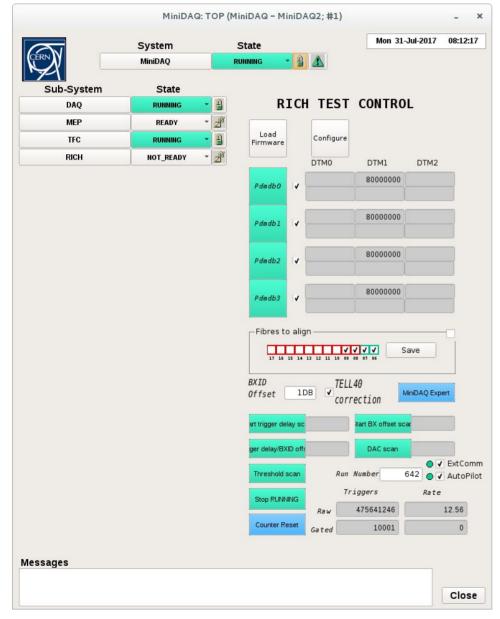

## WinCC panels

- What is provided is ok for quick tests, but starting to use it for measurements we needed more:

- run number

- step runs

- threshold scan

- DAC scan

- latency scans

- FE configuration:

- CLARO config

- loading firmware

- $\circ$  Recipes

- Mostly compatible with MiniDAQ1

## WinCC panels

|                                                                                | Pdmdb2Contr                            | rol (MiniDAQ - MiniDAQ2; #1)              |

|--------------------------------------------------------------------------------|----------------------------------------|-------------------------------------------|

| Pdmdb2<br>GBT 2 Initia                                                         | PDMDB (                                | Control                                   |

| Data Links                                                                     | GBT<br>files                           | FPGA0 Filename                            |

| DTM0                                                                           | Link Program Lin<br>0 Enabled          |                                           |

| DTM1 Program<br>GBT0<br>✓ Enabled                                              | Link Lin<br>8 Definition O             | Configuration Configuration Configuration |

| DTM2 <i>Enabled</i><br>Program<br>all<br>GBTs                                  | Link<br>0 Check<br>GBTs<br>V Fast Mode | Alian phones                              |

| CLARO<br>Claro Config Filena<br>/home/WinCC/ConfigFiles/c<br>Program<br>Claros |                                        | ed Set Claro Check Claros                 |

|                                                                                |                                        | Close                                     |

| PR_TMR       | * | PR_TMR Data_Packer_inst    | - |

|--------------|---|----------------------------|---|

| ed4bf14      | • | PR_TMR Reset_Control_inst0 | - |

| Apply        |   | PR_TMR Reset_Control_inst1 | • |

| Program FPGA |   | PR_TMR Reset_Control_inst2 |   |

|              |   | PR_TMR Reset_Control_inst3 |   |

|              |   | PR_TMR TFC_inst0           | - |

|              |   | PR_TMR TFC_inst1           | - |

|              |   | PR_TMR TFC_inst2           |   |

|              |   | PR_TMR TFC_inst3           | - |

|              |   | PR_TMR Voter_TFC_inst      | - |

|              |   | PR_TMR Vtr_Rst_Cntrl_inst  | - |

- SCA-I2C/SPI/JTAG are supported for a single instruction:

- we needed a bunch of panels and scripts

- A lot faster (x10) on MiniDAQ2

- CPU usage of GBtServ, WCCOAxx ~20%

## WinCC panels

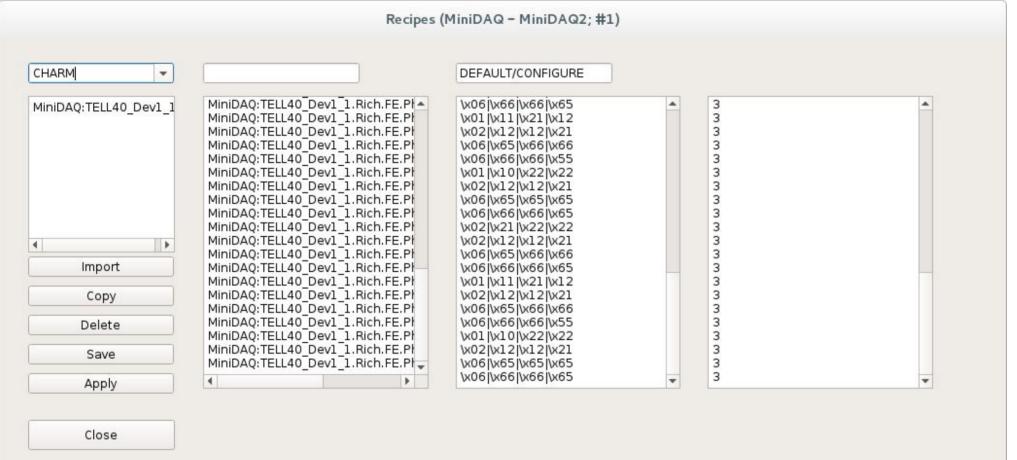

- Recipes are still a dev feature:

- only one recipe in the FW

- we supplemented it cheating

### Summary

- Detector side:

- BXID flagging: offsets and latency may not be obvious to find, especially with asynchronous triggers (test beam case)

- GBTx e-links phase alignment: it took some effort to make it reproducible after powercycles

- MiniDAQ2

- After patching the LLI clock tree it is usable (standalone)

- $\circ$   $\:$  Significant improvement on the SCA side in terms of speed of operation

- 1.1MB Xilinx (compressed) bitstream

- MiniDAQ1: 15(30) seconds with GbtServ off(on)

- MiniDAQ2: 2-3 seconds

- Useful in tests

- Very relevant in real applications

- The first one broke after a few weeks of usage (DC-DC converters), and it's being replaced

- WinCC

- It usually works (besides versioning stuff)

- To use it for test beams or measurements quite some work is required

- Not very multi-developer friendly yet (subdetector components)