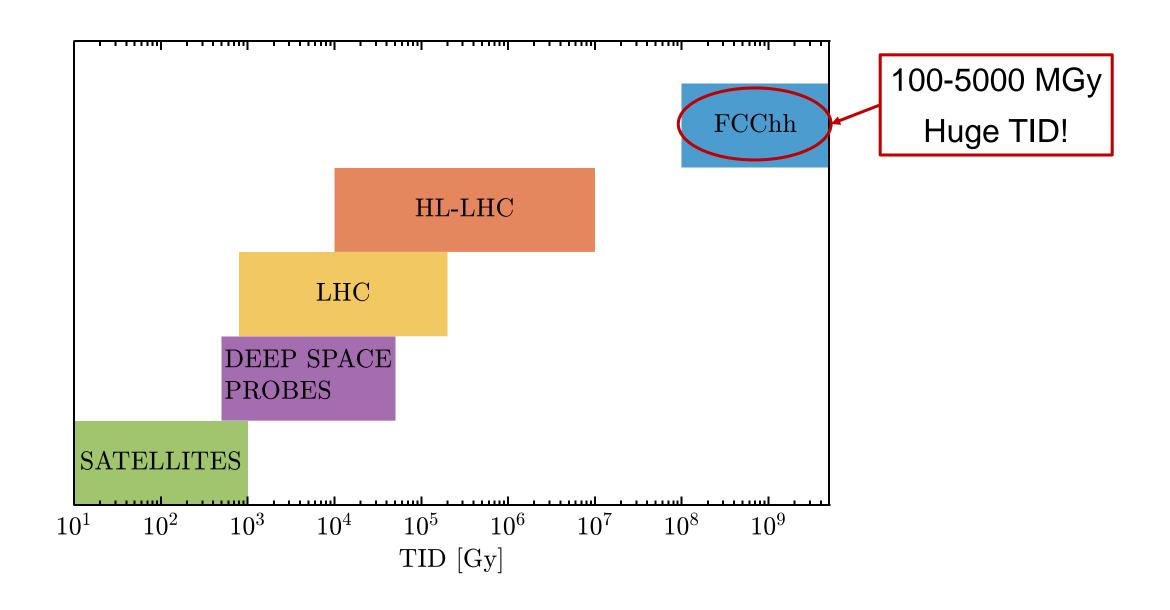

## FCC RADIATION ENVIRONMENT: AN UNPRECEDENTED CHALLENGE FOR MOS TRANSISTORS

GIULIO BORGHELLO giulio.borghello@cern.ch

| RADIATION EFFECTS |       | IONIZING                     | NON-IONIZING        |  |  |

|-------------------|-------|------------------------------|---------------------|--|--|

| CUMULATIVE        |       | TOTAL IONIZING DOSE<br>(TID) | DISPLACEMENT DAMAGE |  |  |

| STOCH             | ASTIC | SINGLE EVENT EFFECTS         |                     |  |  |

Cumulative: The higher the radiation level, the larger the damage.

## Highest radiation levels:

**DETECTORS**

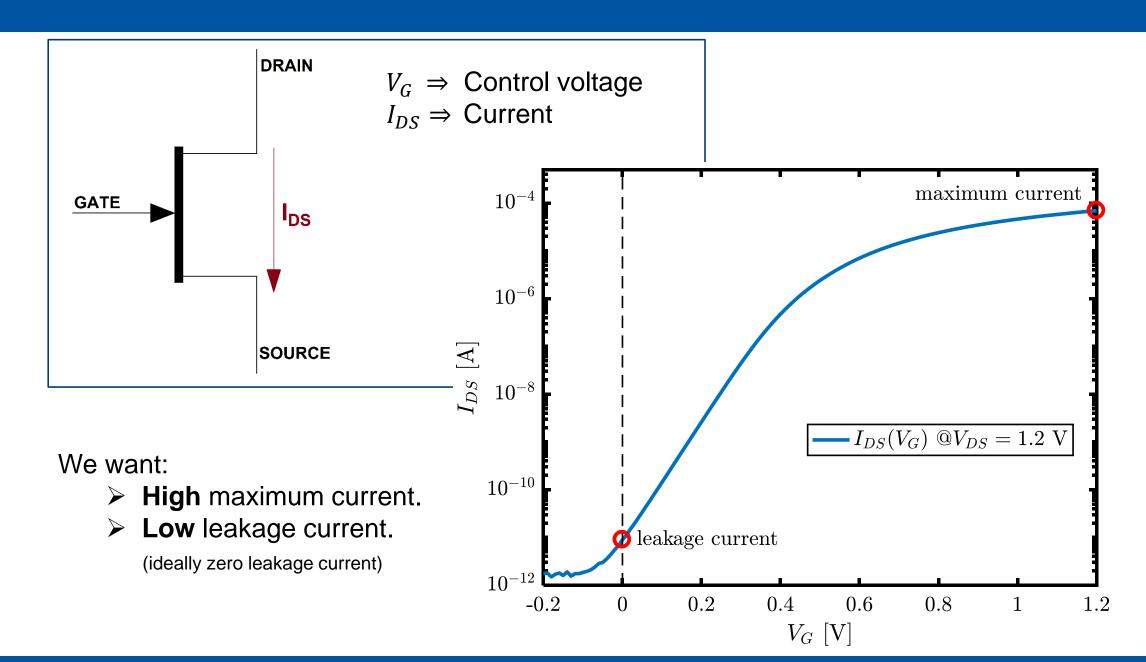

How MOS transistors respond to TID?

Why should we care about it?

| Processor                                             | N. Transistor  | Year | Designer      |  |

|-------------------------------------------------------|----------------|------|---------------|--|

| Apple A11 Bionic<br>(hexa-core ARM64<br>"mobile SoC") | 4,300,000,000  | 2017 | Apple         |  |

| 8-core Ryzen                                          | 4,800,000,000  | 2017 | AMD           |  |

| IBM z14                                               | 6,100,000,000  | 2017 | IBM           |  |

| Xbox One X (Project Scorpio) main SoC                 | 7,000,000,000  | 2017 | Microsoft/AMD |  |

| Centriq 2400                                          | 18,000,000,000 | 2017 | Qualcomm      |  |

Source: https://en.wikipedia.org/wiki/Transistor\_count

## Commercial processors

Example:

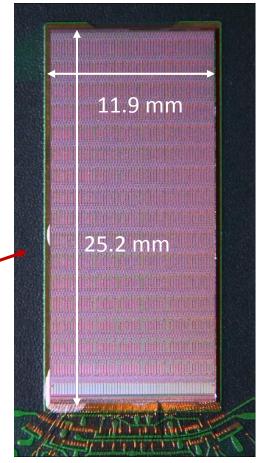

**MPA** (Macro Pixel ASIC)

For **CMS** outer tracker:

~1.5M of transistors

# Billions of transistors for each experiment!

Courtesy of Davide Ceresa, CERN (EP-ESE-ME section)

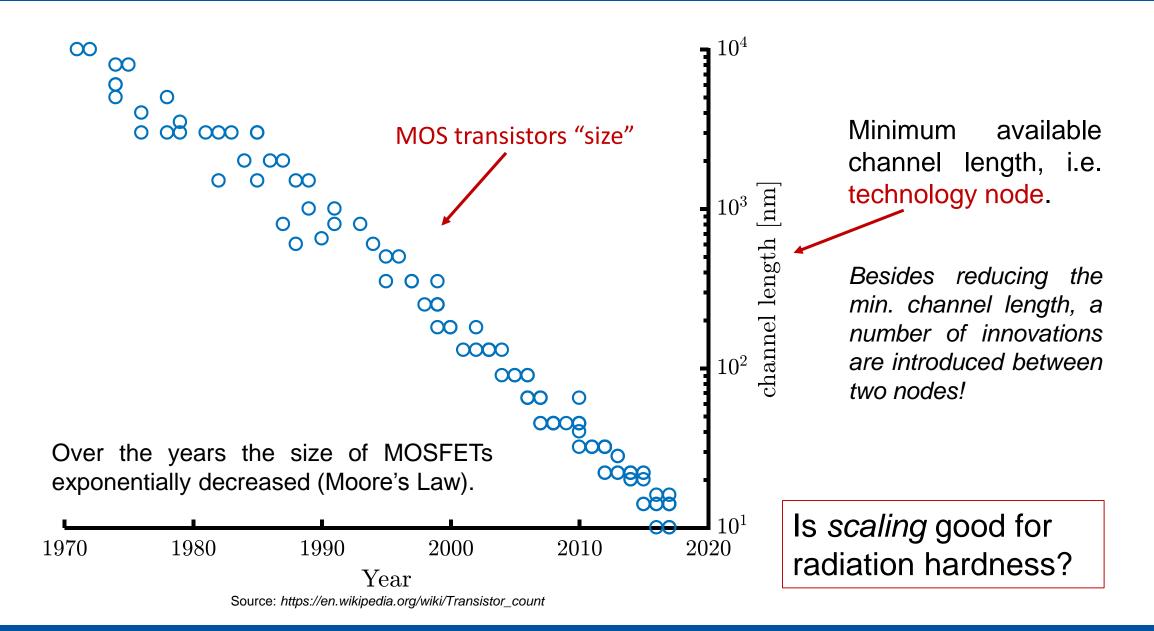

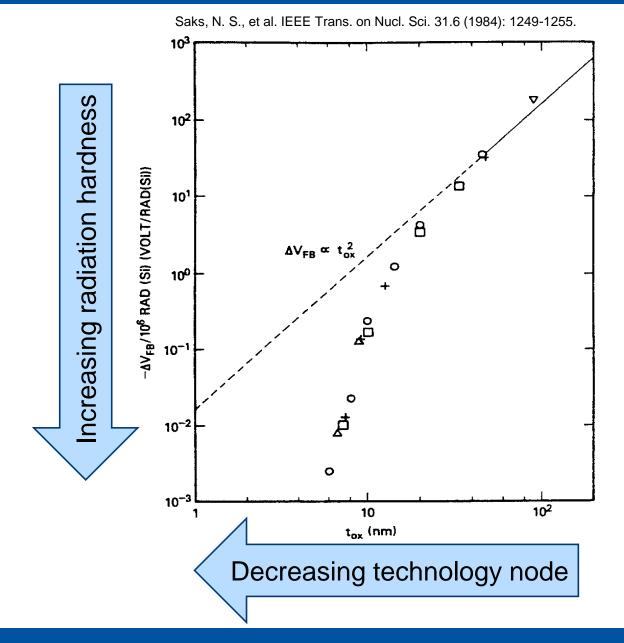

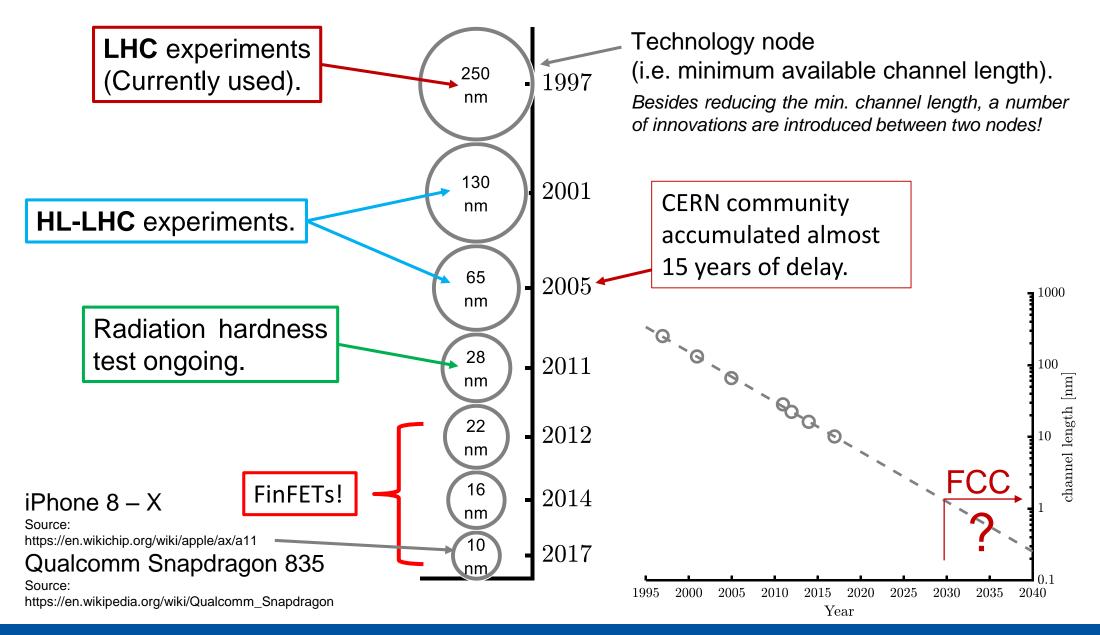

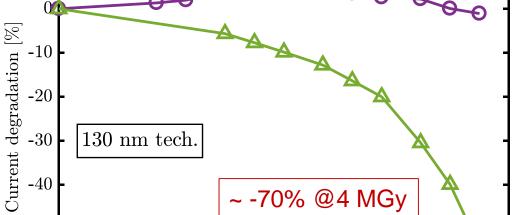

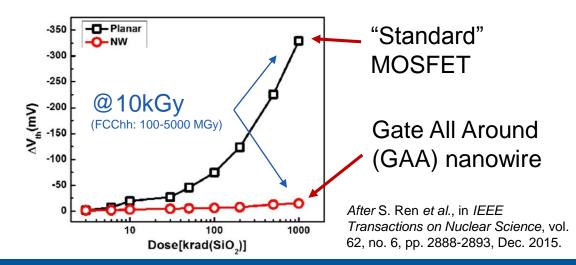

**Some aspects** of MOS radiation response improve with scaling.

130 nm tech

(FCChh: 100-5000 MGy)

$10^{5}$

$10^{6}$

10

Max.

-50

PreRad

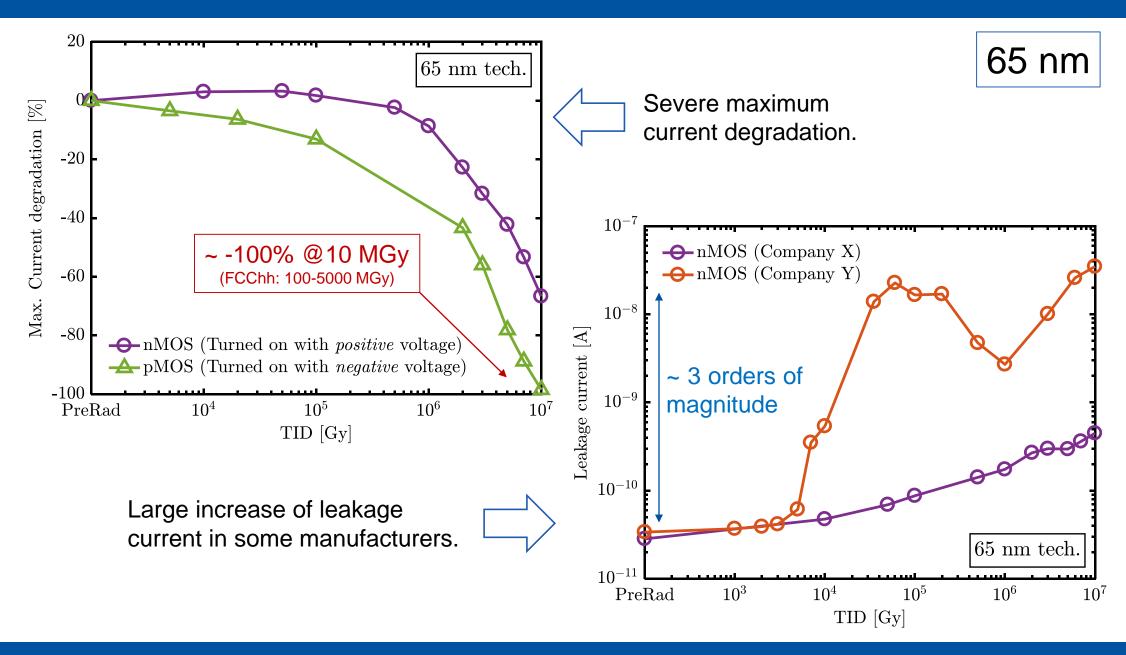

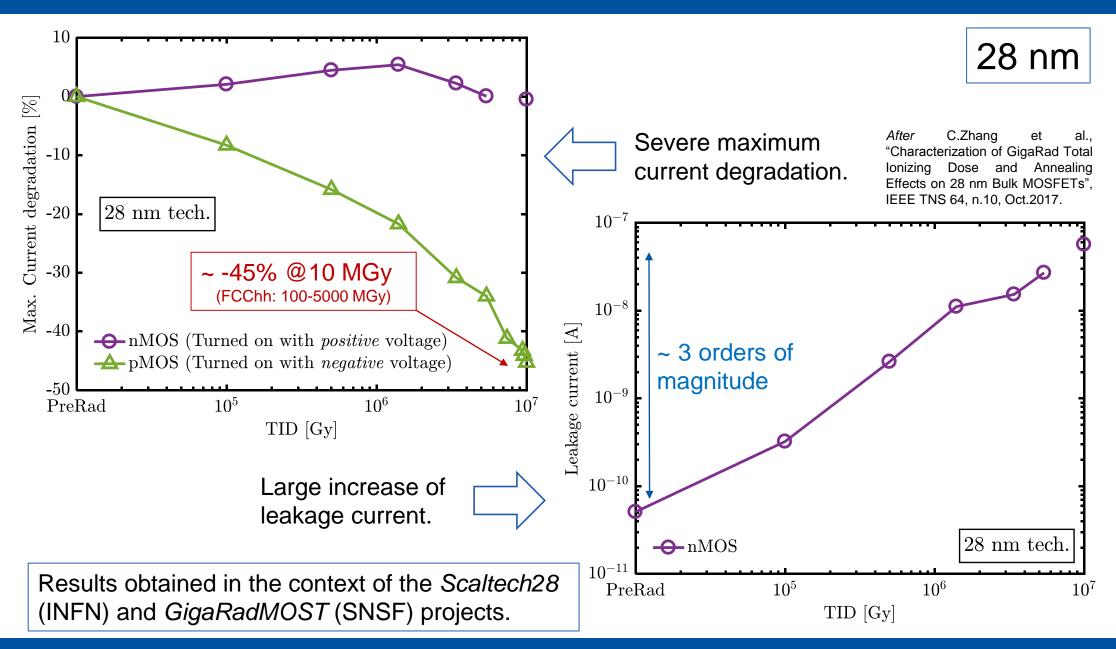

Severe maximum current degradation for pMOS.

$10^{-5}$

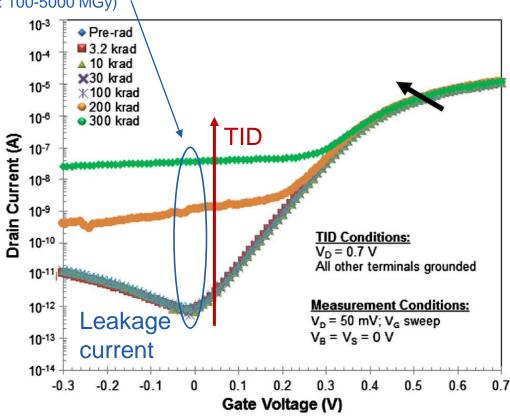

Large increase of leakage current.

TID [Gy]

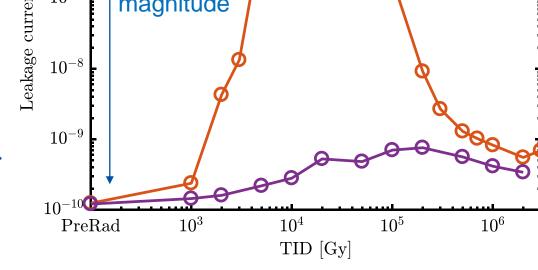

• Peak around 10~30 kGy.

$10^{3}$

Extremely process-dependent.

-nMOS (Turned on with *positive* voltage)

→ pMOS (Turned on with negative voltage)

$10^{4}$

#### Below 28 nm:

#### **Planar MOSFETs** → **FinFETs**

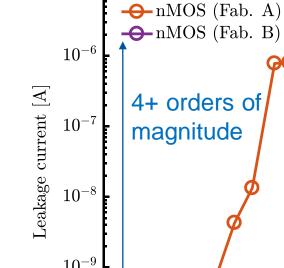

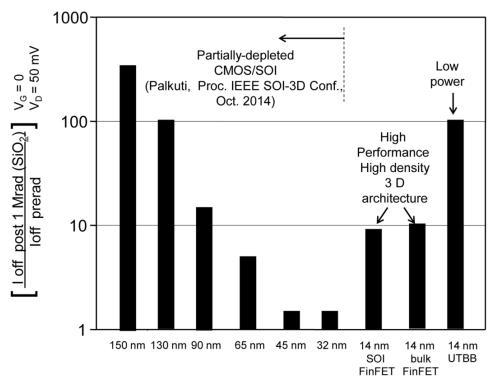

### FinFETs ≤22 nm

4+ orders of magnitude @3 kGy (FCChh: 100-5000 MGy)

#### Large increase of leakage current!

After I.Chatterjee et al., "Bias Dependence of Total-Dose Effects in Bulk FinFETs", IEEE TNS 60, n.6, 2013

#### **Technology Node**

After H. Hughes et al., "Total Ionizing Dose Radiation Effects on 14 nm FinFET and SOI UTBB Technologies," 2015 IEEE Radiation Effects Data Workshop (REDW), Boston, MA, 2015, pp. 1-6.

## Future technologies (likable)

Source: International roadmap for devices and systems - 2016 edition - more moore white paper "https://irds.ieee.org/images/files/pdf/2016\_MM.pdf"

| YEAR OF PRODUCTION                           | 2015            | 2017            | 2019             | 2021                   | 2024             | 2027          | 2030          |

|----------------------------------------------|-----------------|-----------------|------------------|------------------------|------------------|---------------|---------------|

| Logic device technology naming               | P70M56          | P54M36          | P42M24           | P32M20                 | P24M12G1         | P24M12G2      | P24M12G3      |

| Logic industry "Node Range" Labeling<br>(nm) | "16/14"         | "11/10"         | "8/7"            | "6/5"                  | "4/3"            | "3/2.5"       | "2/1.5"       |

| Logic device structure options               | finFET<br>FDSOI | finFET<br>FDSOI | finFET<br>LGAA   | finfet<br>Lgaa<br>Vgaa | VGAA,<br>M3D     | VGAA, M3D     | VGAA, M3D     |

|                                              |                 |                 |                  |                        |                  |               |               |

|                                              | FINFEY          | FINFET          | Lateral Nanowire | Vertical Nanowire      | Wortkal Nanowine | Monolatric 3D | Monolatric 3D |

New technologies could be more rad-hard, but:

- Very small literature on TID effects.

- We are very far from commercial products.

## Expected TID in FCChh:

100 – 5000 MGy

X-ray irradiation facility at CERN can provide (MAX):

~ 0.1 MGy/h

To perform TID experiments:

~ 40 days – 5+ years

## Displacement Damage

MOSFET are usually not sensitive to DD.

However fluence in the FCChh can be two order of magnitude higher than in the HL-LHC!

To be tested!

## CONCLUSIONS

- ☐ TID expected in FCChh is extremely large.

- TID strongly affects MOS transistors performance.

- Current technology cannot withstand the FCChh levels of TID.

- Radiation response extremely technology dependent.

- Almost impossible to foreseen the behaviour of future technologies.

- Need to be tested!

- Ways to perform high-TID experiments within a reasonable time have to be found.

- □ DD may lead to additional failure mechanisms.

- Need to be tested!

- □ Radiation-induced degradation of MOS transistors performance may represent a limit to the physics exploitation of the FCC.